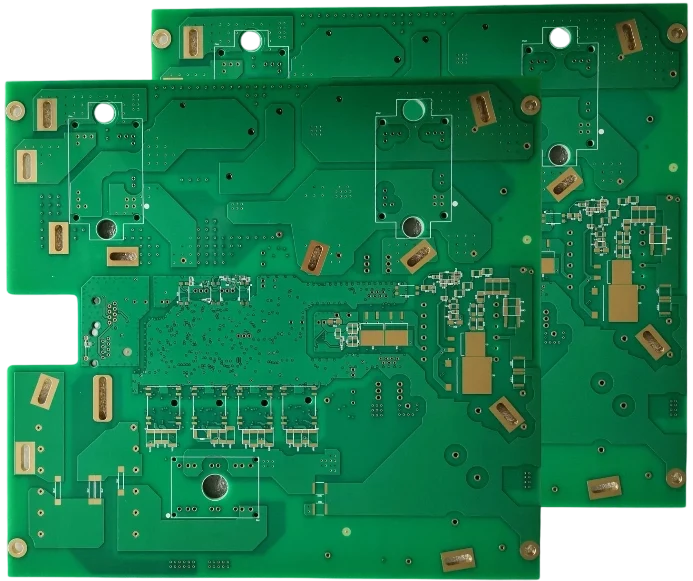

Coordination CAM haute vitesse et SI

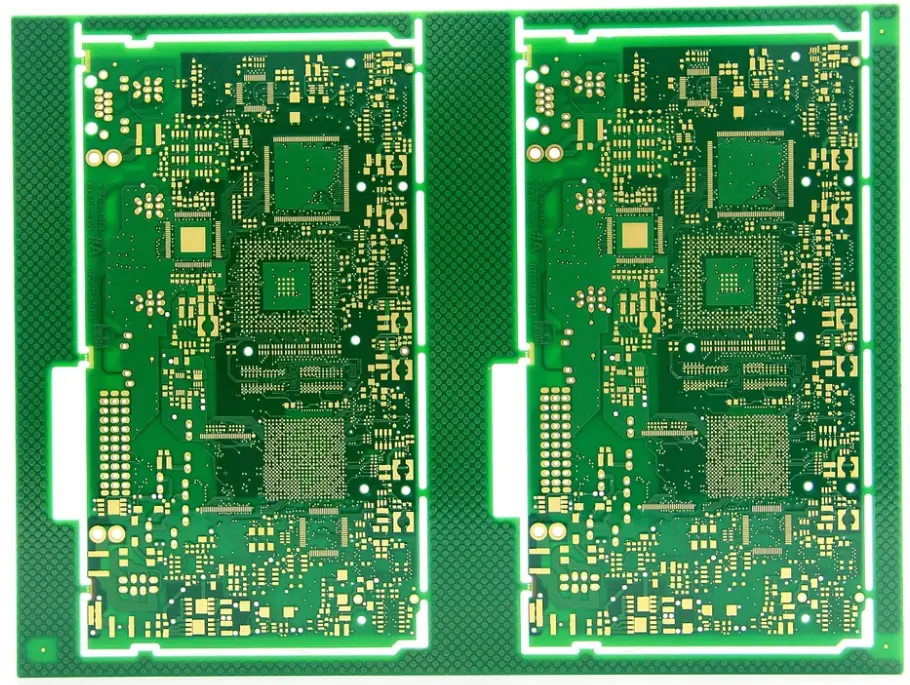

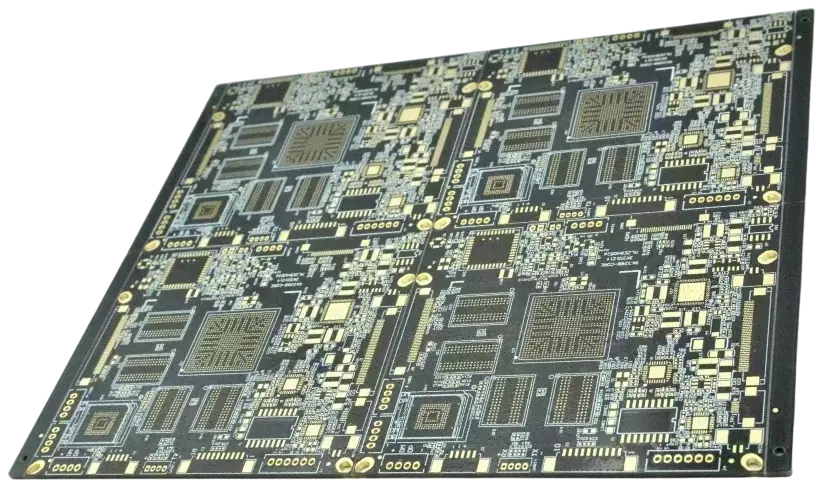

Les ingénieurs CAM traduisent les contraintes SI en fichiers de fabrication, définissant les empilements, les cartes de perçage, les coupons d'impédance et les coordonnées de défonçage.

- Documentez les objectifs diélectriques, la rugosité du cuivre et la teneur en résine par couche.

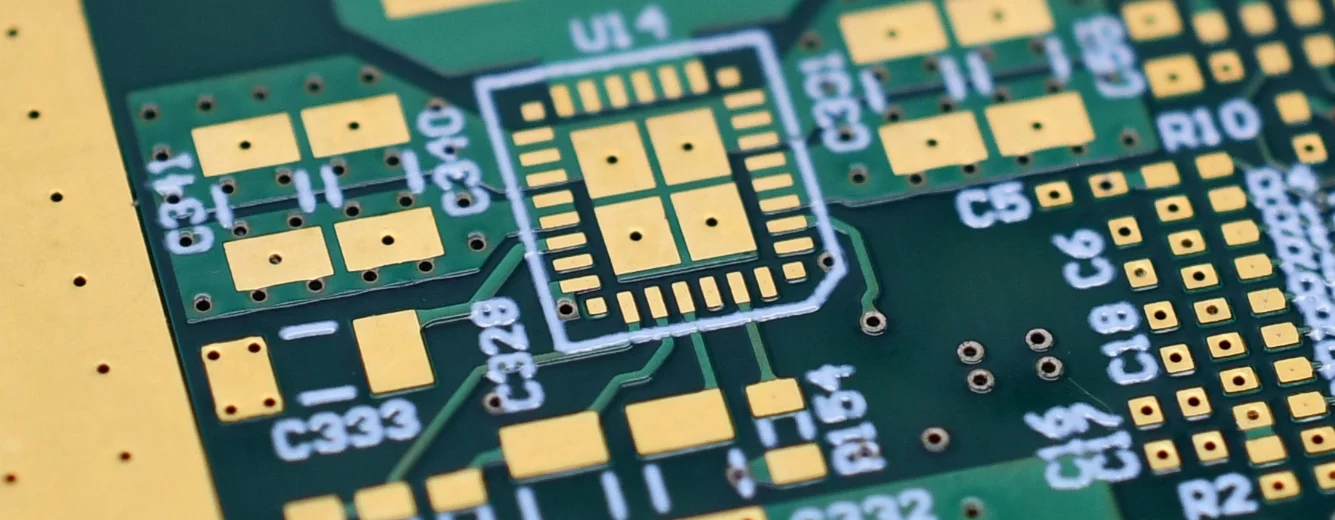

- Définissez les coupons d'impédance, les géométries des paires différentielles et les empilements de tolérance.

- Planifiez les profondeurs de défonçage, les remplissages VIPPO et les vias de stitching des plans de référence.

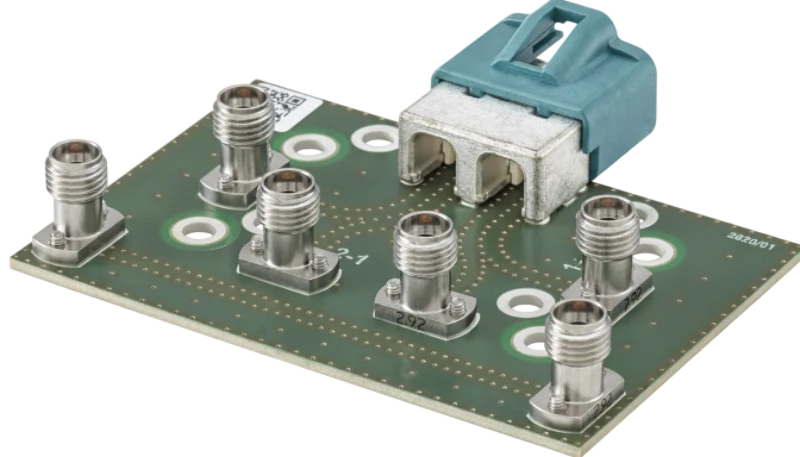

- Coordonnez les empreintes des connecteurs press-fit et les exigences de tear-drop.

- Simulez ou validez les transitions de via avec les sorties des outils SI.

- Fournissez des instructions de manipulation et de cuisson pour les matériaux à faible perte.

- Publiez des notes de fabrication détaillant les substitutions autorisées et les points de contrôle qualité.