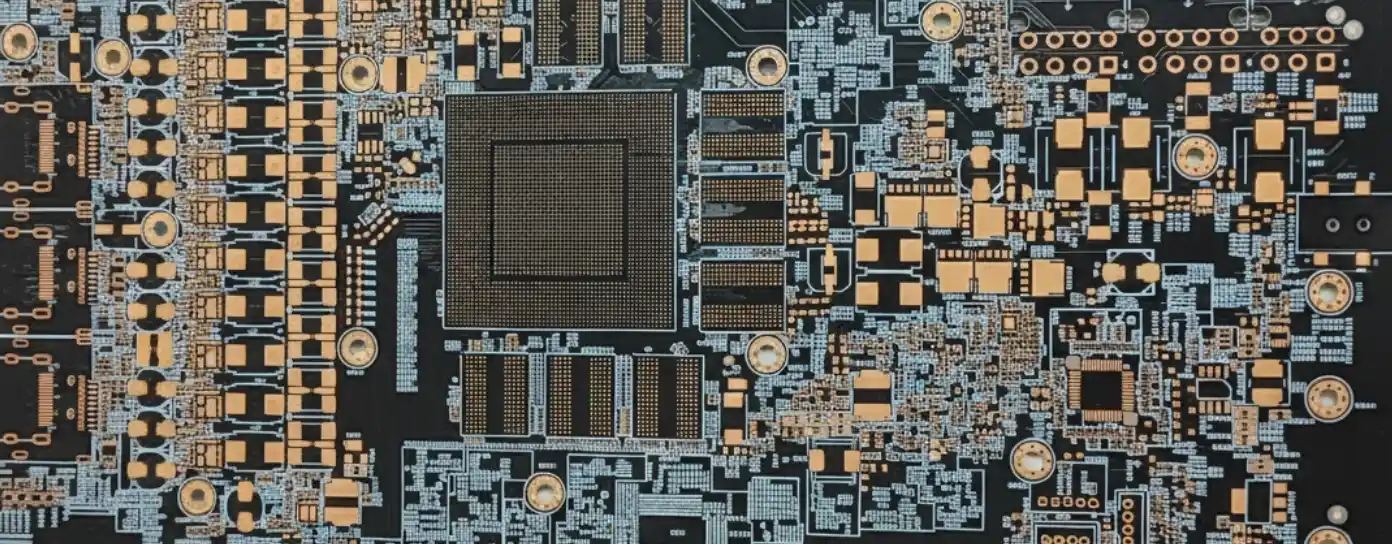

Workflow d’ingénierie CAM — convertir les données de conception en process HDI fabricable

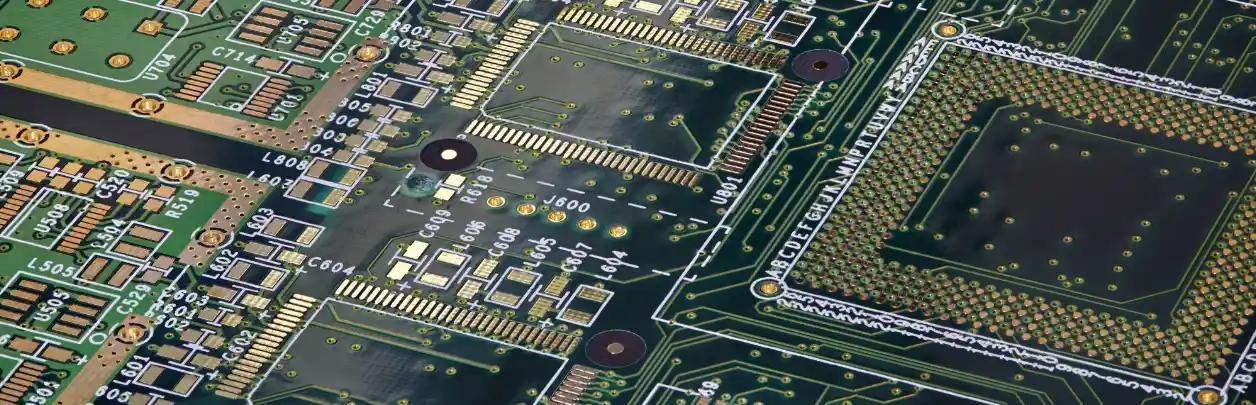

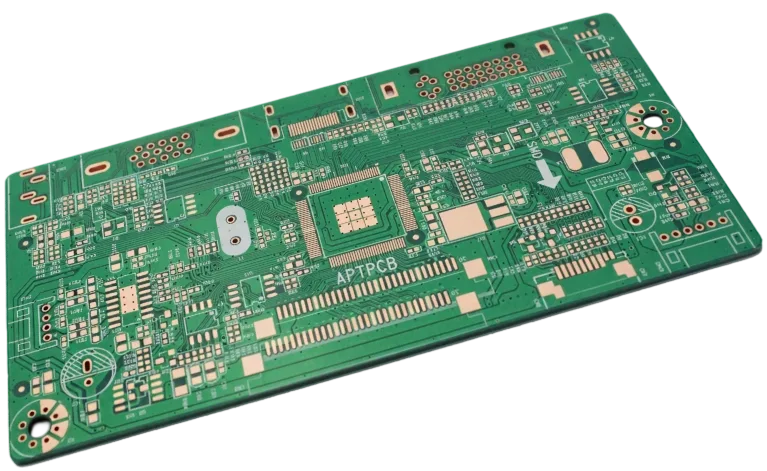

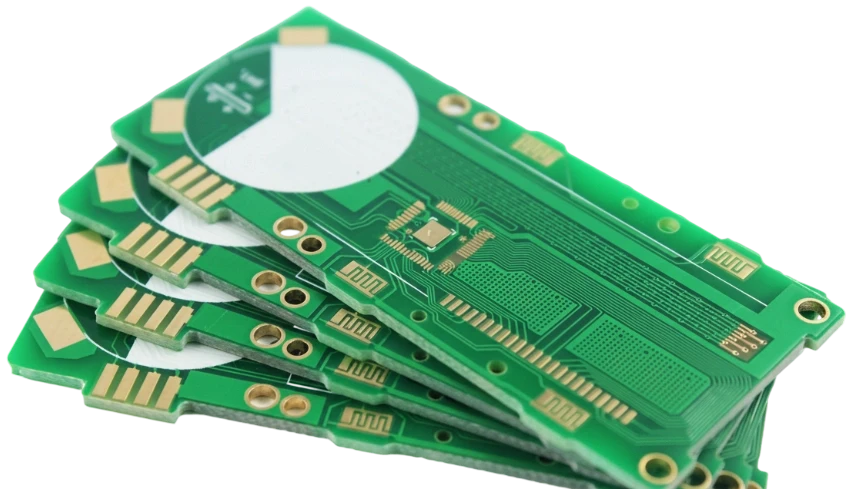

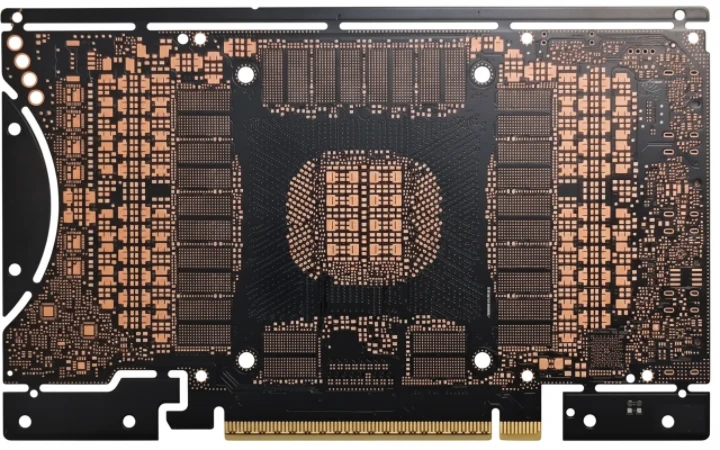

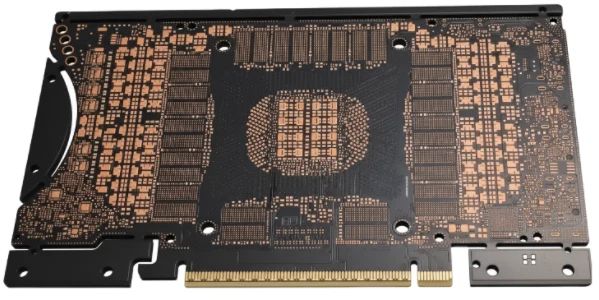

Dans le process de fabrication HDI, la première phase essentielle est menée par les ingénieurs CAM, qui traduisent l’intention de conception en un plan de production précis et fabricable. Après réception des données Gerber ou ODB++, ils vérifient la structure d’empilage, les configurations microvia et les exigences d’impédance. Via analyse DFM, programmation de perçage et préparation des notes de fabrication, les ingénieurs CAM s’assurent que chaque caractéristique du design est compatible avec les capacités de production.

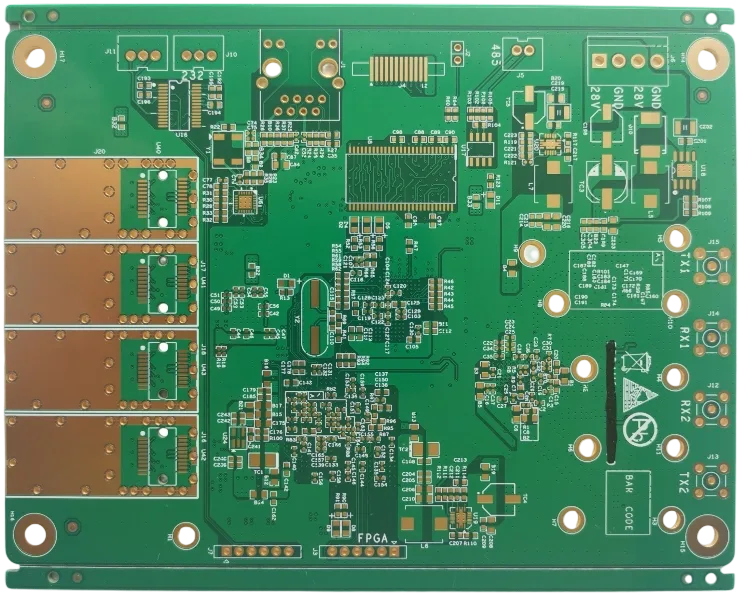

- Confirmer la structure d’empilage et la configuration des couches SBU.

- Définir le type de microvia (staggered/stacked), VIPPO et les règles via-in-pad.

- Réaliser une analyse DFM (largeur/espacement, annular ring, dégagement via-piste).

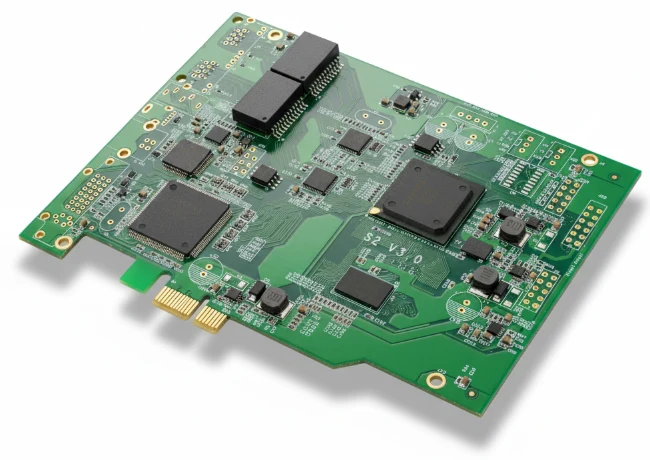

- Définir les programmes de perçage laser et les profils de remplissage cuivre.

- Planifier les coupons d’impédance et la stratégie de mesure TDR.

- Valider le choix matériaux (FR-4/low-loss) et la compatibilité Tg/CTE.

- Collaborer avec l’ingénierie de production pour revue fabricabilité et validation du flux process avant release.