Une carte d’équilibrage BMS bien conçue conditionne directement la longévité et la sécurité d’un bloc batterie multi‑cellules. Sans égalisation fiable, un bloc Li‑ion ou LiFePO4 monté en série finit par dériver : une ou plusieurs cellules atteignent trop tôt les limites de tension, la capacité utile se réduit, et le risque de défaut (jusqu’à l’emballement thermique) augmente.

Chez APTPCB (usine PCB APTPCB), nous voyons régulièrement des conceptions BMS dont les problèmes proviennent de deux points : la précision de mesure (chutes IR, couplages, mauvaise masse) et la gestion thermique (résistances de décharge, MOSFETs, cuivre insuffisant). Ce guide rassemble des règles concrètes, une liste de contrôle d’exécution et des scénarios de dépannage pour livrer une carte d’équilibrage BMS robuste et industrialisable (DFM).

Conception de carte d’équilibrage BMS : réponse rapide (30 secondes)

Si vous devez aller à l’essentiel, appliquez immédiatement ces principes :

- Dimensionner le courant d’équilibrage : en passif, viser au moins ~1 % de la capacité cellule (taux C) pour corriger la dérive sur la durée (ex. 50 mA–100 mA pour petits packs, ≥1 A pour gros stockages).

- Traiter la thermique en priorité : l’équilibrage passif transforme l’énergie en chaleur. Utilisez plans cuivre, vias thermiques et, si nécessaire, PCB à cuivre épais pour éloigner les points chauds des cellules.

- Mesurer en Kelvin : routez les lignes de mesure de tension séparément des chemins de puissance, sinon la chute IR fausse la mesure et déclenche l’algorithme au mauvais moment.

- Soigner la chaîne référence/ADC : une précision meilleure que 0,1 % est un objectif réaliste sur de nombreux designs ; ~10 mV d’erreur peut amputer la capacité utile de plusieurs pourcents.

- Prévoir une protection à sécurité intrinsèque : ajoutez des protections redondantes (surtension/surchauffe) qui fonctionnent même si le micrologiciel du microcontrôleur est en défaut.

Quand la conception d’une carte d’équilibrage BMS s’applique (et quand elle ne s’applique pas)

Le bon niveau d’effort dépend du bloc batterie et du produit : parfois l’équilibrage est indispensable, parfois c’est un choix de coût.

Quand appliquer une conception rigoureuse :

- Packs en série (≥2S) : dès 2S, la dérive de tension entre cellules est inévitable à terme.

- Exigence de forte durée de vie : VE, ESS, robotique/industrie : quand on vise 1000+ cycles, l’équilibrage fait partie de la stratégie de durée de vie.

- Cellules de lots différents : si la chaîne d’approvisionnement force des mélanges (à éviter), l’équilibrage actif aide à compenser les écarts d’impédance.

- Charge rapide : les charges à fort C accentuent les écarts ; sans équilibrage robuste, une cellule atteint trop tôt la coupure surtension.

Quand cela peut être inutile (ou réduit) :

- 1S : pas d’équilibrage inter‑cellules, uniquement protection.

- Produits ultra‑économiques et courte durée : certains designs acceptent une dérive et une fin de vie plus rapide pour réduire la BOM.

- Plomb‑acide (parfois) : une auto‑égalisation peut exister, mais l’électronique de contrôle reste préférable sur de grosses banques.

- Piles primaires : pas d’équilibrage sur des chimies non rechargeables.

Règles et spécifications de conception (paramètres clés et limites)

Le tableau suivant regroupe des règles d’ingénierie fréquemment utilisées pour une carte d’équilibrage BMS. Respecter ces ordres de grandeur rend le comportement stable sous courant et température.

| Règle / Paramètre | Valeur recommandée / plage | Pourquoi c’est important | Comment vérifier | Si ignoré |

|---|---|---|---|---|

| Courant d’équilibrage | 0,5 % à 2 % de la capacité cellule (Ah) | Le BMS doit corriger la dérive plus vite qu’elle n’apparaît. | Calculer le courant dans la résistance de décharge à $V_{cell,max}$. | Bloc déséquilibré ; capacité utile qui baisse. |

| Largeur lignes de mesure | 6–10 mil (0,15–0,25 mm) | Courant faible, uniquement signal ; évite des effets parasites inutiles. | Revue du routage (visualiseur Gerber). | Bruit/couplage ; mesures instables. |

| Largeur pistes puissance | Calculée pour $\Delta T < 10^\circ C$ | Limite l’échauffement local en décharge/équilibrage. | Calcul IPC‑2152 selon courant. | Pistes qui chauffent, délamination, risque feu. |

| Puissance résistance de décharge | Puissance nominale > 2× dissipation réelle | Le déclassement évite la dérive et la panne à chaud. | Fiche technique vs. $P=V^2/R$. | Panne résistance ; équilibrage inopérant. |

| MOSFET Rds(on) | < 10 mΩ (pour forts courants) | Réduit les pertes et la température du composant. | Fiche technique + estimation thermique. | MOSFET en surchauffe (open/short). |

| Précision tension | ±2 mV à ±5 mV | Détermine les seuils start/stop d’équilibrage. | Comparaison au multimètre étalonné. | Mauvais déclenchement ; surcharge ou non‑équilibrage. |

| Dégagement thermique | > 5 mm des cellules | Les points chauds dégradent la chimie des cellules. | Revue mécanique 3D + caméra thermique. | Vieillissement accéléré ; danger sécurité. |

| Distance d’isolement | > 0,5 mm par 100 V | Réduit le risque d’arc sur des blocs haute tension (>60 V). | Analyse des distances de fuite et d’isolement en CAO. | Court‑circuit, panne catastrophique. |

| Condensateurs de filtrage | 100 nF à 1 µF sur les lignes de mesure | Filtre le bruit HF (moteur/onduleur). | Oscilloscope sur nœuds de mesure. | Valeurs qui sautent ; fausses alarmes. |

| Tg PCB (transition vitreuse) | Tg élevé (>170°C) | Résiste mieux aux contraintes thermiques du passif. | Choix matériau (datasheet). | Voilage PCB ; fissures vias. |

| Vernis de tropicalisation | Acrylique ou silicone | Protège contre condensation et fuites électrolyte. | Inspection visuelle sous UV. | Corrosion ; courts‑circuits en humidité. |

Étapes de mise en œuvre (points de contrôle du processus)

Suivez ces étapes pour passer d’une idée à une carte d’équilibrage BMS réellement fabricable.

Définir la chimie et le nombre de séries :

- Identifier Li‑ion (3,6 V/4,2 V), LiFePO4 (3,2 V/3,65 V) ou LTO : cela fixe les seuils.

- Vérification : contrôler que la tension max du stack reste sous les limites de tenue des composants.

Choisir la topologie d’équilibrage :

- Passif (décharge résistive) vs actif (transfert capacitif/inductif). Le passif est courant pour <100 W ; l’actif pour des stockages à forte capacité et des contraintes d’efficacité.

- Vérification : valider budget coût, encombrement et complexité.

Calculer le courant cible :

- Estimer le déséquilibre d’auto‑décharge (souvent 2–3 %/mois) et dimensionner $R = V_{cell} / I_{balance}$.

- Vérification : s’assurer que ce courant équilibre dans la fenêtre de charge réelle du produit.

Sélection des composants + déclassement :

- Choisir des résistances de décharge adaptées (puissance/impulsions) et des MOSFETs à seuil de grille compatible si pilotage direct par IC.

- Vérification : plages de température (-40°C à +105°C si nécessaire) et marges tension/courant.

Schéma et simulation :

- Ajouter des filtres RC sur les lignes de mesure ; simuler les commutations pour éviter les pics destructeurs.

- Vérification : la tension d’activation (turn‑on) doit correspondre aux seuils cellule + hystérésis.

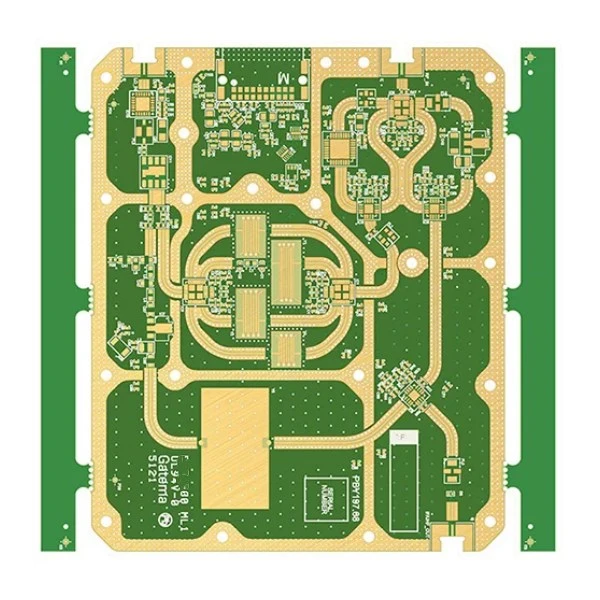

Layout PCB (focus thermique) :

- Éloigner les résistances de décharge du MCU et des capteurs température ; utiliser de larges plans cuivre reliés par vias thermiques.

- Vérification : consulter les règles PCB haute conductivité thermique et vérifier la dissipation.

Routage des mesures (Kelvin) :

- Router les mesures séparées des chemins de puissance, idéalement en mode différentiel ; prise au plus près des bornes cellules.

- Vérification : aucune boucle de commutation à fort courant ne doit longer les lignes de mesure.

Fabrication prototype :

- Commander une petite série ; verrouiller le poids cuivre (ex. 2 oz / 3 oz) prévu au design.

- Vérification : effectuer une inspection premier article (FAI) sur placement et polarités.

Tests fonctionnels :

- Tester l’activation au seuil exact ; utiliser la caméra thermique pour confirmer des hot‑spots typiquement <60°C–80°C.

- Vérification : vérifier que l’équilibrage s’arrête bien sous la limite d’hystérésis.

Dépannage (modes de défaillance et correctifs)

Même avec une bonne conception, certains problèmes reviennent souvent. Voici une grille pratique pour les diagnostiquer.

Symptôme : les cellules restent déséquilibrées après une charge complète

- Causes : courant d’équilibrage trop faible ; charge terminée trop tôt ; erreur de mesure.

- Contrôles : mesurer le courant réel dans les résistances ; vérifier si la coupure chargeur est sous le seuil de démarrage d’équilibrage.

- Correctif : réduire la valeur des résistances (augmenter le courant) ; ajuster la stratégie de charge ; recalibrer.

- Prévention : dimensionner sur le pire cas de mismatch, pas sur le nominal.

Symptôme : décoloration du PCB / odeur de chaud

- Causes : résistances surchargées ; pistes sous‑dimensionnées ; cuivre insuffisant.

- Contrôles : thermographie en fonctionnement ; vérifier $P=V^2/R$ vs datasheet.

- Correctif : augmenter puissance résistances ; ajouter cuivre ; améliorer convection.

- Prévention : déclassement (souvent ~50 %) ; envisager PCB à âme métallique si très forte charge thermique.

Symptôme : valeurs de tension instables

- Causes : bruit sur les lignes de mesure ; masse mal définie ; repliement de spectre.

- Contrôles : oscilloscope sur entrée ADC ; recherche de boucles de masse.

- Correctif : augmenter/ajouter un filtre RC (ex. 1 kΩ + 100 nF) ; éloigner les lignes de mesure des nœuds de commutation.

- Prévention : mesures différentielles + plan de masse correctement séparé.

Symptôme : MOSFET d’équilibrage en court‑circuit (toujours ON)

- Causes : ESD ; surtension ; surchauffe.

- Contrôles : mesures Gate‑Source / Drain‑Source ; vérifier protections (TVS, diodes si charge inductive).

- Correctif : remplacer ; ajouter TVS.

- Prévention : $V_{ds}$ ≥ 1,5× $V_{cell,max}$ ; résistance de gate pour ralentir la commutation.

Symptôme : le BMS coupe trop tôt

- Causes : chute IR sur lignes de mesure ; faux déclenchement OV.

- Contrôles : comparer tension aux bornes cellule vs lecture BMS sous charge.

- Correctif : améliorer la connexion Kelvin ; optimiser le routage des lignes de mesure.

- Prévention : intégrer la résistance connecteur/liaisons dans la conception.

Symptôme : la batterie se vide en stockage

- Causes : courant de repos élevé ; MOSFETs fuyards ; résidus flux (chemins de fuite).

- Contrôles : mesurer le courant de veille ; inspection pour courts partiels et courants de fuite.

- Correctif : choisir ICs ultra‑low‑power ; nettoyer les résidus.

- Prévention : mode veille solide + process de nettoyage strict.

Comment choisir (passif vs actif)

Le choix passif/actif est structurant : il fixe l’efficacité, la chaleur dissipée, le coût et le niveau EMI.

1. Équilibrage passif (décharge résistive)

- Principe : dissiper l’énergie de la cellule la plus haute via une résistance.

- Avantages : simple, peu coûteux, compact, robuste.

- Inconvénients : inefficace (chaleur), courant limité (souvent <200 mA), lent pour de gros blocs batterie.

- Cas d’usage : e‑bikes, outils, laptops, produits grand public.

- Point clé : la thermique devient votre contrainte n°1.

2. Équilibrage actif (transfert d’énergie)

- Principe : transférer l’énergie vers les cellules plus basses (ou vers le bloc) via capacités/inductances.

- Avantages : rendement élevé (>90 %), très peu de chaleur, courants élevés (1 A–10 A), plus de capacité utile.

- Inconvénients : coûteux, contrôle plus complexe, surface PCB plus grande, EMI plus critique.

- Cas d’usage : VE, systèmes ESS de grande capacité, blocs batterie à forte valeur.

- Point clé : optimisation fréquence de découpage et blindage EMI.

Matrice de décision : Si votre bloc < 20 Ah et que le coût domine, choisissez plutôt Passif. Si votre bloc > 50 Ah ou que l’efficacité est critique, choisissez plutôt Actif. Entre 20 Ah et 50 Ah, la décision dépend surtout des contraintes thermiques du boîtier.

FAQ (coût, délai, DFM)

Q : Quel est l’impact coût typique de l’équilibrage sur un PCB BMS ? R : En passif, l’impact est souvent limité (résistances + MOSFETs), typiquement ~$0,50–$2,00 par chaîne série selon le volume. En actif, le coût augmente nettement (inductances/transformateurs + contrôleur), souvent +$10 à $30+ par carte.

Q : L’équilibrage impacte‑t‑il le délai de fabrication du PCB ? R : Les conceptions passives standards n’allongent généralement pas les délais (5–10 jours). Les designs nécessitant du cuivre épais (3 oz+) ou des matériaux high‑Tg peuvent ajouter 3–5 jours.

Q : Quels critères d’acceptation pour l’assemblage d’une carte d’équilibrage BMS ? R : AOI pour les joints de soudure, ICT pour les valeurs, puis un test fonctionnel en simulant des entrées cellule. Le courant d’équilibrage doit être dans ±10 % de la cible, et le courant de fuite sous le seuil spécifié (souvent <10 µA).

Q : Quels fichiers DFM faut‑il fournir ? R : Gerbers (RS‑274X), fichier Centroid/PnP, BOM détaillée, et une note précisant les exigences d’isolement/tension de claquage, ainsi que les zones à exclure du vernis de tropicalisation (connecteurs, points de test).

Q : Puis‑je utiliser du FR4 standard ? R : Oui pour beaucoup de designs passifs à faible courant. Pour >500 mA ou des zones très denses en chaleur, un FR4 high‑Tg (Tg 170) réduit le risque de délamination. En extrême, envisager des PCB à âme en aluminium ou métal.

Q : Comment tester l’équilibrage sans batteries ? R : Avec un simulateur de cellules ou plusieurs alimentations de précision. Une échelle de résistances permet aussi de créer un stack équilibré, puis un déséquilibre contrôlé.

Q : Quelle finition de surface recommandez‑vous ? R : L’ENIG est souvent privilégié : planéité adaptée au pas fin (IC BMS) et bonne résistance à la corrosion.

Q : Comment traiter les chemins de fort courant dans le routage ? R : Utiliser des polygones/plans plutôt que des pistes fines, calculer le dimensionnement au courant du bloc. Au‑delà, prévoir des barres omnibus et/ou des couches cuivre épais pour 50 A+.

Q : Pourquoi entend‑on parfois un bourdonnement ? R : Souvent du coil‑whine (inductances) ou des MLCCs qui “chantent” en actif. En passif, une PWM dans la bande audible (20 Hz–20 kHz) peut aussi générer du bruit ; augmenter la fréquence aide souvent.

Q : APTPCB propose‑t‑il des tests fonctionnels ? R : Oui, nous pouvons réaliser des FCT (tests fonctionnels de circuits) selon votre procédure et vos exigences de banc de test.

Ressources (pages et outils connexes)

- Solutions PCB Power & Energy: capacités pour électronique batterie/énergie.

- Directives DFM: liste de contrôle pour préparer la série.

- Assemblage SMT: process pour IC BMS au pas fin et composants de puissance.

Glossaire (termes clés)

| Terme | Définition |

|---|---|

| Équilibrage de cellules | Égaliser tension et SOC des cellules d’un bloc série. |

| Équilibrage passif | Dissiper l’énergie de la cellule la plus haute sous forme de chaleur via une résistance de décharge. |

| Équilibrage actif | Transférer/redistribuer l’énergie des cellules hautes vers les basses via C/L. |

| BMS (système de gestion de batterie) | Système électronique de surveillance et de protection d’une batterie ou d’un bloc. |

| SOC (état de charge) | Niveau de charge relatif à la capacité (en %). |

| SOH (état de santé) | Indicateur d’état ou d’usure du bloc par rapport au nominal. |

| Résistance de décharge | Résistance de puissance utilisée pour vider l’excès d’énergie d’une cellule en mode passif. |

| Connexion Kelvin (4 fils) | Mesure de tension qui supprime l’effet des résistances de liaisons. |

| OCV (tension à circuit ouvert) | Tension aux bornes sans charge (sans courant). |

| C‑Rate | Taux de charge/décharge relatif à la capacité nominale. |

| Emballement thermique | Boucle d’auto‑échauffement menant à une augmentation incontrôlée de température. |

| Hystérésis | Écart entre seuil de démarrage et seuil d’arrêt pour éviter les oscillations. |

Demander un devis pour une carte d’équilibrage BMS

Prêt à passer votre carte d’équilibrage BMS du prototype à la série ? APTPCB peut réaliser une revue DFM pour détecter les risques thermiques et de routage avant l’industrialisation. Envoyez vos Gerbers, BOM et exigences de test pour recevoir un devis détaillé sous 24 heures.

Conclusion (prochaines étapes)

Une carte d’équilibrage BMS fiable exige une approche disciplinée : thermique, précision de mesure, déclassement et DFM. Que vous choisissiez un équilibrage passif économique ou une topologie active à haut rendement, la qualité de l’implantation et du routage fixe la sécurité et la durée de vie du bloc batterie. En appliquant les règles, points de contrôle et scénarios de dépannage ci‑dessus, vous augmentez fortement vos chances de réussite au test et en production.