Le calcul haute performance exige des débits de données plus rapides entre les puces hétérogènes, faisant du contrôle d'impédance de la carte d'interconnexion EMIB un facteur critique dans l'encapsulation moderne des semi-conducteurs. À mesure que les conceptions évoluent vers l'encapsulation 2.5D et les architectures de chiplets, les frontières traditionnelles entre le PCB et le substrat d'encapsulation s'estompent. Assurer l'intégrité du signal à travers le pont intégré et le substrat organique environnant exige une exécution de fabrication précise. Ce guide fournit un flux de travail complet pour les ingénieurs et les équipes d'approvisionnement afin de gérer l'impédance dans ces interconnexions avancées.

Points Clés à Retenir

- Définition : Le contrôle d'impédance de la carte d'interconnexion EMIB fait référence au maintien d'une impédance caractéristique spécifique (généralement 85Ω ou 100Ω différentielle) à travers la transition du pont en silicium vers le substrat organique.

- Métrique Critique : La perte de retour et la perte d'insertion sont tout aussi importantes que la valeur d'impédance cible ($Z_0$) dans l'intégration de chiplets à haute vitesse.

- Impact Matériel : La désadaptation de la constante diélectrique ($D_k$) entre le pont en silicium et les couches d'empilement du PCB est la principale source de réflexion du signal.

- Idée Faussée : Beaucoup supposent que les tolérances standard des PCB (+/- 10%) sont suffisantes ; cependant, les conceptions EMIB nécessitent souvent un contrôle de +/- 5% ou plus strict.

- Validation : Les tests de réflectométrie dans le domaine temporel (TDR) doivent être effectués sur des coupons de test spécifiques qui imitent la transition pont-carte, et non pas seulement sur des coupons de trace standard.

- Conseil de fabrication : Le contrôle de la rugosité de surface du cuivre est essentiel pour minimiser les pertes par effet de peau aux fréquences supérieures à 25 GHz.

- APTPCB (APTPCB PCB Factory) est spécialisée dans les processus de PCB HDI et de type substrat de haute précision nécessaires pour prendre en charge ces architectures d'encapsulation avancées.

Ce que signifie réellement le contrôle d'impédance des cartes d'interconnexion EMIB

Comprendre la définition fondamentale est la première étape avant d'analyser des métriques spécifiques et des tolérances de fabrication.

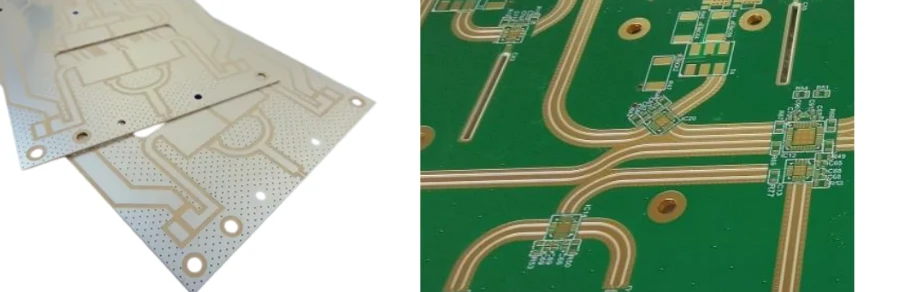

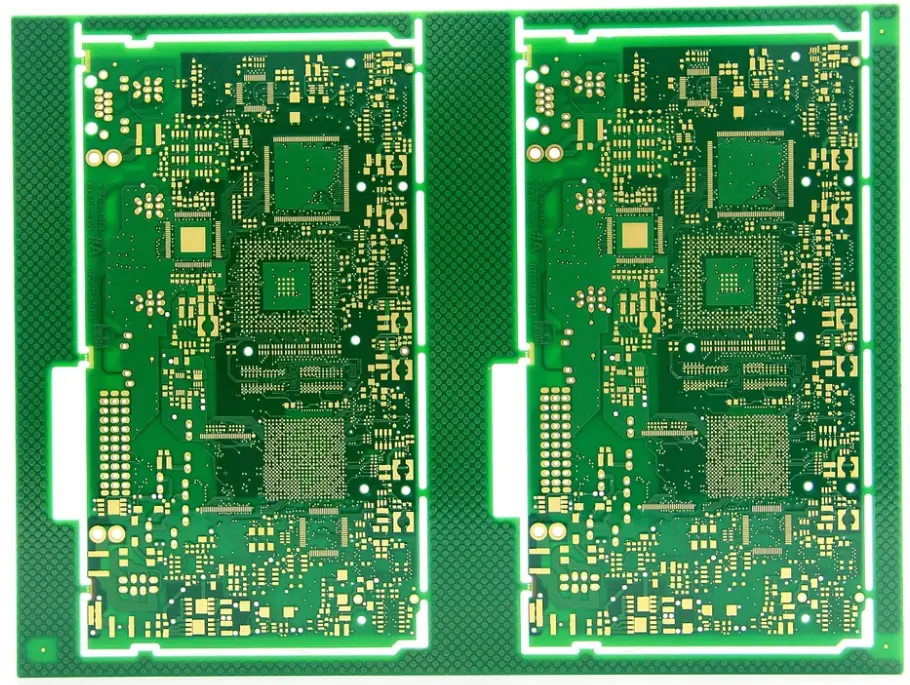

Le contrôle d'impédance des cartes d'interconnexion EMIB est la discipline d'ingénierie qui gère la résistance électrique aux signaux CA lorsqu'ils voyagent entre le pont de silicium intégré et le substrat d'encapsulation organique. Contrairement aux PCB standard où les pistes courent sur des couches de fibre de verre uniformes, une structure EMIB (Embedded Multi-die Interconnect Bridge) implique un environnement hybride. Les signaux doivent traverser d'une puce de silicium, à travers des micro-bosses, vers un pont de silicium, et de là vers le substrat d'encapsulation. La "carte d'interconnexion" dans ce contexte agit comme le support. Elle doit correspondre à l'impédance du routage à pas ultra-fin sur le pont de silicium. Si l'impédance ne correspond pas à l'interface, des réflexions de signal se produisent. Ces réflexions entraînent une corruption des données, une augmentation des taux d'erreur binaire (BER) et une réduction de l'efficacité énergétique. Pour APTPCB, atteindre ce contrôle signifie utiliser des techniques HDI (High Density Interconnect) avancées, des microvias laser et des matériaux diélectriques ultra-minces qui comblent le fossé entre la fabrication de semi-conducteurs et la fabrication traditionnelle de PCB.

Métriques de contrôle d'impédance de la carte d'interconnexion EMIB qui comptent

Une fois que la portée du contrôle d'impédance est définie, les ingénieurs doivent quantifier la qualité à l'aide d'indicateurs de performance spécifiques.

Le succès de la conception d'une carte d'interconnexion EMIB repose sur le strict respect des métriques d'intégrité du signal. Dans les applications à haute vitesse comme les accélérateurs d'IA ou les processeurs de centres de données, un simple "réussite/échec" sur la résistance est insuffisant. Vous devez évaluer le comportement de la carte sur un spectre de fréquences.

| Métrique | Pourquoi c'est important | Plage typique / Facteurs | Comment mesurer |

|---|---|---|---|

| Impédance Caractéristique ($Z_0$) | Détermine si le chemin du signal correspond à la source et à la charge. Les désadaptations provoquent des réflexions. | 85Ω ou 100Ω (Différentiel) ; 50Ω (Asymétrique). Tolérance : ±5% à ±10%. | Réflectométrie dans le domaine temporel (TDR) sur des coupons de test. |

| Perte d'insertion | Mesure la quantité de puissance de signal perdue lors de son passage à travers l'interconnexion. | < -1,5 dB par pouce à la fréquence de Nyquist. Fortement influencé par la rugosité du cuivre et $D_k$. | Analyseur de réseau vectoriel (VNA) ou extraction de paramètres S. |

| Perte de retour | Mesure la quantité de signal renvoyée à la source en raison de discontinuités d'impédance. | < -10 dB à -15 dB est souhaitable. Plus bas est mieux. | VNA (paramètre S11). |

| Décalage (Intra-paire) | La différence de temps de propagation entre les lignes positive et négative d'une paire différentielle. | < 5 ps (picosecondes). Critique pour la signalisation différentielle. | TDR ou Oscilloscope. |

| Stabilité de la constante diélectrique ($D_k$) | Les variations de $D_k$ provoquent des fluctuations d'impédance le long de la trace. | $D_k$ stable sur toute la gamme de fréquences (par exemple, 3,0 - 3,5 pour les substrats avancés). | Vérification de la fiche technique du matériau et anneaux résonateurs. |

| Rugosité de surface du cuivre | Le cuivre rugueux augmente la résistance aux hautes fréquences (effet de peau). | $R_z$ < 2 µm (feuille de cuivre VLP ou HVLP recommandée). | Profilomètre ou MEB (Microscope Électronique à Balayage). |

Comment choisir le contrôle d'impédance de la carte d'interconnexion EMIB : guide de sélection par scénario

Une fois les métriques établies, le prochain défi consiste à sélectionner la bonne stratégie de contrôle en fonction du scénario d'application spécifique. Différents cas d'utilisation finale exigent différents niveaux de rigueur dans le contrôle de l'impédance des cartes d'interconnexion EMIB. Une spécification excessive ajoute des coûts inutiles, tandis qu'une spécification insuffisante entraîne une défaillance du système.

Scénario 1 : Calcul haute performance (HPC) et IA

- Exigence : Bande passante maximale (intégration HBM).

- Compromis : Nécessite la tolérance d'impédance la plus stricte (±5 %) et des matériaux à très faible perte.

- Conseil : Choisissez des films de construction avancés (ABF) et du cuivre HVLP. Le coût est secondaire par rapport à la performance.

Scénario 2 : Appareils mobiles grand public

- Exigence : Miniaturisation et autonomie de la batterie.

- Compromis : Les contraintes d'espace imposent des diélectriques plus minces, ce qui rend le contrôle de l'impédance plus difficile.

- Conseil : Privilégiez les matériaux de base minces. Acceptez des tolérances légèrement plus lâches (±7-10 %) pour maintenir le rendement et réduire les coûts.

Scénario 3 : Systèmes ADAS automobiles

- Exigence : Fiabilité et stabilité thermique.

- Compromis : Les matériaux doivent résister aux cycles thermiques, qui peuvent modifier l'impédance au fil du temps.

- Conseil : Sélectionnez des matériaux à Tg élevé avec un $D_k$ stable sur de larges plages de température. La validation doit inclure des tests de contrainte thermique.

Scénario 4 : Infrastructure 5G / Stations de base

- Exigence : Haute fréquence et faible latence.

- Compromis : Les longues longueurs de trace sur le substrat augmentent les risques de perte d'insertion.

- Conseil : Concentrez-vous sur les stratifiés "Low Loss" et "Ultra Low Loss". Le contrôle d'impédance doit tenir compte des bandes de fréquences spécifiques (mmWave).

Scénario 5 : Prototype / NPI (Nouvelle Introduction de Produit)

- Exigence : Vitesse de livraison et débogage.

- Compromis : Les délais rapides peuvent limiter la disponibilité des matériaux.

- Conseil : Utilisez des matériaux haute vitesse standard disponibles. Concentrez-vous sur la validation de la logique de conception plutôt que sur une optimisation parfaite de l'impédance.

Scénario 6 : Production de Masse (Sensible aux Coûts)

- Exigence : Rendement et efficacité des coûts.

- Compromis : Ne peut pas maintenir des tolérances ultra-serrées sans des taux de rebut élevés.

- Conseil : Conception pour la fabrication (DFM). Élargir les pistes si possible pour rendre l'impédance moins sensible aux variations de gravure.

Points de contrôle de la mise en œuvre du contrôle d'impédance des cartes d'interconnexion EMIB

Après avoir sélectionné la bonne stratégie, l'accent est mis sur l'exécution tactique, des fichiers de conception au produit final.

La mise en œuvre du contrôle d'impédance des cartes d'interconnexion EMIB nécessite un effort synchronisé entre l'ingénieur de conception et l'atelier de fabrication. Utilisez cette liste de contrôle pour vous assurer qu'aucune étape critique n'est manquée pendant le processus de fabrication des PCB HDI.

- Définition de l'empilement :

- Recommandation : Définir explicitement le nombre de couches, les épaisseurs diélectriques et les poids de cuivre.

- Risque : Les empilements ambigus conduisent à des calculs d'impédance incorrects par l'ingénieur CAM.

- Acceptation : Fiche d'empilement approuvée, signée par le concepteur et le fabricant.

Sélection des matériaux :

- Recommandation : Spécifier la série exacte du matériau (par exemple, Megtron 6, Rogers ou des films ABF spécifiques).

- Risque : Les désignations génériques "FR4" échoueront aux vitesses EMIB.

- Acceptation : Certification des matériaux (CoC) du fournisseur.

Largeur et espacement des pistes (L/S) :

- Recommandation : Ajuster la largeur des pistes dans le CAM pour compenser les facteurs de gravure (forme trapézoïdale).

- Risque : La sur-gravure réduit la largeur des pistes, augmentant l'impédance.

- Acceptation : Analyse en coupe transversale (micro-section) vérifiant la géométrie.

Continuité du plan de référence :

- Recommandation : Assurer des plans de masse solides sous les signaux à haute vitesse, en particulier près de l'interface du pont.

- Risque : Les ruptures dans le plan de référence provoquent des discontinuités d'impédance immédiates.

- Acceptation : Inspection Optique Automatisée (AOI) des couches internes.

Enregistrement des microvias :

- Recommandation : L'alignement du perçage laser doit être précis pour connecter les pastilles du pont au substrat.

- Risque : Un désalignement modifie le couplage capacitif, altérant l'impédance.

- Acceptation : Inspection aux rayons X de l'alignement des vias.

Épaisseur du placage de cuivre :

- Recommandation : Maintenir une distribution uniforme du placage.

- Risque : Les variations d'épaisseur du cuivre affectent l'inductance totale de la ligne.

- Acceptation : Mesure d'épaisseur non destructive (CMI).

Application de la finition de surface :

- Recommandation : Utiliser ENIG ou ENEPIG pour les surfaces planes adaptées au wire bonding ou au flip-chip.

- Risque : Les finitions HASL épaisses créent des surfaces inégales et des variations d'impédance.

- Acceptation : Mesure de l'épaisseur de la finition de surface (XRF).

Compensation de la gravure :

- Recommandation : L'usine doit appliquer une compensation globale de la gravure basée sur le poids du cuivre.

- Risque : Une gravure incohérente sur le panneau entraîne une variation d'impédance entre les unités.

- Acceptation : Test de coupon d'impédance sur les bords du panneau.

Effet du masque de soudure :

- Recommandation : Tenir compte du $D_k$ du masque de soudure dans le calcul de l'impédance (pour les couches externes).

- Risque : Le masque de soudure réduit l'impédance de 2-3 ohms ; ignorer cela entraîne des défaillances.

- Acceptation : Mesure TDR après l'application du masque de soudure.

Validation TDR finale :

- Recommandation : Test à 100 % des coupons d'impédance pour les lots critiques.

- Risque : Expédition de cartes qui réussissent la continuité électrique mais échouent à l'intégrité du signal.

- Acceptation : Rapport TDR montrant la réussite/l'échec par rapport à la tolérance.

Erreurs courantes de contrôle d'impédance des cartes d'interconnexion EMIB

Même avec une liste de contrôle, des erreurs spécifiques se produisent fréquemment dans l'environnement complexe de la fabrication de ponts intégrés.

Éviter ces pièges courants dans le contrôle d'impédance des cartes d'interconnexion EMIB peut économiser des semaines de temps de reconception et des milliers de dollars de rebut.

- Ignorer la "zone de transition" : La discontinuité d'impédance la plus critique se produit lorsque le signal passe du pont en silicium au substrat de la carte de circuit imprimé. Les concepteurs adaptent souvent l'impédance de la trace mais ignorent la capacité parasite du pad/bump de connexion. Correction : Simulez la transition dans des solveurs de champ 3D et optimisez l'empilement des pads.

- Utiliser des constantes diélectriques génériques : Se fier à la valeur $D_k$ "marketing" (par exemple, 4,0) au lieu de la valeur dépendante de la fréquence (par exemple, 3,8 à 10 GHz). Correction : Demandez le tableau des matériaux dépendants de la fréquence à APTPCB.

- Négliger les modèles de rugosité du cuivre : Les calculateurs d'impédance standard supposent un cuivre lisse. Aux vitesses EMIB, la rugosité ajoute un délai et une perte significatifs. Correction : Utilisez le modèle de Huray ou des facteurs de correction de rugosité similaires dans les calculs.

- Coupons de test inadéquats : Placer les coupons de test trop loin du circuit réel ou utiliser des conceptions qui ne correspondent pas à la densité réelle des traces. Correction : Utilisez des coupons intégrés ou des structures de test "in-circuit" lorsque cela est possible.

- Négliger les tolérances de fabrication : Concevoir une ligne de 50 ohms qui nécessite une trace de 3,1 mil, alors que la capacité minimale de l'usine est de 3 mil +/- 0,5 mil. Correction : Consultez tôt le Calculateur d'impédance et les règles de conception.

- Omission de prendre en compte les zones riches en résine : Dans les substrats hétérogènes, la résine peut s'accumuler dans les espaces entre les pistes, modifiant le $D_k$ local. Correction : Utilisez un remplissage de cuivre factice (thieving) pour assurer une distribution et un pressage uniformes de la résine.

Questions fréquentes (FAQ) sur le contrôle d'impédance des cartes d'interconnexion EMIB

Pour conclure les détails techniques, voici les réponses aux questions les plus urgentes concernant la logistique et l'exécution.

Q : Comment un contrôle strict de l'impédance des cartes d'interconnexion EMIB impacte-t-il le coût global ? R : Le resserrement des tolérances de ±10% à ±5% peut augmenter les coûts de 15 à 25%. Cela est dû à la nécessité de matériaux de qualité supérieure, de tests TDR plus fréquents et de rendements de fabrication inférieurs.

Q : Quel est le délai typique pour les prototypes de cartes d'interconnexion EMIB avec des exigences d'impédance ? R : Les délais standard sont de 15 à 20 jours. Cependant, si des matériaux spécialisés à faible perte ou des films ABF sont nécessaires, les délais peuvent s'étendre à 4-6 semaines en fonction de la disponibilité des matériaux.

Q : Quels sont les meilleurs matériaux pour le contrôle d'impédance des cartes d'interconnexion EMIB à 56 Gbit/s ? R : Le FR4 standard n'est pas adapté. Vous devriez utiliser des matériaux comme Panasonic Megtron 6/7, Isola Tachyon, ou des films Ajinomoto Build-up (ABF) spécialisés qui offrent une faible tangente de perte ($D_f$) et un $D_k$ stable.

Q : Comment les tests sont-ils effectués pour les couches enterrées dans un substrat EMIB ? A: Tester les couches enterrées est difficile sur une carte finie. Nous utilisons des "coupons de test" situés sur les rails du panneau qui ont la même structure de couche et la même géométrie de trace que la carte réelle. Ceux-ci sont testés via TDR avant que les couches externes ne soient laminées ou après la fabrication finale.

Q: Quels sont les critères d'acceptation pour les tests TDR sur ces cartes? A: Le critère d'acceptation standard est que l'impédance mesurée doit se situer dans la tolérance spécifiée (par exemple, 100Ω ±10%). De plus, la forme d'onde TDR doit être lisse, sans creux ou pics prononcés indiquant des discontinuités.

Q: Puis-je utiliser des vias standard pour la conception de cartes d'interconnexion EMIB? A: Généralement, non. Les conceptions EMIB nécessitent un routage haute densité qui exige des microvias laser, des vias borgnes et des vias enterrés pour gérer l'intégrité du signal et la densité. Les forets mécaniques sont souvent trop grands et créent trop de capacité parasite.

Q: Comment spécifier le contrôle d'impédance dans mes fichiers Gerber? A: Ne vous fiez pas uniquement aux noms de fichiers Gerber. Incluez un dessin de fabrication détaillé (Fab Drawing) qui liste les couches spécifiques, les largeurs de trace, les plans de référence et les valeurs d'impédance cibles pour chaque groupe de signaux.

Q: Quelle est la différence entre l'impédance asymétrique (single-ended) et différentielle dans ce contexte? A: L'impédance asymétrique (single-ended) fait référence à une piste par rapport à un plan de masse (généralement 50Ω). L'impédance différentielle fait référence à deux pistes l'une par rapport à l'autre et au plan de masse (généralement 85Ω ou 100Ω). Les chemins de données EMIB sont presque exclusivement différentiels pour rejeter le bruit.

Ressources pour le contrôle d'impédance des cartes d'interconnexion EMIB

- Fabrication de PCB haute vitesse: Découvrez les capacités de fabrication de cartes supportant des débits de données élevés.

- Calculateur d'impédance: Un outil pour estimer la largeur et l'espacement des pistes pour votre impédance cible.

- Technologie PCB HDI: Découvrez les technologies de microvias et de lignes fines essentielles pour les substrats EMIB.

- Conception d'empilement de PCB: Directives pour l'agencement des couches afin d'obtenir une intégrité de signal optimale.

Glossaire du contrôle d'impédance des cartes d'interconnexion EMIB

| Terme | Définition |

|---|---|

| EMIB | Embedded Multi-die Interconnect Bridge. Une technologie utilisant un pont en silicium intégré dans un substrat pour connecter des puces. |

| Impédance ($Z_0$) | L'opposition qu'un circuit présente au passage d'un courant lorsqu'une tension est appliquée. |

| TDR | Réflectométrie dans le domaine temporel. Une technique de mesure utilisée pour déterminer l'impédance d'une ligne. |

| Microvia | Un petit trou percé au laser (généralement < 150µm) pour connecter des couches adjacentes dans les cartes HDI. |

| ABF | Film Ajinomoto Build-up. Un matériau isolant dominant utilisé dans les substrats de circuits intégrés pour les CPU/GPU hautes performances. |

| CTE | Coefficient de Dilatation Thermique. Le taux auquel un matériau se dilate avec la chaleur. Les déséquilibres provoquent des problèmes de fiabilité. |

| Insertion Loss | Perte d'Insertion. La perte de puissance du signal résultant de l'insertion d'un dispositif (ou d'une trace) dans une ligne de transmission. |

| Return Loss | Perte de Retour. La perte de puissance dans le signal renvoyé/réfléchi par une discontinuité dans une ligne de transmission. |

| Differential Pair | Paire Différentielle. Deux signaux complémentaires utilisés pour transmettre des données, offrant une immunité élevée au bruit. |

| Skin Effect | Effet de Peau. La tendance du courant alternatif à haute fréquence à se distribuer près de la surface du conducteur. |

| Dielectric Constant ($D_k$) | Constante Diélectrique ($D_k$). Une mesure de la capacité d'un matériau à stocker de l'énergie électrique dans un champ électrique. Affecte la vitesse du signal et l'impédance. |

| Loss Tangent ($D_f$) | Tangente de Perte ($D_f$). Une mesure de la puissance du signal perdue sous forme de chaleur dans le matériau diélectrique. |

| RDL | Couche de Redistribution. Couches métalliques sur une puce ou un substrat qui redirigent les pads d'E/S vers différents emplacements. |

Conclusion finale : Prochaines étapes pour le contrôle de l'impédance de la carte d'interconnexion EMIB

La maîtrise du contrôle d'impédance des cartes d'interconnexion EMIB est une condition préalable pour être compétitif à l'ère des chiplets et de l'intégration hétérogène. Cela exige un changement de mentalité, passant de la "connexion de points" à la "gestion des lignes de transmission". En comprenant les métriques de perte d'insertion et de perte de retour, en sélectionnant les bons matériaux et en appliquant des points de contrôle de fabrication stricts, vous pouvez garantir que vos conceptions haute performance fonctionnent comme prévu.

Si vous êtes prêt à faire passer votre conception du concept à la production, APTPCB est prêt à vous aider. Pour obtenir une évaluation DFM précise et un devis, veuillez fournir les éléments suivants :

- Fichiers Gerber (RS-274X) ou données ODB++.

- Diagramme d'empilement indiquant les matériaux souhaités et le nombre de couches.

- Exigences d'impédance (par exemple, Couche 3, 100Ω Diff, Largeur de trace 4mil).

- Netlist pour la validation des tests électriques.

Visitez notre Page de devis pour démarrer votre projet dès aujourd'hui.