Points clés à retenir

- Définition : La couverture ICT (In-Circuit Test) en usine pour les PLC fait référence au pourcentage de réseaux et de composants sur une carte de contrôleur logique programmable qui peuvent être vérifiés électriquement pendant la fabrication.

- Criticité : Contrairement à l'électronique grand public, les PLC exigent une fiabilité proche de 100 % ; les défauts non détectés peuvent entraîner des défaillances industrielles catastrophiques.

- Métriques : La norme PCOLA/SOQ est la référence de l'industrie pour mesurer la qualité de la couverture, et pas seulement de simples pourcentages.

- Conception pour le test (DFT) : Atteindre une couverture élevée commence au stade du schéma, et non à l'usine.

- Compromis : Une couverture plus élevée nécessite souvent des PCB plus grands ou des montages plus coûteux ; équilibrer cela est essentiel pour une production rentable.

- Validation : Les rapports de simulation doivent être validés par rapport aux résultats des tests physiques lors de l'inspection du premier article (FAI).

- Partenariat : Travailler avec un fabricant compétent comme APTPCB (APTPCB PCB Factory) garantit que votre stratégie DFT s'aligne sur les capacités de production réelles.

Dans le contexte des contrôleurs logiques programmables (PLC) (portée et limites)

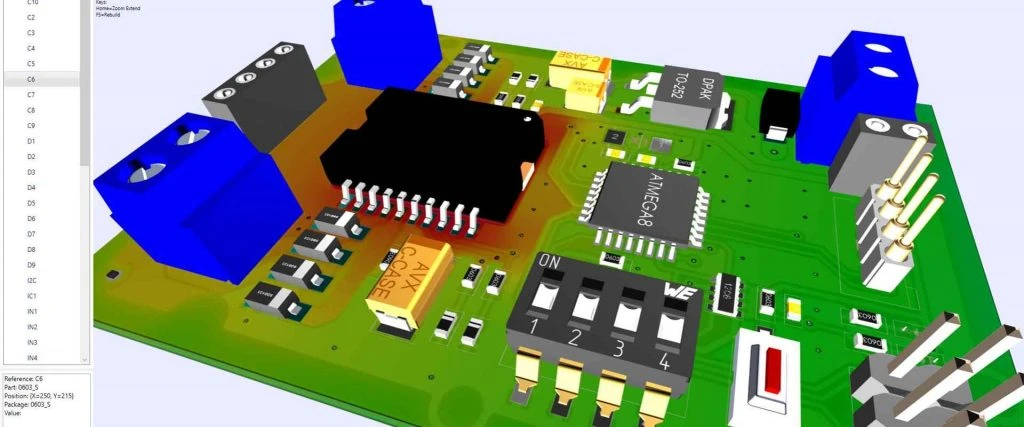

Comprendre la portée des tests est la première étape pour garantir la fiabilité industrielle des systèmes de contrôle. La couverture ICT en usine pour les PLC est une mesure quantitative de la proportion de la logique et de la connectivité d'une carte de circuit imprimé qui peut être validée à l'aide d'un testeur "à lit de clous". Dans le contexte des contrôleurs logiques programmables (PLC), cette métrique est bien plus critique que dans l'électronique générale. Les PLC fonctionnent dans des environnements difficiles impliquant des vibrations, des températures extrêmes et des interférences électromagnétiques. Une soudure qui passe une inspection visuelle mais échoue à un test de stress électrique peut entraîner l'arrêt d'une usine des mois plus tard.

L'ICT (In-Circuit Test) cible spécifiquement :

- Courts-circuits et Ouvertures: S'assurer qu'il n'existe pas de ponts non intentionnels entre les réseaux et que les pistes sont continues.

- Valeurs des Composants: Vérifier que la résistance, la capacitance et l'inductance correspondent à la nomenclature (BOM).

- Présence et Orientation des Composants: S'assurer que les puces sont montées et orientées correctement.

- Fonction des Composants Actifs: Effectuer des vérifications logiques de base sur les diodes, les transistors et les circuits intégrés.

Il est important de distinguer la couverture ICT de la couverture du Test Fonctionnel du Circuit (FCT). L'ICT recherche les défauts de fabrication (ponts de soudure, pièces incorrectes), tandis que le FCT vérifie que la carte exécute sa logique prévue. Pour un PLC, une couverture ICT élevée est le fondement qui rend le FCT significatif. Si les connexions physiques ne sont pas vérifiées en premier, le débogage fonctionnel devient impossible. Chez APTPCB, nous soulignons que la couverture n'est pas seulement un pourcentage. C'est un outil de gestion des risques. Une carte avec une couverture de 95% pourrait encore manquer le seul relais de sécurité critique qui protège l'ensemble du système. Par conséquent, la portée doit privilégier les "réseaux critiques" par rapport aux statistiques de couverture génériques.

Métriques importantes (comment évaluer la qualité)

Mesurer la couverture exige plus qu'un simple rapport de réussite/échec ; cela demande une analyse granulaire des types de défauts spécifiques.

Pour évaluer véritablement la couverture ICT en usine pour les PLC, les ingénieurs utilisent des métriques spécifiques qui catégorisent ce qui est testé et avec quelle efficacité. La norme industrielle pour cela est le modèle PCOLA/SOQ. Ce modèle sépare les attributs des composants (PCOLA) des attributs de connexion (SOQ).

| Métrique | Pourquoi c'est important | Plage typique ou facteurs influençants | Comment mesurer |

|---|---|---|---|

| Taux d'accès au test | Détermine si les sondes peuvent physiquement atteindre les réseaux. | 90% - 100%. Inférieur sur les cartes HDI. | (Réseaux avec points de test / Réseaux totaux) × 100. |

| Couverture des composants | Assure que les bonnes pièces sont installées. | 85% - 98%. Limité par les condensateurs de dérivation en parallèle. | Nombre de composants avec des valeurs vérifiées / Nombre total de la nomenclature. |

| Couverture du réseau | Vérifie la continuité et l'isolation. | 95% - 100%. Critique pour les plans d'alimentation et de masse. | Nombre de réseaux entièrement testés / Nombre total de la netlist. |

| Taux de faux échecs | Un nombre élevé de faux échecs ralentit la production et endommage les pastilles. | < 500 PPM. Influencé par la qualité du montage et la contrainte. | (Fausses alarmes / Nombre total de cartes testées) × 1 000 000. |

| Score PCOLA | Vérifie la Présence, la Correction, l'Orientation, le Fonctionnement, l'Alignement. | Élevé. Essentiel pour les CI et connecteurs complexes. | Analyse logicielle automatisée de la génération du programme de test. |

| Score SOQ | Vérifie les Courts-circuits, les Ouvertures, la Qualité (intégrité des joints de soudure). | Critique. Doit être proche de 100% pour la sécurité des automates. | Mesuré via des seuils de résistance pendant la phase de test de court-circuit/ouverture. |

| Gauge R&R | Garantit que le montage de test est cohérent et reproductible. | < 10%. Si >30%, le système de test n'est pas fiable. | Analyse statistique des mesures répétées sur la même unité. |

Guide de sélection par scénario (compromis)

Différents scénarios de fabrication dictent différentes approches pour atteindre une couverture de test optimale.

Atteindre une couverture ICT d'usine à 100% pour les automates est souvent physiquement impossible ou économiquement non viable. Vous devez choisir la bonne stratégie en fonction du cycle de vie de votre produit et des contraintes techniques. Ci-dessous sont présentés les scénarios courants et l'approche recommandée pour chacun.

1. Production à grand volume, faible mix

- Scénario: Production de masse de modules E/S d'automates standard.

- Recommandation: Investir dans un montage à vide haut de gamme avec sondage double face.

- Compromis : Coût d'outillage initial élevé (5k $ - 15k $), mais temps de test par unité le plus bas et répétabilité la plus élevée.

- Aperçu APTPCB : Pour des volumes supérieurs à 5 000 unités, le coût du banc de test s'amortit rapidement, justifiant la dépense pour une couverture maximale.

2. Prototype et NPI (Nouvelle Introduction de Produit)

- Scénario : Première série d'une nouvelle carte CPU PLC.

- Recommandation : Utiliser le test par sondes mobiles (FPT) au lieu d'un banc de test ICT fixe.

- Compromis : Coût d'outillage nul, mais temps de test par carte très lent.

- Pourquoi : Les modifications de conception sont fréquentes. Le FPT permet de mettre à jour les points de test dans le logiciel sans avoir à reconstruire un banc de test physique.

3. Conceptions à interconnexion haute densité (HDI)

- Scénario : Automates compacts utilisant des micro-vias et des BGA à pas fin.

- Recommandation : Combiner l'ICT avec le Boundary Scan (JTAG) et l'inspection automatisée par rayons X (AXI).

- Compromis : Les sondes ICT ne peuvent pas atteindre chaque réseau dans la technologie PCB HDI. Vous devez vous fier au JTAG pour la logique numérique et aux rayons X pour les joints de soudure BGA.

- Risque : Se fier uniquement à l'ICT ici entraînera une faible couverture (<60 %).

4. Automates critiques pour la sécurité (SIL 3 / SIL 4)

- Scénario : Automates utilisés dans les systèmes d'arrêt d'urgence.

- Recommandation : Test redondant. Couverture ICT à 100 % sur les réseaux de sécurité, suivie d'un FCT à 100 %.

- Compromis : Coût le plus élevé et temps de cycle le plus long.

- Objectif : Le respect des normes de sécurité pour la conception de PCB de PLC nécessite souvent des fentes d'isolation physique, ce qui peut compliquer l'étanchéité sous vide pour les montages. Les montages mécaniques à pression sont préférés ici.

5. Contrôleurs industriels haute tension

- Scénario : Automates programmables (PLC) gérant directement des entrées 220V/480V.

- Recommandation : TIC sélectif. Ne pas sonder directement les réseaux haute tension si le testeur ne peut pas gérer la décharge potentielle.

- Compromis : Couverture réduite sur les entrées d'alimentation pour protéger l'équipement de test.

- Atténuation : Utiliser l'inspection optique automatique (AOI) pour la section haute tension et le TIC pour la logique basse tension.

6. Cartes revêtues (revêtement conforme)

- Scénario : Automates programmables (PLC) destinés à des environnements humides ou corrosifs.

- Recommandation : Tester avant le revêtement. Si un test après revêtement est nécessaire, utiliser des pointes en caoutchouc conductrices ou un masquage spécialisé.

- Compromis : Le masquage ajoute du travail. Les sondes perforantes peuvent endommager le revêtement, compromettant la protection contre l'humidité.

De la conception à la fabrication (points de contrôle de l'implémentation)

La mise en œuvre réussie du TIC est un processus linéaire qui commence bien avant la finalisation du routage du PCB.

Pour garantir une couverture TIC élevée en usine pour les PLC, les concepteurs doivent suivre un flux de travail strict de conception pour le test (DFT). L'ajout de points de test sur un routage fini est une recette pour des problèmes d'intégrité du signal et une faible couverture.

- Phase Schématique - Priorisation des Nets: Identifier les nets critiques (alimentation, réinitialisation, horloges, bus de communication). Les marquer comme "À Tester Impérativement" dans le schéma.

- Phase de Layout - Placement des Points de Test: Placer les points de test (TP) sur la face inférieure du PCB chaque fois que possible. Les montages unilatéraux sont significativement moins chers et plus fiables que les montages bilatéraux.

- Alignement sur la Grille: Aligner les TP sur une grille de 2,54 mm (100 mil) ou 1,27 mm (50 mil). Les points hors grille nécessitent un perçage personnalisé coûteux pour le montage.

- Géométrie des TP: Utiliser un diamètre de pad minimum de 0,8 mm à 1,0 mm pour les sondes standard. Des pads plus petits (0,5 mm) nécessitent des sondes coûteuses et fragiles.

- Règles de Dégagement: Maintenir un dégagement d'au moins 1,5 mm entre les points de test et les corps des composants pour éviter que la tête de la sonde ne heurte le composant.

- Considérations CEM: Lors de la gestion du zonage CEM et de la mise à la terre pour PLC, assurez-vous que les points de test sur les lignes à haute vitesse n'agissent pas comme des antennes. Utilisez des points de test "sans stub" ou couvrez-les avec un blindage de masse si nécessaire.

- Trous de Positionnement: Inclure au moins deux trous de positionnement non plaqués (3mm+) dans les coins opposés. Ceux-ci alignent le PCB avec le montage. Sans eux, un sondage précis est impossible.

- Génération Gerber: Exporter un fichier spécifique "Point de Test" ou une netlist IPC-356. Ne comptez pas sur le fabricant pour deviner quels pads sont destinés aux tests.

- Fabrication du Montage: Envoyer les données à l'entreprise de montage 2-3 semaines avant la fabrication du PCB.

- Débogage : Le premier passage produit généralement de fausses défaillances. Ajustez les tolérances logicielles (par exemple, la variance des résistances) plutôt que de modifier physiquement la carte.

- Test de jauge de contrainte : Avant la production en série, mesurez la contrainte mécanique que le montage applique au PCB. Une flexion excessive peut fissurer les condensateurs céramiques.

- Documentation : Créez un "Rapport de couverture" détaillant exactement quels réseaux sont testés et lesquels sont ignorés. C'est vital pour le dépannage futur.

Pour des spécifications détaillées sur les exigences de disposition, consultez nos directives DFM.

Erreurs courantes (et l'approche correcte)

Même les ingénieurs expérimentés tombent dans des pièges qui réduisent la couverture ou augmentent les coûts de fabrication.

Éviter ces pièges garantit que votre stratégie de couverture ICT d'usine pour PLC est efficace et sûre.

- Erreur : Placer des points de test sous des composants BGA ou à profil bas.

- Correction : Les points de test doivent être accessibles. Si un réseau n'est accessible que sous un BGA, déportez-le vers un via ou un pad dédié.

- Erreur : Compter sur le "Via-in-Pad" pour le sondage.

- Correction : Le sondage des vias plaqués peut provoquer des "fissures en barillet" ou un contact peu fiable en raison de vides de soudure. Utilisez toujours un pad de test plat et solide.

- Erreur : Ignorer les composants hauts.

- Correction : Des condensateurs ou transformateurs hauts sur la face inférieure empêchent la carte de reposer à plat sur le support. Gardez la face inférieure relativement plate ou créez des zones d'exclusion pour les composants hauts.

- Erreur : Supposer qu'une couverture à 100 % est nécessaire.

- Correction : Chercher à obtenir les derniers 5 % de couverture (généralement des condensateurs de découplage ou des résistances de tirage) peut doubler le coût du support. Acceptez une couverture inférieure sur les composants passifs non critiques si le contrôle du processus est bon.

- Erreur : Oublier la routine de "décharge".

- Correction : Les grands condensateurs des automates programmables industriels (API) stockent de l'énergie. Le support ICT doit disposer d'un circuit de décharge pour éviter de griller les sondes du testeur au contact.

- Erreur : Utiliser un masque de soudure sur les points de test.

- Correction : Les points de test doivent être ouverts dans le masque. Les sondes ne peuvent pas pénétrer le masque de soudure de manière fiable sans endommager la pointe ou la carte.

- Erreur : Négliger la densité des sondes.

- Correction : Trop de sondes dans une petite zone (haute densité) crée une pression ascendante massive, pouvant déformer la carte. Répartissez les points de test uniformément.

- Erreur : Négliger les normes de fabrication de PCB de contrôle industriel.

- Correction : Les cartes industrielles ont un cuivre plus épais et des profils thermiques différents. Assurez-vous que les paramètres de test tiennent compte de la capacité de transport de courant plus élevée des pistes.

Questions fréquentes (FAQ)

Q : Quel est le coût typique d'un support ICT pour API ? A: Un banc de test standard à "lit de clous" coûte généralement entre 2 000 et 6 000 dollars, selon le nombre de points de test et s'il est simple ou double face.

Q: Le TIC peut-il tester le logiciel sur l'API? R: Généralement, non. Le TIC teste le matériel (physique). Cependant, certains systèmes TIC avancés peuvent effectuer une "Programmation Flash" pour charger le bootloader initial, ce qui constitue un pont vers le test logiciel.

Q: En quoi le TIC diffère-t-il du test à sondes mobiles? R: Le TIC utilise un dispositif fixe pour tester tous les points simultanément (rapide, coût d'installation élevé). Le test à sondes mobiles utilise des bras robotiques mobiles pour tester les points séquentiellement (lent, coût d'installation nul). Le TIC est destiné à la production en volume; le test à sondes mobiles est destiné aux prototypes.

Q: Quel est l'espacement minimum entre les points de test? R: Pour les sondes standard (100 mil), maintenez 2,54 mm centre à centre. Pour un pas fin (50 mil), vous pouvez descendre à 1,27 mm, mais le coût du dispositif augmente et la durabilité diminue.

Q: Le TIC endommage-t-il le PCB? R: Il laisse de petites "marques de contact" (petites dépressions) sur les pastilles de test. C'est normal et acceptable. Cependant, une pression excessive peut fissurer les joints de soudure, c'est pourquoi un test par jauges de contrainte est requis.

Q: Puis-je utiliser des vias comme points de test? R: Ce n'est pas recommandé. Les vias sont souvent masquées par le vernis épargne. Même si elles sont ouvertes, elles sont irrégulières. Il est préférable d'ajouter une pastille de test dédiée connectée au via.

Q: Comment gérer les points de test pour les paires différentielles haute vitesse? R: L'ajout d'un point de test crée un "moignon" qui peut réfléchir les signaux. Pour les bus de communication PLC à très haute vitesse, utilisez la simulation pour vous assurer que le point de test ne dégrade pas l'intégrité du signal, ou testez ces lignes via le balayage de frontière (boundary scan) à la place.

Q: Pourquoi mon rapport de couverture affiche-t-il un faible pourcentage ? R: Cela arrive souvent si vous avez de nombreux condensateurs parallèles (le testeur les voit comme un seul grand condensateur) ou si vous avez de nombreux réseaux physiquement inaccessibles (par exemple, à l'intérieur d'un BGA sans fan-out).

Q: Ai-je besoin de l'ICT si j'ai l'AOI (Inspection Optique Automatisée) ? R: Oui. L'AOI vérifie uniquement si la pièce semble correcte. Elle ne peut pas dire si une résistance a la mauvaise valeur, si une puce est défectueuse, ou s'il y a une soudure froide sous un composant.

Q: Quelles données APTPCB a-t-il besoin pour établir un devis ICT ? R: Nous avons besoin des fichiers Gerber, de la BOM (Bill of Materials), du fichier XY Pick and Place et de la Netlist électrique (format IPC-356).

Pages et outils associés

- Services de test ICT: Explorez nos capacités spécifiques concernant le matériel et le logiciel de test in-situ.

- PCB de contrôle industriel: Découvrez les exigences spécifiques en matière de matériaux et de fabrication pour l'électronique industrielle.

- Directives DFM: Téléchargez notre liste de contrôle pour vous assurer que votre conception est prête pour les tests de production de masse.

Glossaire (termes clés)

| Terme | Définition |

|---|---|

| Lit à clous | Un dispositif ICT traditionnel contenant des centaines de sondes à ressort qui contactent simultanément le PCB. |

| DFT (Design for Test) | La pratique d'ingénierie consistant à concevoir une disposition de PCB spécifiquement pour faciliter un test facile et complet. |

| DUT (Device Under Test) | L'assemblage PCB spécifique actuellement placé dans le banc de test. |

| Banc de test | L'interface mécanique (matériel personnalisé) qui maintient le PCB et aligne les sondes sur les points de test. |

| Netlist | Un fichier texte décrivant la connectivité électrique du PCB, définissant quels broches de composants sont connectées à quels nets. |

| Pogo Pin | Une sonde à ressort utilisée dans les bancs de test pour établir un contact électrique avec les pastilles du PCB. |

| IPC-356 | Le format de fichier standard utilisé pour communiquer les coordonnées des points de test et les informations de netlist au fabricant. |

| Boundary Scan (JTAG) | Une méthode pour tester les interconnexions sur des CI complexes (comme les FPGA) sans sondes physiques, en utilisant une interface série. |

| Marque de témoin | La petite indentation laissée sur une pastille de soudure par la sonde de test ; preuve que le point a été testé. |

| Jauge de contrainte | Un capteur utilisé pour mesurer la flexion physique ou la contrainte appliquée au PCB pendant la compression sous vide du banc de test. |

| Faux échec | Un résultat de test indiquant un défaut alors que la carte est en fait bonne, généralement causé par un mauvais contact de la sonde ou des tolérances serrées. |

| Guard Trace | Une technique en TIC où les réseaux environnants sont portés à une tension spécifique pour isoler le composant mesuré. |

Conclusion finale (prochaines étapes)

Atteindre une couverture TIC d'usine élevée pour les PLC n'est pas une réflexion après coup ; c'est une décision stratégique qui a un impact sur la sécurité et la fiabilité des systèmes industriels. En comprenant les métriques PCOLA/SOQ, en sélectionnant la bonne stratégie de fixation et en adhérant à des règles DFT strictes, vous vous assurez que chaque PLC quittant la ligne est prêt pour la dure réalité de l'atelier.

Pour faire avancer votre projet PLC, APTPCB recommande une revue DFM complète avant de finaliser votre conception. Lors de la demande de devis, veuillez fournir :

- Fichiers Gerber (y compris une couche de points de test dédiée si disponible).

- BOM (nomenclature) avec les numéros de pièces du fabricant.

- Netlist (format IPC-356).

- Schémas (PDF) pour référence de débogage.

- Exigences de test spécifiques (par exemple, "Doit tester 100% des circuits de relais de sécurité").

Des tests de haute qualité sont la police d'assurance pour la réputation de votre marque. Commencez votre parcours de validation avec les bonnes données et le bon partenaire.