Définition, périmètre et public visé

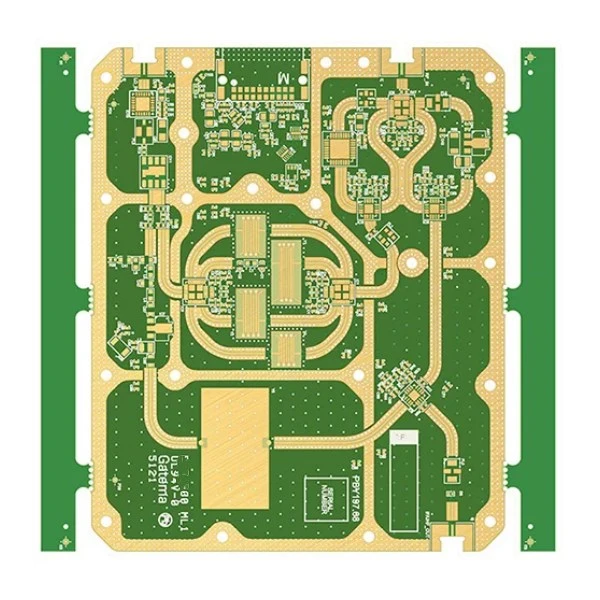

Le contrôle d’impédance des PCB d’étage de puissance GaN désigne la maîtrise précise des dimensions de pistes, des empilages de couches et des matériaux diélectriques afin de préserver l’intégrité du signal et de réduire l’inductance parasite dans les circuits en nitrure de gallium (GaN). Contrairement aux conceptions à base de silicium, les composants GaN commutent à des vitesses extrêmement élevées, avec des dv/dt et di/dt très forts. Sans contrôle d’impédance strict, ces fronts de commutation rapides provoquent surtensions, oscillations et interférences électromagnétiques (EMI), au point d’endommager le composant ou de faire échouer les essais réglementaires.

Ce guide s’adresse aux responsables engineering et aux acheteurs techniques qui font évoluer leurs conceptions de MOSFET silicium standard vers la technologie GaN. Il se concentre sur la réalité industrielle de fabrication de ces cartes. Vous n’avez pas besoin d’être physicien pour l’utiliser ; vous devez surtout être décideur et vouloir sécuriser une chaîne d’approvisionnement fiable.

Le périmètre couvre l’interface critique entre la conception de PCB d’étage de puissance GaN et leur fabrication. Nous expliquons comment spécifier des exigences réellement fabricables, comment valider les résultats et comment éviter les pièges courants côté achats. APTPCB (APTPCB PCB Factory) a élaboré ce guide pour combler l’écart entre simulation théorique et production physique.

Quand utiliser cette approche, et quand l’éviter

Bien cadrer les exigences propres au GaN permet de savoir si votre projet justifie réellement le surcoût lié à un contrôle d’impédance avancé ou si une fabrication standard suffit.

Utilisez un contrôle d’impédance strict pour un PCB d’étage de puissance GaN lorsque :

- la fréquence de commutation dépasse 500 kHz : à ces vitesses, l’inductance parasite dans la boucle de grille devient une source critique de défaillance.

- la densité de puissance est élevée : des applications comme les alimentations de serveurs ou les chargeurs embarqués pour véhicules électriques exigent des techniques HDI (High Density Interconnect) avec impédance contrôlée.

- les temps de montée sont rapides (<10ns) : si vos transistors GaN commutent en nanosecondes, les pistes du PCB se comportent comme des lignes de transmission et nécessitent une impédance adaptée pour éviter les réflexions.

- vous réalisez des amplificateurs de puissance RF : en RF, le GaN est courant, et l’adaptation d’impédance est indispensable pour conserver un transfert de puissance efficace.

Une approche standard est préférable lorsque :

- vous restez sur des conceptions silicium existantes : avec des Si-MOSFET standard commutant sous 100 kHz, des tolérances de +/- 10% sont généralement suffisantes.

- vous traitez des circuits auxiliaires lents : la logique de commande ou les rails d’alimentation auxiliaires d’une même carte n’ont pas toujours besoin des matériaux coûteux imposés à l’étage de puissance principal.

- vous fabriquez un prototype de validation mécanique : si l’objectif se limite à vérifier encombrement et forme, vous pouvez éviter les essais d’impédance onéreux pour gagner du temps.

Spécifications à définir (matériaux, empilage, tolérances)

Dès lors que votre projet exige une fabrication hautes performances, vous devez fixer des spécifications claires pour aligner l’équipe de conception et le fabricant.

- Choix du matériau diélectrique : spécifiez des matériaux présentant une constante diélectrique (Dk) stable et un faible facteur de pertes (Df) à haute fréquence. Les choix courants sont le FR4 à Tg élevée pour les fréquences plus basses, ou des stratifiés Rogers/Isola pour les applications GaN de classe RF.

- Symétrie de l’empilage : définissez un empilage équilibré pour limiter le gauchissement. En GaN, la distance entre la couche supérieure (composants) et le premier plan de référence interne (GND) doit être minimale afin de réduire l’inductance de boucle.

- Tolérance d’impédance : passez de la tolérance standard de +/- 10% à +/- 5% ou +/- 7% pour les pistes critiques de commande de grille et de boucle de puissance.

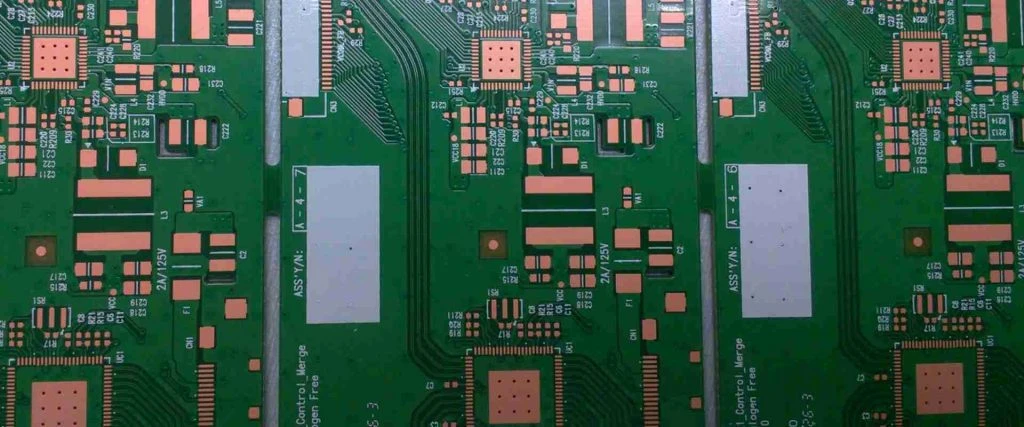

- Poids de cuivre : précisez-le avec soin. Un cuivre épais (2oz+) aide la gestion thermique, mais complique la gravure de lignes fines nécessaire au contrôle d’impédance.

- Largeur et espacement des pistes : définissez les minima en fonction du poids de cuivre. Pour 1oz, 4mil/4mil est courant ; pour 2oz, 6mil/6mil est plus sûr.

- Types de vias : indiquez si des vias borgnes ou enterrés sont requis. Les conceptions GaN utilisent souvent des vias-in-pad métallisés et rebouchés (POFV) pour raccourcir les chemins inductifs sous le pad thermique du composant.

- Finition de surface : ENIG (Electroless Nickel Immersion Gold) ou ENEPIG est préférable au HASL. La planéité d’ENIG est essentielle pour positionner précisément de petits boîtiers GaN tels que CSP ou QFN.

- Masque de soudure : spécifiez un masque LPI (Liquid Photoimageable). Son épaisseur influence l’impédance ; le fabricant doit donc intégrer cet effet dans ses calculs.

- Résistance au pelage : les composants GaN montent fortement en température. Vérifiez que le stratifié offre une forte résistance d’adhérence du cuivre afin d’éviter le délaminage sous cyclage thermique.

- Style de tissage du verre : demandez du "spread glass" ou des styles de tissage plus serrés, comme 1067 ou 1080, afin de réduire l’effet de tissage susceptible de créer du skew sur les paires différentielles rapides.

- Exigences de propreté : la contamination ionique doit être strictement maîtrisée pour éviter la croissance dendritique sous champ électrique élevé.

- Documentation : exigez un rapport de contrôle d’impédance joint à l’expédition, avec les mesures TDR comparées aux fichiers de conception.

Risques de fabrication (causes racines et prévention)

Même avec des spécifications parfaites, le procédé physique de fabrication introduit des variables susceptibles de perturber le contrôle d’impédance des PCB d’étage de puissance GaN. Identifier ces risques tôt permet d’éviter le rebut.

Risque : variation du facteur de gravure

- Cause racine : plus le cuivre est épais, plus l’agent de gravure attaque le haut de la piste plus vite que le bas, ce qui crée un profil trapézoïdal.

- Détection : analyse microsection.

- Prévention : APTPCB applique des facteurs de compensation de gravure aux données Gerber avant production. Les concepteurs doivent prévoir de légers ajustements de largeur.

Risque : variation de l’épaisseur diélectrique

- Cause racine : l’écoulement du prepreg pendant la stratification peut varier, ce qui modifie la distance entre la piste et le plan de référence.

- Détection : les essais TDR mettent en évidence des discontinuités d’impédance.

- Prévention : utilisez du cuivre d’équilibrage (thieving) dans les zones vides pour uniformiser la pression à la stratification et garantir une épaisseur régulière.

Risque : erreurs de registration (désalignement des couches)

- Cause racine : tolérances mécaniques au perçage et à l’alignement en stratification.

- Détection : inspection RX ou coupons de vérification de perçage.

- Prévention : utilisez le Laser Direct Imaging (LDI) pour une registration plus serrée et ajoutez des mires d’alignement spécifiques sur les couches critiques.

Risque : variation d’épaisseur du masque de soudure

- Cause racine : une application irrégulière du masque de soudure modifie la constante diélectrique effective autour de la piste.

- Détection : inspection visuelle et TDR.

- Prévention : privilégiez des procédés d’enduction par pulvérisation ou rideau de haute qualité ; tenez compte de l’effet du masque dès le calcul initial de l’empilage.

Risque : fiabilité des vias sous contrainte thermique

- Cause racine : les dispositifs GaN génèrent une chaleur concentrée. L’expansion en axe Z du PCB peut fissurer la métallisation des vias.

- Détection : essai de choc thermique.

- Prévention : utilisez des matériaux à Tg élevée (Tg > 170°C) et garantissez une épaisseur de métallisation suffisante dans les fûts de vias, en moyenne 25µm.

Risque : manque de résine

- Cause racine : les conceptions à cuivre fort exigent davantage de résine pour remplir les vides entre pistes. Si le prepreg n’en contient pas assez, des cavités apparaissent.

- Détection : essai diélectrique haute tension ou microsection.

- Prévention : choisissez des prepregs à forte teneur en résine pour les couches adjacentes au cuivre épais.

Risque : oxydation de la finition de surface

- Cause racine : mauvais stockage ou mauvaise manipulation d’une finition ENIG.

- Détection : essai de brasabilité.

- Prévention : emballage sous vide avec dessiccant et cartes indicatrices d’humidité, plus un suivi strict de la durée de vie en stock.

Risque : absorption d’humidité

- Cause racine : les matériaux PCB absorbent l’humidité de l’air, ce qui augmente Dk et peut entraîner du délaminage au refusion.

- Détection : pesée ou étuvage.

- Prévention : faites sécher les cartes avant assemblage et stockez-les dans des sachets barrières à l’humidité (MBB).

Validation et acceptation (essais et critères de réussite)

Pour s’assurer que les risques de fabrication sont bien maîtrisés, un plan de validation robuste doit être exécuté avant d’accepter le lot de PCB d’étage de puissance GaN.

Objectif : vérifier la précision d’impédance

- Méthode : réflectométrie temporelle (TDR) sur coupons de test ou sur cartes réelles.

- Critère d’acceptation : l’impédance mesurée doit rester dans la tolérance spécifiée, par exemple 50 ohms +/- 5%.

Objectif : vérifier la construction de l’empilage

- Méthode : microsection (analyse en coupe).

- Critère d’acceptation : les épaisseurs diélectriques et les poids de cuivre doivent correspondre au dessin d’empilage approuvé à +/- 10% près.

Objectif : vérifier l’isolation

- Méthode : essai Hi-Pot (High Potential).

- Critère d’acceptation : aucun claquage ni courant de fuite au-delà de la limite, par exemple <1mA, à la tension de test spécifiée.

Objectif : vérifier la brasabilité

- Méthode : essai de flottation de soudure ou test de balance de mouillage.

- Critère d’acceptation : >95% de la surface du pad doit être recouverte d’un dépôt de soudure lisse et continu.

Objectif : vérifier la tenue thermique

- Méthode : Interconnect Stress Test (IST) ou choc thermique (-40°C à +125°C).

- Critère d’acceptation : la variation de résistance des vias en chaîne doit rester <10% après le nombre de cycles spécifié.

Objectif : vérifier la propreté

- Méthode : essai de contamination ionique (test ROSE).

- Critère d’acceptation : le niveau de contamination doit rester inférieur à 1,56 µg/cm² équivalent NaCl, ou au niveau exigé par la classe IPC-6012.

Objectif : vérifier la précision dimensionnelle

- Méthode : CMM (Coordinate Measuring Machine) ou inspection optique.

- Critère d’acceptation : contour de carte, positions des trous et dimensions des lumières doivent respecter les tolérances du plan mécanique.

Objectif : vérifier la qualité du placage

- Méthode : fluorescence X (XRF) pour mesurer l’épaisseur de finition de surface.

- Critère d’acceptation : épaisseur d’or ENIG 2-5µin ; épaisseur de nickel 120-240µin.

Check-list de qualification fournisseur (RFQ, audit, traçabilité)

Utilisez cette check-list pour évaluer les partenaires potentiels en fabrication et assemblage de PCB d’étage de puissance GaN.

Groupe 1 : éléments RFQ (ce que vous envoyez)

- Fichiers Gerber (RS-274X ou X2) avec nommage clair des couches.

- Plan de fabrication précisant la classe IPC (classe 2 ou 3).

- Schéma d’empilage avec valeurs d’impédance cibles et couches de référence.

- Exigences de fiches matière (Tg, Dk, Df, CTI).

- Tableau de perçage distinguant trous métallisés et non métallisés.

- Tableau d’impédance reliant largeur de piste, couche et valeur cible en ohms.

- Exigences de panélisation, si nécessaires pour l’assemblage.

- Notes spécifiques sur les vias-in-pad ou vias remplis.

Groupe 2 : preuves de capacité (ce qu’ils doivent fournir)

- Liste d’équipements montrant la capacité LDI (Laser Direct Imaging).

- Exemples de rapports TDR issus de précédents projets haut débit.

- Certificat UL couvrant l’empilage matière demandé.

- Rapport DFM démontrant l’examen de vos fichiers spécifiques.

- Preuve de maîtrise simultanée du cuivre fort et du fine pitch sur une même carte.

- Certification ISO 9001 et IATF 16949, si l’application est automobile.

Groupe 3 : système qualité et traçabilité

- Sérialisent-ils chaque carte individuellement ou uniquement les panneaux ?

- Peuvent-ils tracer les lots de matières premières, du stratifié et de la feuille de cuivre jusqu’au PCB fini ?

- Une AOI (Automated Optical Inspection) est-elle réalisée sur chaque couche interne ?

- Réalisent-ils un test électrique à 100% par Flying Probe ou lit à clous ?

- Disposent-ils d’une salle propre dédiée à l’exposition et à la stratification ?

- Quelle est leur procédure de traitement des non-conformités (MRB) ?

Groupe 4 : gestion des changements et livraison

- Ont-ils un processus formel de PCN (Product Change Notification) ?

- Gèlent-ils l’empilage et la marque matière après validation du prototype ?

- Quel est le délai standard pour ce niveau technologique ?

- Proposent-ils des options quick-turn pour la NPI (New Product Introduction) ?

- L’emballage est-il compatible ESD et maîtrisé contre l’humidité ?

- Fournissent-ils un Certificate of Conformance (CoC) avec chaque expédition ?

Aide à la décision (arbitrages et règles de choix)

Choisir la bonne approche de contrôle d’impédance des PCB d’étage de puissance GaN revient à arbitrer entre performance, coût et fabricabilité.

- Si vous privilégiez la vitesse de commutation maximale (>1 MHz) : choisissez des matériaux Rogers ou haut débit plutôt que du FR4. Leur plus faible facteur de pertes justifie un coût matière 2 à 3 fois plus élevé pour éviter la dégradation du signal.

- Si vous privilégiez la gestion thermique : choisissez du cuivre fort (3oz+) ou des PCB à noyau métallique. En contrepartie, admettez que les tolérances d’impédance puissent devoir s’assouplir à +/- 10% en raison des difficultés de gravure sur cuivre épais.

- Si vous privilégiez la densité et le faible encombrement : choisissez du HDI avec via-in-pad. Cette solution réduit fortement l’inductance de boucle, mais augmente le coût carte de 30-50% par rapport à une technologie traversante.

- Si vous privilégiez le coût : choisissez du FR4 standard à Tg élevée avec un empilage standard. C’est viable pour des applications GaN <500kHz, à condition de soigner le routage pour compenser les limites du matériau.

- Si vous privilégiez la fiabilité pour l’automobile ou l’industrie : choisissez une fabrication IPC Class 3. Ce niveau impose des critères plus stricts sur le placage et l’inspection, ce qui aide la carte à survivre aux cyclages thermiques sévères.

- Si vous privilégiez l’intégrité du signal avant la puissance : choisissez des diélectriques plus minces. Des couches fines, par exemple 3-4 mil de prepreg, augmentent le couplage et réduisent la diaphonie, mais restent plus délicates à fabriquer.

FAQ (coût, délai, fichiers DFM, essais)

Quel est l’impact coût du contrôle d’impédance sur un PCB d’étage de puissance GaN ? Un contrôle d’impédance strict augmente généralement le coût unitaire du PCB de 10-20%. Cela couvre les coupons de test TDR, la planification spécialisée de l’empilage et des rendements de fabrication plus faibles dus à des tolérances plus serrées.

Quel est l’impact sur le délai par rapport à une carte standard ? Prévoyez 2-3 jours supplémentaires par rapport au délai standard. L’équipe engineering a besoin de plus de temps pour traiter les EQ (Engineering Questions) liées à l’empilage, et les tests TDR ajoutent une étape au contrôle qualité final.

Quels fichiers DFM faut-il fournir précisément ? Au-delà des Gerber standard, vous devriez fournir si possible un fichier IPC-2581 ou ODB++, ou à défaut un dessin détaillé de l’empilage. Indiquez explicitement quelles pistes sont "impedance critical" pour que l’ingénieur CAM sache quelles lignes mesurer.

Puis-je utiliser du FR4 standard pour le contrôle d’impédance d’un étage de puissance GaN ? Oui, pour des applications GaN à plus basse fréquence, sous 1 MHz. Vous devez toutefois utiliser du FR4 "High-Tg" avec un Tg > 170°C pour résister à la contrainte thermique. À fréquence plus élevée, le FR4 standard devient trop dissipatif.

Quels critères d’acceptation s’appliquent aux essais TDR sur les cartes GaN ? Le critère standard est de +/- 10% autour de l’impédance cible. Pour du GaN hautes performances, vous pouvez demander +/- 5%, mais cela peut réduire le nombre de fournisseurs capables et augmenter le coût.

Comment l’épaisseur de cuivre influence-t-elle le contrôle d’impédance ? Un cuivre plus épais (2oz+) rend la gravure précise de lignes fines plus difficile, ce qui accroît la dispersion d’impédance. Si vous avez besoin à la fois d’un courant élevé et d’une impédance serrée, envisagez des poids de cuivre différents selon les couches.

Pourquoi recommande-t-on le via-in-pad pour la conception d’un PCB d’étage de puissance GaN ? Le via-in-pad place le via directement sous le pad de soudure du composant. Cela crée le chemin le plus court possible vers le plan de masse et réduit l’inductance parasite, qui pénalise fortement les performances GaN.

Dois-je tester 100% des cartes en impédance ? En général, non. Un contrôle TDR devient destructif s’il est réalisé directement sur la carte, il est donc effectué sur un coupon de test en bord de panneau. En pratique, on contrôle habituellement un coupon par panneau ou par lot pour valider le procédé.

Pages et outils associés

- Fabrication de PCB haute fréquence – Découvrez les options matière et les capacités adaptées aux applications de commutation rapide comme le GaN.

- Outil de calcul d’impédance – Utilisez cet outil pour estimer largeurs de pistes et espacements avant de figer votre routage.

- Capacités HDI – Découvrez la technologie High Density Interconnect, souvent nécessaire pour réduire l’inductance de boucle dans les conceptions GaN.

- Directives DFM – Vérifiez les règles de conception afin que votre carte à impédance contrôlée puisse être fabriquée sans retard.

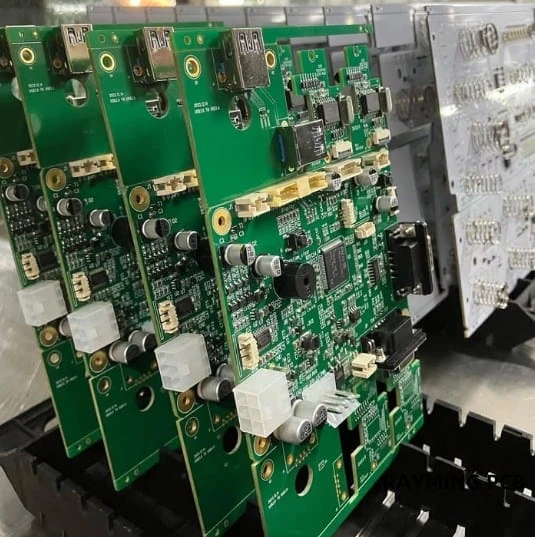

- Services d’assemblage PCB – Comprenez comment nous assemblons les composants GaN à pas fin après la fabrication.

Demander un devis (revue DFM + tarification)

Prêt à passer du design à la production ? Transmettez vos données à APTPCB pour une revue DFM complète et une offre de prix. Nous comparons votre empilage à notre stock matière et validons vos calculs d’impédance avant facturation.

Merci de fournir les éléments suivants pour obtenir un devis précis :

- Fichiers Gerber : RS-274X ou ODB++.

- Dessin d’empilage : avec type de matériau et impédance cible.

- Volume : quantité prototype versus volume de série.

- Exigences d’essais : précisez si des rapports TDR ou l’IPC Class 3 sont requis.

Demander un devis et une revue DFM

Conclusion (prochaines étapes)

Déployer avec succès la technologie au nitrure de gallium demande plus que le simple choix du bon transistor ; cela exige une approche globale du contrôle d’impédance des PCB d’étage de puissance GaN. En définissant des exigences serrées sur les matériaux et l’empilage, en comprenant les risques de fabrication et en appliquant un plan de validation rigoureux, vous garantissez un étage de puissance efficace et fiable. Utilisez la check-list fournie pour qualifier vos fournisseurs et vérifier qu’ils peuvent répondre aux exigences sévères des commutations GaN à haute vitesse.