Investir dans le Design for Manufacturability (DFM) et le Design for Testability (DFT) est une décision stratégique qui fait passer le pilotage qualité d’une logique réactive de correction à une logique préventive. Pour les acheteurs et les chefs de produit, comprendre comment réduire les défauts PCBA avec le DFM et le DFT est l’un des moyens les plus efficaces de diminuer le coût total et d’accélérer la mise sur le marché. Ce guide présente les spécifications techniques et les cadres de décision nécessaires pour aligner la conception avec les capacités réelles de fabrication.

Points forts

- Prévention en amont : le DFM détecte avant la production les problèmes de layout qui provoquent ponts de soudure, tombstoning et vides.

- Couverture de test : le DFT garantit qu’un défaut éventuel sera détecté par l’ICT ou le test fonctionnel au lieu de se retrouver sur le terrain.

- Réduction des coûts : corriger un défaut au stade de la conception coûte environ 10x moins cher qu’en assemblage et environ 100x moins cher après livraison.

- Alignement fournisseur : des exigences claires sur le stencil et le profil de refusion sont essentielles pour des composants complexes comme les BGA et les QFN.

Points clés à retenir

Avant d’entrer dans les détails techniques, voici une synthèse de l’effet direct de ces deux approches sur vos coûts et sur la fiabilité du produit.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Objectif principal | Garantir que le produit peut être fabriqué de façon répétable avec un rendement élevé. | Garantir que le produit peut être vérifié rapidement et avec précision. |

| Cible côté défauts | Empêche l’apparition de défauts, par exemple les ponts de soudure. | Détecte les défauts qui apparaissent malgré tout, par exemple les circuits ouverts. |

| Livrable clé | Géométries de pads optimisées, reliefs thermiques, espacements composants. | Points de test, accès JTAG, scan chains. |

| Moteur de ROI | First Pass Yield (FPY) plus élevé, moins de retouches. | Taux de panne terrain plus faible, diagnostic plus rapide. |

Réduire les défauts PCBA avec le DFM et le DFT : périmètre, contexte de décision et critères de réussite

La réduction des défauts ne commence pas sur la ligne d’assemblage, mais dès le schéma et le routage. Quand un acheteur demande comment réduire les défauts PCBA avec le DFM et le DFT, il doit comprendre qu’il achète une capacité de procédé, et non une simple carte standard.

Contexte de décision

Les acheteurs arbitrent souvent entre davantage de temps d’ingénierie au départ et une production plus fluide ensuite. Sauter les revues DFM pour accélérer un prototype conduit fréquemment à des cartes difficiles à fabriquer ou à des taux de rebut élevés lors des volumes série. Le bon niveau d’analyse dépend de la complexité du PCBA. Une carte simple avec de gros passifs peut nécessiter peu de DFM, alors qu’une carte HDI avec BGA exige une revue rigoureuse.

Critères de réussite

Pour vérifier si vos efforts DFM et DFT produisent l’effet attendu, suivez au minimum les indicateurs suivants :

- First Pass Yield (FPY) : pourcentage de cartes qui passent tous les tests sans retouche. Une cible de 98%+ est courante pour un produit mature.

- Couverture de test : pourcentage des nets et composants accessibles par des tests automatisés. Un DFT solide vise 90%+.

- Taux de faux défauts : fréquence à laquelle de bonnes cartes sont rejetées à cause de limites de test mal définies ou de fixtures instables.

- Engineering Change Orders (ECOs) : une baisse des ECO liés à l’assemblage est un bon indicateur de DFM efficace.

Spécifications à définir avant de vous engager

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 (typique), davantage si nécessaire | Influe sur le coût, le rendement et la marge de routage | Stackup + rapport DFM |

| Min trace/space | 4/4 mil (typique) | Influe sur le rendement et le délai | DRC + capacité de fabrication |

| Via strategy | Through vias vs VIPPO vs microvias | Affecte la fiabilité d’assemblage | Microsection + critères IPC |

| Surface finish | ENIG/OSP/HASL | Affecte la soudabilité et la planéité | COC + essais de soudabilité |

| Solder mask | Vert mat (par défaut) | Améliore la lisibilité AOI et réduit le risque de pontage | Essai AOI + enregistrement du masque |

| Test | Flying probe / ICT / FCT | Arbitrage couverture vs coût | Rapport de couverture + plan de fixture |

| Acceptance class | IPC Class 2 / 3 | Définit les limites de défaut acceptables | Notes de plan + rapport d’inspection |

| Lead time | Standard vs expedited | Influe sur le risque planning | Devis + confirmation de capacité |

Pour mettre en place un DFM et un DFT efficaces, certaines exigences doivent impérativement figurer dans le package de données. Dès qu’un point reste ambigu, l’atelier comble le vide par des hypothèses, et c’est une cause majeure de défauts.

1. Exigences de données DFM

Fournissez à votre contract manufacturer (CM) autre chose qu’un simple jeu de Gerber.

- Choix de la classe IPC : précisez explicitement si l’assemblage relève de l’IPC-A-610 Class 2 ou Class 3. Ce choix conditionne les critères de volume de soudure et d’alignement.

- Empreintes composants : exigez une vérification des empreintes par rapport à la Bill of Materials (BOM). Les écarts entre le composant réel et le land pattern sont une cause classique de défaut DFM.

- Stratégie de panelisation : définissez le panel. Une panelisation mal conçue peut provoquer des fissures de contrainte dans les condensateurs céramiques lors du dépanelisage.

- Ponts de masque de soudure : spécifiez une largeur minimale de masque entre pads, typiquement 4 mil, pour éviter les ponts sur les boîtiers à pas fin.

2. Exigences de données DFT

Le DFT est souvent traité trop tard, ce qui conduit à des fixtures bed of nails coûteux incapables d’atteindre les nets critiques.

- Accessibilité des points de test : imposez un point de test sur la face inférieure du PCB pour tous les nets critiques. Cela permet un In-Circuit Test (ICT) sur une seule face, nettement moins coûteux.

- Dégagement autour des points de test : imposez un dégagement minimal, par exemple 50 mil, entre les points de test et les composants hauts pour éviter les collisions de pointes.

- JTAG/Boundary Scan : sur les cartes numériques complexes, assurez-vous que la chaîne JTAG est bien routée et accessible. Cela permet de tester les liaisons entre circuits sans pointes physiques.

- Netlist : fournissez systématiquement une netlist IPC-356. Elle permet au fabricant de comparer la connectivité issue des Gerber à celle du schéma.

Ressources associées

Risques majeurs : causes racines, détection précoce et prévention

Comprendre les défauts typiques permet de prioriser les contrôles DFM. Les cas les plus difficiles se situent souvent sous les composants à terminaisons inférieures comme les QFN (Quad Flat No-lead) et les BGA.

1. Vides sous QFN et BGA

Les vides sont des poches d’air piégées dans la brasure. Un taux de vide trop élevé réduit la conductivité thermique et la tenue mécanique.

- Risque : surchauffe de QFN de puissance à cause d’un transfert thermique insuffisant au travers d’une soudure trop creuse.

- Prévention (DFM) : appliquez les qfn reflow best practices to reduce voids. Cela consiste à fenêtrer l’ouverture de pâte à braser sur le pad thermique. Au lieu d’imprimer un bloc plein qui piège les gaz, on imprime une grille de petites ouvertures avec environ 50-70% de couverture pour laisser s’échapper les volatils pendant la refusion.

2. Défauts de soudure BGA : ponts et opens

Les BGA sont complexes car les joints sont invisibles à l’œil.

- Risque : défaut Head-in-Pillow (HiP), lorsque la bille repose sur la pâte sans coalescence correcte.

- Prévention (DFM/process) : il faut un contrôle strict selon bga voiding control: stencil, reflow, and x-ray criteria.

- Stencil : utilisez des stencils électropolis avec ouvertures trapézoïdales pour assurer une libération propre de la pâte.

- Refusion : optimisez la zone de soak. Si le flux brûle trop tôt, l’oxydation empêche le mouillage.

- Critères RX : définissez clairement les seuils d’acceptation. En IPC Class 2, les vides doivent généralement rester sous 25% de la surface de la bille.

3. Tombstoning

Ce défaut se produit lorsqu’un petit composant passif se redresse sur une extrémité pendant la refusion.

- Cause racine : forces de mouillage déséquilibrées, souvent parce qu’un pad est relié à un grand plan de masse qui agit comme dissipateur, tandis que l’autre pad est sur une piste fine.

- Prévention (DFM) : utilisez des reliefs thermiques sur les pads de masse afin que les deux pads atteignent la température de refusion au même moment.

4. Shadowing

En vague ou en brasage sélectif, les gros composants peuvent masquer les plus petits et empêcher l’onde de brasure d’atteindre correctement leurs broches.

- Prévention (DFM) : appliquez des règles d’espacement dépendantes du sens de passage dans la machine de brasage.

Validation et acceptation : essais et critères de conformité

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| Continuité électrique | Flying probe / fixture | 100% des nets testés, aucun open ni short | Rapport E-test |

| Dimensions critiques | Mesure | Conforme aux tolérances du plan | Enregistrement d’inspection |

| Intégrité de métallisation / remplissage | Microsection | Aucun vide ni fissure au-delà des limites IPC | Photos de microsection |

| Soudabilité | Test de mouillage | Mouillage acceptable, pas de dewetting | Rapport de soudabilité |

| Warpage | Mesure de planéité | Conforme à la spécification, p. ex. ≤0,75% | Relevé de warpage |

| Validation fonctionnelle | FCT | Tous les cas passent, journal archivé | Logs FCT |

Comment prouver que les efforts DFM et DFT ont été efficaces ? Il faut établir un plan de validation cohérent avec vos objectifs de NPI assembly.

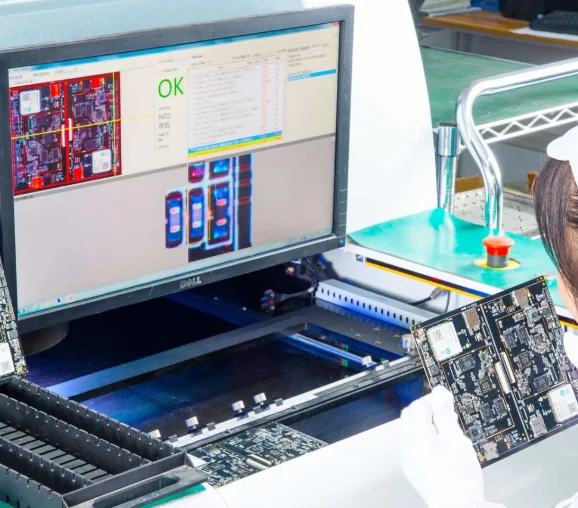

Automated Optical Inspection (AOI)

L’AOI constitue la première ligne de défense. Les caméras vérifient la présence des composants, leur polarité, leur décalage et la qualité des joints.

- Critères de conformité : aucune pièce manquante, repères de polarité alignés, filets de soudure conformes aux critères IPC.

- Limite : l’AOI ne voit pas sous les BGA ni sous les QFN.

X-Ray Inspection (Axi)

L’inspection RX est indispensable pour valider les BGA et les QFN.

- Critères de conformité : les exigences de bga voiding control: stencil, reflow, and x-ray criteria doivent être respectées. Vides <25%, forme de bille cohérente, absence de pontage.

- Application : inspection à 100% sur prototypes, inspection par échantillonnage en production série.

- En savoir plus : Inspection RX

In-Circuit Test (ICT) et Flying Probe

C’est à ce stade que le DFT prend toute sa valeur.

- ICT : utilise un fixture bed of nails pour tester simultanément tous les nets. C’est rapide, mais coûteux en outillage. Il faut donc des points de test prévus dès le DFT.

- Flying Probe : des bras robotisés viennent sonder les points sans fixture. C’est plus lent, mais très adapté au prototype.

- Critères de conformité : toutes les valeurs passives sont dans la tolérance et aucun short ou open n’est présent sur les nets actifs.

Functional Circuit Test (FCT)

Dernière étape de validation : la carte est alimentée et doit réaliser sa fonction réelle.

- Critères de conformité : l’équipement démarre, le firmware se charge et les E/S répondent correctement.

Check-list de qualification fournisseur : RFQ, audit et traçabilité

Si vous choisissez un partenaire pour vous aider à réduire les défauts PCBA avec le DFM et le DFT, utilisez cette check-list.

1. Capacités d’ingénierie

- Le fournisseur réalise-t-il une revue DFM obligatoire avant le tooling ?

- Fournit-il un rapport DFM détaillé, et pas seulement un résultat pass/fail, en signalant des risques comme les acid traps ou les slivers ?

- Est-il capable de proposer des empreintes alternatives pour améliorer le rendement ?

- Consultez les Directives DFM pour le niveau attendu.

2. Maîtrise du process

- Dispose-t-il d’une SPI inline ? La SPI élimine une large part des défauts de dépôt de pâte.

- L’inspection RX est-elle disponible en interne ?

- Sait-il appliquer les qfn reflow best practices to reduce voids, par exemple via refusion sous vide ou optimisation de profil ?

3. Traçabilité et système qualité

- Le site est-il certifié ISO 9001 ou IATF 16949 ?

- La traçabilité descend-elle jusqu’au niveau composant, en reliant des lots précis à des numéros de série précis ?

- Examinez leur Système qualité.

Choisir le bon niveau de DFM et DFT : arbitrages et règles de décision

Toutes les cartes n’exigent pas la même intensité de DFM et de DFT. Les règles suivantes aident à équilibrer coût et risque.

Scénario A : électronique grand public simple à faible coût et grand volume

- Stratégie : concentrer l’effort sur le DFM pour maximiser le rendement et réduire le temps de cycle.

- DFT : minimum. S’appuyer sur l’AOI et sur un échantillonnage fonctionnel.

- Compromis : accepter un taux de panne terrain légèrement plus élevé pour préserver un coût unitaire bas.

Scénario B : médical ou automobile à haute fiabilité et volume moyen

- Stratégie : DFM et DFT poussés.

- DFT : 100% ICT et 100% test fonctionnel.

- Compromis : coûts NRE plus élevés pour les fixtures et le développement de test, mais quasi-absence de défaillances terrain.

- Point spécifique : application stricte de bga voiding control: stencil, reflow, and x-ray criteria.

Scénario C : prototypage rapide

- Stratégie : DFM "léger". Corriger uniquement les points bloquants pour l’assemblage.

- DFT : flying probe, sans coût de fixture.

- Compromis : temps de test unitaire plus élevé, mais délai global plus court.

FAQ : coût, délai, fichiers DFM, matériaux et test

1. Ajouter des exigences DFM/DFT augmente-t-il le prix du devis ? Oui, au départ. Le temps d’ingénierie et les fixtures de test en NRE augmentent le coût initial. En contrepartie, le coût total du projet baisse souvent grâce à une meilleure qualité de passage et à moins de retouches.

2. Quel impact une revue DFM a-t-elle sur le délai ? En général 1 à 2 jours. Une revue DFM sérieuse intervient avant la commande des composants et des matériaux. Ce léger décalage évite souvent des semaines perdues plus tard.

3. Le DFM peut-il corriger un mauvais schéma ? Non. Le DFM garantit que la carte peut être fabriquée, pas que le design électronique fonctionne. Si le schéma est erroné, la carte sera correctement assemblée mais restera défaillante fonctionnellement.

4. Quelle différence entre DFM et DFA ? Le DFM désigne généralement la fabricabilité de la carte nue, comme la gravure ou le perçage. Le DFA concerne l’assemblage, comme les soudures et les dégagements. Dans la pratique, beaucoup d’acteurs utilisent DFM comme terme couvrant les deux.

5. Ai-je besoin de l’ICT si j’ai déjà un test fonctionnel ? Idéalement oui. L’ICT indique quel composant ou quel net est en défaut. Le test fonctionnel indique surtout que la carte ne fonctionne pas. Pour le diagnostic et la réparation, l’ICT est bien plus rapide.

6. En quoi les matériaux influencent-ils le DFM ? Le choix du matériau, par exemple un FR4 High Tg, détermine comment la carte se dilate pendant la refusion. Un mauvais appariement de CTE entre carte et composant est une cause majeure de fatigue des soudures.

7. Quelle est la meilleure façon de transmettre les notes DFM ? Ajoutez un fichier Read Me ou un PDF dans l’archive Gerber. Listez explicitement les exigences particulières, comme "Do not X-out arrays" ou "Mask plug vias at U1".

Demander un devis ou une revue DFM : quoi envoyer

Prêt à optimiser votre PCBA pour la production série ? Envoyez votre package de données pour une revue DFM complète.

Check-list pour la demande de devis :

- Fichiers Gerber (RS-274X) : couches cuivre, masque de soudure, sérigraphie, perçages et couches de pâte.

- Bill of Materials (BOM) : fichier Excel avec Manufacturer Part Numbers (MPN) et repères de référence.

- Fichier centroid (Pick and Place) : coordonnées X-Y et angles de rotation.

- Plans d’assemblage : PDF montrant l’emplacement des composants et les repères de polarité.

- Exigences de test : description de la couverture visée, par exemple ICT, FCT ou burn-in.

Glossaire : termes clés

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability : règles de layout qui réduisent les défauts. | Réduit retouches, retards et coûts cachés. |

| AOI | Automated Optical Inspection utilisée pour détecter les défauts de soudure et d’assemblage. | Améliore la couverture et détecte tôt les dérives. |

| ICT | In-Circuit Test qui contrôle opens, shorts et valeurs électriques. | Test structurel rapide pour les fabrications en volume. |

| FCT | Functional Circuit Test qui alimente la carte et vérifie son comportement. | Valide la fonction réelle en charge. |

| Flying Probe | Test électrique sans fixture, réalisé par pointes mobiles. | Adapté aux prototypes et aux volumes faibles à moyens. |

| Netlist | Définition de connectivité utilisée pour comparer le design au PCB fabriqué. | Détecte opens et shorts avant l’assemblage. |

| Stackup | Construction des couches avec cœurs, prepregs, cuivre et épaisseurs. | Influence impédance, warpage et fiabilité. |

| Impedance | Comportement contrôlé des pistes pour signaux RF ou haut débit, p. ex. 50Ω. | Évite réflexions et problèmes d’intégrité du signal. |

| ENIG | Finition chimique nickel or par immersion. | Bon compromis entre soudabilité et planéité ; surveiller l’épaisseur de nickel. |

| OSP | Finition Organic Solderability Preservative. | Économique, mais plus sensible à la manutention et aux refusions multiples. |

Conclusion : prochaines étapes

Comprendre comment réduire les défauts PCBA avec le DFM et le DFT revient à investir dans la durée de vie du produit et dans la crédibilité de votre marque. En fixant des exigences claires sur le stencil, la refusion et l’accessibilité au test, vous transformez un process opaque en process piloté et prévisible.

Impliquez votre partenaire industriel dès la phase de conception. Une revue conjointe des qfn reflow best practices to reduce voids et de bga voiding control: stencil, reflow, and x-ray criteria vous fera gagner du temps et du budget. Exigez un package de données transparent, validez avec rigueur et choisissez un fournisseur qui traite la qualité comme une responsabilité partagée.