Réponse rapide sur les PCB de serveurs d'inférence (30 secondes)

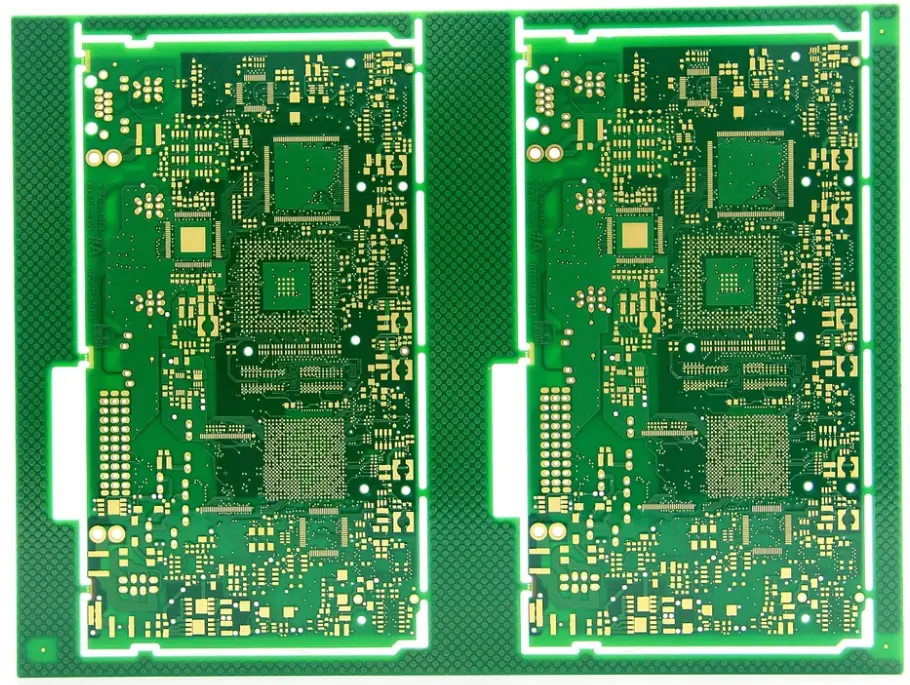

La conception et la fabrication d'un PCB de serveur d'inférence nécessitent d'équilibrer l'intégrité des signaux haute vitesse avec une densité thermique intense. Contrairement aux cartes informatiques à usage général, ces PCB doivent supporter un débit soutenu pour les charges de travail d'IA sans pics de latence causés par la dégradation du signal ou l'étranglement thermique (thermal throttling).

- Le choix des matériaux est critique : Le FR-4 standard est insuffisant pour les vitesses PCIe Gen5/6. Vous devez utiliser des matériaux à très faible perte (ex. Panasonic Megtron 6/7/8 ou Isola Tachyon) pour minimiser la perte d'insertion.

- Le backdrilling (contre-perçage) est obligatoire : Pour réduire la réflexion du signal dans les liaisons à haute vitesse (> 25 Gbps), les stubs de vias doivent être retirés (backdrillés) à moins de 8-10 mils de la couche de signal.

- Cuivre lourd pour la distribution électrique : Les accélérateurs d'inférence consomment un courant important. Les plans d'alimentation nécessitent souvent du cuivre de 2 oz ou 3 oz pour minimiser la chute de tension (IR drop) et gérer la diffusion de la chaleur.

- Contrôle d'impédance strict : Les paires différentielles nécessitent généralement une tolérance de 85 Ω ou 100 Ω ± 5 %. Les écarts provoquent de la gigue (jitter) et la perte de paquets de données dans les flux de traitement de l'IA.

- Stratégie de gestion thermique : Les configurations haute densité dans les formats de châssis 1U ou 2U nécessitent souvent l'intégration de pièces de cuivre (copper coin) ou la technologie VIPPO (Via-in-Pad Plated Over) pour dissiper la chaleur des GPU ou des ASIC.

- Nombre de couches et empilement (Stackup) : La plupart des cartes de serveurs d'inférence vont de 12 à 24 couches pour s'adapter à un routage dense et isoler les signaux haute vitesse entre les plans de masse.

Quand le PCB de serveur d'inférence s'applique (et quand il ne s'applique pas)

Comprendre l'enveloppe opérationnelle spécifique d'un PCB de serveur d'inférence garantit que vous ne sur-concevez pas un contrôleur simple ou ne sous-spécifiez pas un nœud d'IA critique.

Quand utiliser les normes de PCB de serveur d'inférence :

- Déploiement Edge AI/ML : Vous construisez des serveurs destinés à exécuter des modèles pré-entraînés (inférence) pour l'analyse vidéo, le traitement du langage naturel ou le traitement des données de conduite autonome.

- Intégration d'accélérateurs haute vitesse : La carte doit héberger ou se connecter à plusieurs accélérateurs basés sur PCIe (GPU, TPU, FPGA) nécessitant des interfaces PCIe Gen5 ou CXL.

- Nœuds de calcul denses : Vous concevez des facteurs de forme de PCB de serveur 1U ou PCB de serveur 2U où le flux d'air est restreint et où la conductivité thermique du PCB est une voie de refroidissement principale.

- Exigences de faible latence : L'application exige un traitement en temps réel où la gigue du signal ou le bruit d'intégrité de l'alimentation pourrait causer une latence inacceptable (ex. trading financier ou systèmes de sécurité).

- Architectures basées sur ARM : Vous utilisez des conceptions de PCB de serveur ARM à grand nombre de cœurs (comme Ampere Altra) qui nécessitent des impédances spécifiques pour le réseau de distribution électrique (PDN).

Quand les règles de PCB standard s'appliquent à la place :

- Hébergement web à usage général : Les serveurs de base standards gérant le trafic web de base ne nécessitent pas les matériaux coûteux à faible perte nécessaires pour l'inférence de l'IA.

- Nœuds de capteurs IoT : Les dispositifs de collecte de données à basse vitesse n'ont pas besoin de cartes à grand nombre de couches avec contrôle d'impédance.

- Grappes d'entraînement de modèles massifs : Bien que similaires, les serveurs d'"Entraînement" ont souvent des densités de puissance encore plus élevées (kilowatts par carte) et des topologies d'interconnexion différentes (NVLink/Infinity Fabric) par rapport aux nœuds d'inférence standards.

- Contrôleurs industriels existants (Legacy) : Les systèmes fonctionnant sur des fréquences inférieures à 1 GHz ou des vitesses Ethernet standard ne nécessitent pas de backdrilling ou de feuille de cuivre ultra-lisse.

Règles et spécifications des PCB de serveurs d'inférence (paramètres et limites clés)

Le tableau suivant décrit les paramètres de fabrication non négociables pour un PCB de serveur d'inférence de haute fiabilité. APTPCB (APTPCB PCB Factory) utilise ces bases pour s'assurer que les cartes répondent aux niveaux de performance IPC-6012 Classe 3.

| Catégorie de règle | Valeur / Plage recommandée | Pourquoi c'est important | Comment vérifier | Si ignoré (Mode de défaillance) |

|---|---|---|---|---|

| Matériau de base | Faible perte / Très faible perte (Df < 0,005 @ 10GHz) | Prévient l'atténuation du signal sur les longues traces typiques des cartes de serveurs. | Méthode de test IPC-TM-650 ; vérifier la fiche technique du matériau (ex. Megtron 7). | Perte massive de paquets de données ; le système ne parvient pas à se lier aux vitesses Gen5. |

| Nombre de couches | 12 – 24 Couches | Fournit suffisamment de canaux de routage et de blindage de masse pour les voies à haute vitesse. | Revue du diagramme d'empilement (stackup) ; Analyse de section transversale (microsection). | Diaphonie (crosstalk) excessive ; incapacité à router tous les signaux ; défaillances EMI. |

| Rugosité de la feuille de cuivre | HVLP (Hyper Very Low Profile) ou VLP-2 | Le cuivre rugueux agit comme une résistance à hautes fréquences (effet de peau), augmentant les pertes. | Inspection SEM (Microscope électronique à balayage) de la surface de la feuille. | Augmentation de la perte d'insertion ; dégradation de l'intégrité du signal à > 10 GHz. |

| Tolérance d'impédance | ± 5 % (Cible 85 Ω ou 100 Ω) | Correspond à l'impédance de l'émetteur/récepteur pour éviter les réflexions de signal. | Coupons TDR (Réflectométrie temporelle) sur le panneau de production. | Réflexion du signal (ringing) ; ouverture réduite du diagramme de l'œil ; erreurs de données. |

| Profondeur de Backdrilling | Longueur du stub < 10 mils (0,25 mm) | Les longs stubs de vias agissent comme des antennes/condensateurs, causant des résonances et des encoches dans le signal. | Inspection aux rayons X ; Analyse de section transversale. | Pics de "taux d'erreur binaire" (BER) ; des fréquences spécifiques sont complètement bloquées. |

| Rapport d'aspect (Perçage) | 10:1 à 12:1 (Standard) ; jusqu'à 16:1 (Avancé) | Garantit que la solution de placage peut pénétrer et plaquer le canon du via de manière fiable. | Analyse par microsection de l'épaisseur du placage au centre du via. | Circuits ouverts dans les vias (fissures du canon) pendant les cycles thermiques. |

| Épaisseur de placage | > 25 µm (1 mil) en moyenne dans le trou | Fournit une résistance mécanique pour supporter l'expansion thermique des cartes épaisses. | Mesure CMI ou par section transversale. | Fissuration des coins ou fatigue du canon entraînant des défaillances intermittentes. |

| Barrage de masque de soudure (Solder Mask Dam) | Min 3-4 mils (0,075-0,1 mm) | Prévient les ponts de soudure entre les pastilles BGA à pas fin. | AOI (Inspection optique automatisée). | Courts-circuits sous des composants BGA coûteux (GPU/CPU). |

| Gauchissement / Arc et Torsion (Warpage / Bow & Twist) | < 0,5 % (Cible IPC Classe 3) | Les grandes cartes de serveurs (E-ATX) doivent rester planes pour l'assemblage BGA. | Outil de mesure Shadow Moiré. | Joints ouverts BGA (défauts "head-in-pillow") ; échec de l'assemblage. |

| Transition vitreuse (Tg) | Haute Tg (> 170 °C) | Prévient le ramollissement du matériau et l'expansion sur l'axe Z pendant la refusion et le fonctionnement. | DSC (Calorimétrie différentielle à balayage). | Cratérisation des pastilles (pad cratering) ; délaminage lors de l'assemblage ou d'un fonctionnement à forte charge. |

| Résistance CAF | Matériaux anti-CAF requis | Une polarisation de tension élevée dans les couches d'alimentation des serveurs peut provoquer la croissance de filaments conducteurs. | Test SIR (Résistance d'isolement de surface) ; coupons de test CAF. | Courts-circuits catastrophiques se développant des mois après le déploiement. |

| Via-in-Pad | VIPPO (Plated Over) pour les BGA | Permet de sortir du routage des BGA à pas fin (0,8 mm ou moins) sans traces en "os de chien" (dog-bone). | Inspection visuelle ; Section transversale. | Vides de soudure dans les joints BGA s'ils ne sont pas bouchés/plaqués correctement. |

Étapes de mise en œuvre du PCB de serveur d'inférence (points de contrôle du processus)

Passer d'un schéma à un PCB de serveur d'inférence physique nécessite un flux de travail discipliné. Chaque étape ci-dessous comprend une action spécifique et un contrôle d'acceptation pour éviter des relances (respins) coûteuses.

Définition de l'empilement (Stackup) et sélection des matériaux

- Action : Définissez l'empilement des couches (ex. 16 couches) à l'aide d'une bibliothèque de matériaux de PCB haute vitesse. Équilibrez le poids du cuivre (puissance) avec l'épaisseur du diélectrique (impédance).

- Paramètre : Assurez la symétrie pour éviter le gauchissement. Sélectionnez les styles de verre préimprégné (ex. 1035, 1078) pour minimiser l'effet de tissage de la fibre (fiber weave effect).

- Contrôle : Exécutez une simulation avec un solveur d'impédance. Confirmez que les largeurs de ligne sont fabricables (ex. > 3,5 mils).

Planification (Floorplanning) et simulation thermique

- Action : Placez les composants de forte puissance (CPU, accélérateurs, VRM) pour optimiser le flux d'air dans le châssis 1U/2U.

- Paramètre : Gardez les émetteurs-récepteurs haute vitesse près des connecteurs de bord ou des interfaces de fond de panier (backplane) pour raccourcir les longueurs de trace.

- Contrôle : Effectuez une simulation thermique préliminaire. Assurez-vous que les points chauds (hotspots) ne se chevauchent pas.

Analyse de l'intégrité de l'alimentation (PI)

- Action : Concevez le réseau de distribution électrique (PDN) pour gérer les courants transitoires élevés (di/dt) typiques des charges de travail de l'IA.

- Paramètre : Ciblez une impédance PDN inférieure à 10 mΩ jusqu'à 100 MHz.

- Contrôle : Vérifiez que la chute de tension continue (DC IR drop) est < 2 % sur tous les rails principaux.

Routage haute vitesse et définition du backdrill

- Action : Routez d'abord les voies PCIe Gen5/6 et DDR5. Attribuez des couches spécifiques pour minimiser les transitions de vias.

- Paramètre : Marquez tous les vias haute vitesse pour le backdrilling. Définissez clairement les couches "à ne pas couper" (must-not-cut) dans les fichiers de conception.

- Contrôle : Exécutez une simulation d'intégrité du signal (SI) (marge de fonctionnement du canal).

Revue DFM (Design for Manufacturing)

- Action : Soumettez les fichiers Gerber à APTPCB pour une vérification DFM complète avant la fabrication.

- Paramètre : Vérifiez les anneaux (annular rings) minimum, les rapports d'aspect et l'espacement (clearance) sur les plans d'alimentation internes.

- Contrôle : Confirmez que les tolérances de profondeur de backdrill sont réalisables (généralement ± 5 mils).

Fabrication : Lamination et perçage

- Action : Le fabricant effectue une lamination séquentielle (si HDI) ou une lamination standard.

- Paramètre : Contrôlez la température du cycle de pressage pour assurer le durcissement complet de la résine sans vides.

- Contrôle : Vérification par rayons X de l'alignement des couches (alignement perçage-cuivre).

Fabrication : Placage et finition de surface

- Action : Appliquez le placage de cuivre suivi de la finition de surface (ENIG, Immersion Silver ou ENEPIG).

- Paramètre : Assurez-vous que l'épaisseur de cuivre sur la paroi du trou répond à la classe 3 (> 25 µm).

- Contrôle : Analyse de section transversale d'un coupon de test pour vérifier l'intégrité du placage.

Tests électriques (BBT et TDR)

- Action : 100 % de tests de Netlist (sonde volante - Flying Probe ou lit de clous) et tests d'impédance.

- Paramètre : Les coupons TDR doivent passer à ± 5 % ou ± 10 % comme spécifié.

- Contrôle : Certificat de conformité (CoC) montrant les résultats de réussite du TDR.

Dépannage du PCB de serveur d'inférence (modes de défaillance et correctifs)

Lorsqu'un PCB de serveur d'inférence tombe en panne, cela est souvent dû à des problèmes subtils d'intégrité du signal ou à un stress thermique plutôt qu'à de simples circuits ouverts. Utilisez ce guide pour diagnostiquer les causes profondes.

Symptôme 1 : Taux d'erreur binaire (BER) élevé sur les liaisons PCIe

- Causes possibles :

- Profondeur de backdrilling incorrecte (stub laissé trop long).

- Effet de tissage de la fibre (fiber weave effect) (décalage entre les branches de la paire différentielle).

- Désadaptation d'impédance due à une surgravure (over-etching).

- Vérifications : Analyse TDR de la liaison défaillante ; Section transversale du stub de via ; Mesure VNA de la perte d'insertion.

- Correctif : Relance (Respin) avec une tolérance de backdrill plus stricte ou utilisation du routage "Zig-Zag" (angle de 10 degrés) pour atténuer l'effet de tissage de la fibre.

- Prévention : Spécifiez "Spread Glass" (verre étalé) ou tissu étalé mécaniquement dans les notes de matériaux.

Symptôme 2 : Plantages intermittents du système sous charge

- Causes possibles :

- Défaillance de l'intégrité de l'alimentation (chute de tension) provoquant une instabilité CPU/GPU.

- Arrêt thermique dû à un mauvais transfert de chaleur à travers le PCB.

- Vérifications : Mesurez l'ondulation de tension (voltage ripple) au niveau des condensateurs de charge avec un oscilloscope ; Vérifiez les images de la caméra thermique pour les points chauds.

- Correctif : Ajoutez des condensateurs de découplage ; Augmentez le poids du cuivre sur les plans d'alimentation ; Utilisez la technologie PCB en cuivre lourd.

- Prévention : Effectuez une simulation PI rigoureuse (Chute DC et Impédance AC) lors de la conception.

Symptôme 3 : Cratérisation des pastilles BGA (Pad Cratering) ou fracture du joint

- Causes possibles :

- Différence de CTE (Coefficient d'expansion thermique) entre le grand boîtier BGA et le matériau du PCB.

- Flexion excessive de la carte pendant l'assemblage ou l'installation.

- Vérifications : Test de ressuage et d'arrachement (dye-and-pry test) ; Microsection du joint fracturé.

- Correctif : Utilisez un matériau à Tg plus élevée avec un CTE sur l'axe Z plus faible ; Ajoutez de la colle de coin/sous-remplissage (underfill) aux BGA.

- Prévention : Assurez la symétrie de l'empilement (stackup) pour réduire le gauchissement ; Utilisez des vias remplis de résine (VIPPO) pour un meilleur support mécanique.

Symptôme 4 : Courts-circuits de filament anodique conducteur (CAF)

- Causes possibles :

- Pénétration d'humidité dans les faisceaux de verre combinée à une polarisation de tension élevée.

- Mauvaise qualité de perçage (micro-fissures dans la résine).

- Vérifications : Test de résistance d'isolement ; Microsection montrant la croissance du cuivre le long des fibres de verre.

- Correctif : Les cartes mises au rebut ne peuvent pas être réparées. La nouvelle production doit utiliser des matériaux anti-CAF.

- Prévention : Spécifiez un stratifié de qualité "Anti-CAF" ou "Résistant au CAF" (ex. série Isola 370HR ou Megtron).

Symptôme 5 : Délaminage après refusion (Reflow)

- Causes possibles :

- Humidité piégée dans le PCB (effet pop-corn).

- Systèmes de résine incompatibles dans les empilements hybrides.

- Vérifications : Inspection visuelle pour la formation de cloques ; Microscopie acoustique à balayage (SAM).

- Correctif : Cuisez les cartes avant l'assemblage (120 °C pendant 4 à 6 heures).

- Prévention : Stockez les PCB dans des sacs scellés sous vide avec des cartes indicatrices d'humidité ; Suivez les directives MSL.

Comment choisir un PCB de serveur d'inférence (décisions de conception et compromis)

Choisir la bonne spécification pour un PCB de serveur d'inférence implique de naviguer dans les compromis entre les performances, la capacité thermique et le coût.

1. Matériau : Perte moyenne vs. Très faible perte

- Perte moyenne (Mid-Loss) (ex. Isola 370HR) : Acceptable pour les traces courtes PCIe Gen3 ou Gen4. Moindre coût, plus facile à traiter.

- Très faible perte (Ultra-Low Loss) (ex. Megtron 7, Tachyon) : Obligatoire pour les PCIe Gen5/6 et les traces longues (> 10 pouces). Sensiblement plus cher et nécessite des paramètres de lamination spécialisés.

- Décision : Si votre serveur d'inférence utilise des accélérateurs Gen5, vous devez utiliser des matériaux à faible perte. Ne faites aucun compromis ici.

2. Facteur de forme : 1U vs. 2U/4U

- PCB de serveur 1U : Espace extrêmement contraint. Nécessite des emplacements mémoire horizontaux et des canaux de flux d'air optimisés. La gestion thermique repose fortement sur le fait que le PCB répartit la chaleur vers le châssis.

- PCB de serveur 2U/4U : Permet des cartes de montage (riser cards) verticales et des dissipateurs thermiques plus grands. La disposition du PCB peut être légèrement moins dense, mais la taille de la carte (souvent E-ATX ou personnalisée) introduit des défis de gauchissement.

- Décision : Les conceptions 1U nécessitent souvent l'HDI (High Density Interconnect) pour intégrer le routage, ce qui augmente le coût de la carte mais économise de l'espace dans le rack.

3. Traversant (Through-Hole) vs. HDI (High Density Interconnect)

- Traversant : Cartes multicouches standard. Moins cher, mais limite la densité de routage sous les grands BGA.

- HDI (Microvias) : Utilise des vias borgnes et enterrés percés au laser. Essentiel pour router des BGA au pas de 0,65 mm ou moins que l'on trouve dans les puces d'IA modernes.

- Décision : La plupart des conceptions de PCB de serveur IA haut de gamme nécessitent désormais au moins un HDI de type 3 (microvias empilés) pour sortir les signaux haute vitesse du processeur principal.

4. Finition de surface : ENIG vs. Immersion Silver vs. OSP

- ENIG : Excellente durée de conservation (shelf life) et surface plane. Bon pour la plupart des applications, mais peut souffrir du "Black Pad" s'il n'est pas contrôlé.

- Argent par immersion (Immersion Silver) : Préférable pour les signaux à très haute fréquence (pas d'effet de peau du nickel). Courant dans les cartes de supercalculateurs/serveurs.

- OSP : Le moins cher, mais durée de conservation la plus courte. Rarement utilisé pour les cartes de serveurs à haute fiabilité.

- Décision : Choisissez Immersion Silver pour une intégrité du signal de premier ordre ; choisissez ENIG pour la fiabilité générale et la durée de conservation.

FAQ sur les PCB de serveurs d'inférence (coût, délai de livraison, défauts courants, critères d'acceptation, fichiers DFM)

Q : Quel est le nombre typique de couches pour un PCB de serveur d'inférence IA ? R : La plupart des cartes de serveurs d'inférence se situent entre 12 et 24 couches.

- 12-16 couches : Courant pour les serveurs d'inférence edge à un seul socket.

- 18-24 couches : Requis pour les serveurs de centre de données à double socket avec plusieurs cartes accélératrices pour gérer la densité de routage et les plans d'alimentation.

Q : Comment le backdrilling affecte-t-il le coût du PCB ? R : Le backdrilling augmente le coût de 10 à 20 % selon le nombre de perçages.

- Il ajoute un processus de perçage CNC secondaire.

- Il nécessite une inspection spécialisée (rayons X) pour vérifier le contrôle de la profondeur.

- Cependant, c'est moins cher que d'ajouter plus de couches pour éviter les stubs.

Q : Puis-je utiliser du FR-4 pour un serveur d'inférence PCIe Gen5 ? R : En général, non. Le FR-4 standard a un facteur de dissipation (Df) trop élevé (~ 0,02), provoquant une perte de signal excessive à 16-32 GHz.

- Vous avez besoin de matériaux avec Df < 0,005 (ex. Megtron 6/7).

- L'utilisation de FR-4 entraînera probablement un canal qui échouera aux tests de conformité.

Q : Quels sont les critères d'acceptation pour les PCB de serveur de classe 3 ? R : L'IPC-6012 Classe 3 "Haute fiabilité" est la norme.

- Anneau (Annular Ring) : Aucune rupture (breakout) autorisée (la tangence n'est pas acceptable).

- Placage : Moyenne minimale de 25 µm dans les trous.

- Visuel : Pas de cuivre exposé, pas de cloques, alignement strict du masque de soudure.

- Fiabilité : Doit passer les tests de stress thermique sans délaminage.

Q : Quels fichiers dois-je envoyer pour une revue DFM ? R : Pour obtenir un devis précis et un DFM, envoyez :

- Fichiers Gerber (RS-274X) : Toutes les couches de cuivre, masque de soudure, sérigraphie, fichiers de perçage.

- Netlist IPC-356 : Critique pour vérifier la connectivité électrique par rapport aux graphiques.

- Plan de fabrication (Fab Drawing) : Spécifiant le matériau, l'empilement, les tables d'impédance et le tableau de perçage.

- Readme : Notant les exigences particulières telles que "Backdrill couches X à Y" ou "Trous pour connecteurs press-fit".

Q : Comment gérez-vous la gestion thermique pour les serveurs IA de 1000W+ ? R : Nous utilisons plusieurs techniques :

- Cuivre lourd (Heavy Copper) : Couches internes de 2 oz ou 3 oz pour la distribution de l'énergie.

- Vias thermiques : Tableaux denses de vias sous les composants chauds pour transférer la chaleur vers les plans internes.

- Pièces intégrées (Embedded Coins) : Insertion d'une pièce en cuivre massif directement dans le PCB sous le GPU/CPU (capacité avancée).

Q : Quel est le délai de fabrication des PCB de serveurs d'inférence ? R : Les délais de livraison sont plus longs que pour les cartes standards en raison de la disponibilité des matériaux et de la complexité.

- Standard : 15-20 jours ouvrables.

- Délai rapide (Quick Turn) : 8-12 jours ouvrables (si le matériel est en stock).

- Remarque : Les matériaux haute vitesse (Megtron, Tachyon) peuvent avoir leurs propres délais d'approvisionnement de 2 à 4 semaines s'ils ne sont pas en stock.

Q : Pourquoi le contrôle de l'impédance est-il si critique pour ces cartes ? R : Aux hautes vitesses, la trace du PCB agit comme une ligne de transmission.

- Si l'impédance change (ex. variation de la largeur de la trace), une partie du signal est réfléchie.

- Cette réflexion provoque du bruit (jitter) et ferme le "diagramme de l'œil" (eye diagram), rendant les 0 et les 1 indiscernables.

Q : Prenez-vous en charge les connecteurs press-fit pour les fonds de panier de serveurs ? R : Oui, les connecteurs press-fit sont standard pour les E/S des serveurs.

- La tolérance des trous est extrêmement serrée (ex. ± 0,05 mm).

- Nous contrôlons strictement la taille du trou fini (FHS) pour assurer une bonne rétention de la broche sans endommager le canon (barrel).

Q : Quelle est la différence entre la construction "Core" et "Foil" dans les empilements ? R : Cela affecte le coût et l'alignement.

- Construction Core (Noyau) : Utilise des noyaux stratifiés durcis. Meilleure stabilité dimensionnelle.

- Construction Foil (Feuille) : Utilise plus de préimprégné. Peut être moins cher mais peut bouger davantage lors de la lamination.

- Recommandation : Pour les cartes de serveurs à grand nombre de couches, nous recommandons des constructions de noyau spécifiques pour minimiser le gauchissement.

Ressources pour le PCB de serveur d'inférence (pages et outils connexes)

Pour vous aider davantage dans votre processus de conception et d'approvisionnement, APTPCB fournit des guides détaillés sur les technologies connexes :

- PCB de centre de données de serveur : Aperçu de nos capacités pour le marché plus large des centres de données.

- PCB haute vitesse : Plongée approfondie dans l'intégrité du signal, les matériaux et les règles de conception.

- PCB multicouche : Comprendre les empilements, la lamination et l'alignement pour un grand nombre de couches.

- PCB Megtron : Spécificités sur la famille de matériaux Panasonic essentielle pour les serveurs d'IA.

- PCB de fond de panier (Backplane) : Pour les conceptions impliquant de grandes cartes d'interconnexion passives.

- PCB HDI : Si votre serveur d'inférence nécessite des microvias pour un routage BGA dense.

Glossaire des PCB de serveurs d'inférence (termes clés)

| Terme | Définition | Contexte dans le PCB de serveur d'inférence |

|---|---|---|

| PCIe Gen5 | Peripheral Component Interconnect Express, Génération 5. | L'interface standard pour connecter des accélérateurs d'IA, fonctionnant à 32 GT/s. Nécessite un PCB à très faible perte. |

| Perte d'insertion (Insertion Loss) | La perte de puissance du signal lorsqu'il se déplace le long d'une trace. | Mesurée en dB/pouce. Doit être minimisée pour s'assurer que les signaux atteignent le récepteur intacts. |

| Backdrilling | Perçage à profondeur contrôlée pour retirer la portion inutilisée d'un trou traversant plaqué (stub). | Essentiel pour réduire la réflexion du signal dans les vias haute vitesse (> 10 Gbps). |

| Df (Facteur de dissipation) | Une mesure de la quantité d'énergie absorbée par le matériau isolant. | Plus il est bas, mieux c'est. Le FR4 standard est d'environ 0,02 ; la qualité serveur est < 0,005. |

| Dk (Constante diélectrique) | Une mesure de la capacité du matériau à stocker l'énergie électrique. | Affecte la vitesse de propagation du signal et l'impédance. Un Dk stable est crucial. |

| PAM4 | Modulation d'amplitude d'impulsion à 4 niveaux. | Un schéma de codage utilisé dans les liaisons haute vitesse (comme PCIe Gen6/Ethernet) très sensible au bruit. |

| CTE (Coefficient d'expansion thermique) | Dans quelle mesure le matériau se dilate lorsqu'il est chauffé. | Une inadéquation entre le PCB et les composants provoque des fissures dans les joints de soudure. |

| Tg (Température de transition vitreuse) | La température à laquelle la résine du PCB passe de dure à molle. | Les cartes de serveurs ont besoin d'une Tg élevée (> 170 °C) pour survivre à l'assemblage et à la chaleur. |

| VIPPO | Via-in-Pad Plated Over. | Une technologie où les vias sont placés dans des pastilles, remplis de résine et recouverts d'un placage. Utilisé pour les BGA denses. |

| Effet de tissage de la fibre (Fiber Weave Effect) | Décalage (skew) du signal causé par le motif de la fibre de verre dans le stratifié du PCB. | Peut causer des erreurs de synchronisation dans les paires différentielles. Atténué par le routage "Zig-Zag" ou le verre étalé (spread glass). |

| Contrôle d'impédance | Processus de fabrication pour s'assurer que la résistance de la trace correspond à la conception (ex. 85 Ω). | Critique pour prévenir la réflexion du signal. |

| Press-Fit | Une méthode de connexion sans soudure utilisant des broches conformes enfoncées dans les trous du PCB. | Standard pour les connecteurs de serveur (RJ45, cages) afin d'éviter le stress thermique de la soudure. |

Demander un devis pour un PCB de serveur d'inférence (Revue Design for Manufacturability (DFM) + prix)

Prêt à passer votre PCB de serveur d'inférence de la conception à la production ? APTPCB est spécialisé dans les cartes de serveurs haute vitesse à grand nombre de couches avec une stricte conformité à la classe 3.

Envoyez-nous vos données pour une vérification DFM complète :

- Fichiers Gerber : Ensemble complet comprenant les fichiers de perçage.

- Diagramme d'empilement (Stackup) : Spécifiant le type de matériau (ex. Megtron 7) et l'ordre des couches.

- Plan de perçage (Drill Drawing) : Marquant clairement les emplacements et les profondeurs de backdrill.

- Exigences d'impédance : Valeurs cibles et couches spécifiques.

- Volume et délai de livraison : Quantité de prototypes par rapport aux objectifs de production de masse.

Conclusion (prochaines étapes)

La fabrication réussie d'un PCB de serveur d'inférence est un exploit d'ingénierie de précision, nécessitant une synchronisation parfaite de matériaux à faible perte, un perçage à profondeur contrôlée et des tests d'impédance rigoureux. Que vous construisiez un PCB de serveur 1U compact pour l'analyse edge ou un PCB de serveur IA massif pour le centre de données, la différence entre le succès et l'échec réside souvent dans les détails de fabrication. En adhérant à des règles de conception strictes et en vous associant à un fabricant compétent, vous vous assurez que votre matériel offre la faible latence et le débit élevé requis pour les charges de travail d'IA modernes.