L'obtention d'une intégrité de signal (SI) fiable à 64 GT/s en utilisant la modulation PAM4 nécessite une adhésion stricte à une stratégie de liste de contrôle SI PCIe Gen6 pour la production de masse. Contrairement aux générations précédentes, la Gen6 ne laisse presque aucune marge pour les variations de fabrication. Un écart mineur dans la rugosité du cuivre, l'épaisseur du diélectrique ou la longueur du stub de via peut provoquer l'effondrement du diagramme de l'œil et entraîner des défaillances de taux d'erreur binaire (BER).

APTPCB (Usine de PCB APTPCB) est spécialisée dans le contrôle de ces variables pour les conceptions numériques à haute vitesse. Ce guide fournit les paramètres spécifiques, les points d'inspection et les étapes de dépannage nécessaires pour faire passer une conception PCIe Gen6 du prototype à la fabrication en grand volume sans perte de rendement.

Checklist SI PCIe Gen6 pour la production de masse : réponse rapide (30 secondes)

Pour les ingénieurs ayant besoin de critères de validation immédiats, voici les exigences non négociables pour la production en volume Gen6.

- Sélection des matériaux : Doit utiliser des stratifiés à très faible perte (Df < 0,002 à 32 GHz) tels que Panasonic Megtron 7/8 ou Isola Tachyon 100G. Le FR4 standard n'est pas viable.

- Rugosité du cuivre : Spécifier une feuille de cuivre HVLP (Hyper Very Low Profile) ou VLP2 pour minimiser la perte du conducteur due à l'effet de peau à 32 GHz (Nyquist).

- Contrôle de l'impédance : Resserrer la tolérance à ±5% ou ±7% pour les paires différentielles de 85Ω ou 100Ω ; la tolérance standard de ±10% est souvent insuffisante pour les marges de signalisation PAM4.

- Gestion des Vias : Le rétro-perçage est obligatoire pour tous les vias de signal traversants afin de réduire la longueur de stub en dessous de 6-8 mils (0,15 mm-0,20 mm).

- Effet de tissage de fibres : Faites pivoter la conception de 10-15 degrés ou utilisez du verre étalé (par exemple, 1067, 1078) pour éviter le biais causé par l'alignement du tissage de fibres.

- Finition de surface : Utilisez l'Argent d'immersion ou l'ENEPIG ; évitez le HASL en raison de sa planéité inégale et de ses caractéristiques de perte plus élevées.

Quand la checklist SI PCIe Gen6 pour la production de masse s'applique (et quand elle ne s'applique pas)

Comprendre quand appliquer ces contrôles rigoureux permet d'éviter des dépassements de coûts inutiles.

S'applique à :

- Accélérateurs d'IA et de centres de données : Cartes mères de serveur et modules OAM nécessitant un débit de 64 GT/s.

- Cartes d'interface réseau (NIC) haut de gamme : Adaptateurs Ethernet 400G/800G utilisant des interfaces PCIe Gen6.

- Baies de stockage NVMe : Contrôleurs SSD de classe entreprise poussant la bande passante maximale.

- Équipements de test et de mesure : Oscilloscopes BERT et analyseurs de protocole validant la conformité Gen6.

Ne s'applique pas à :

- Appareils hérités PCIe Gen3/Gen4 : Le FR4 standard et les vias standard sont suffisants ; les contrôles Gen6 sont excessifs.

- Périphériques à faible vitesse : Les contrôleurs USB ou les interfaces de gestion (I2C/SPI) sur la même carte n'ont pas besoin de ces règles SI spécifiques.

- Électronique grand public à courte portée : Les appareils où les longueurs de trace sont < 2 pouces pourraient survivre avec des matériaux de qualité inférieure, bien qu'un risque demeure.

- Exécutions de prototypes uniquement : Bien que l'intégrité du signal (SI) soit importante, le contrôle statistique des processus (SPC) de production de masse n'est pas encore pertinent.

Checklist SI PCIe Gen6 pour la production de masse : règles et spécifications (paramètres clés et limites)

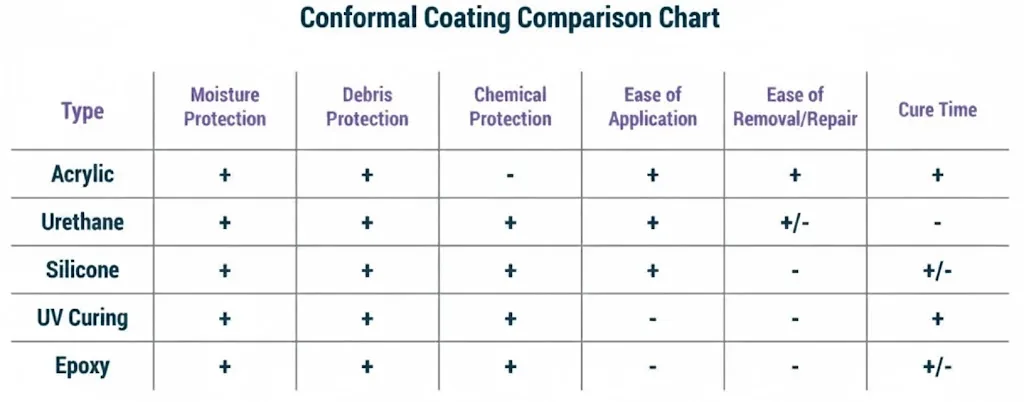

Le tableau suivant présente les règles de fabrication critiques. Ces valeurs doivent être explicitement indiquées dans les notes de fabrication pour garantir le respect de la norme de la liste de contrôle SI PCIe Gen6 pour la production de masse.

| Règle | Valeur/Plage recommandée | Pourquoi c'est important | Comment vérifier | Si ignoré |

|---|---|---|---|---|

| Impédance différentielle | 85Ω ou 100Ω ±5% | La signalisation PAM4 a des marges de bruit (SNR) réduites ; les réflexions doivent être minimisées. | Coupons TDR sur chaque panneau. | BER élevé, échec de l'apprentissage de liaison. |

| Perte diélectrique (Df) | < 0.002 @ 32 GHz | L'atténuation haute fréquence limite la portée du canal. | Méthode de test IPC-TM-650. | L'amplitude du signal tombe en dessous de la sensibilité du récepteur. |

| Rugosité du cuivre | Rz < 2.0 µm (HVLP) | La résistance due à l'effet de peau augmente considérablement à 32 GHz. | Analyse de section transversale (SEM). | Perte d'insertion excessive. |

| Longueur de stub de via | < 8 mils (0.2mm) | Les stubs agissent comme des filtres coupe-bande, résonnant près de la fréquence de Nyquist. | Inspection aux rayons X ou microsection. | Chutes résonantes dans la perte d'insertion (S21). |

| Largeur/Espacement des pistes | Adhérence stricte au solveur de champ | Maintient le couplage et l'impédance ; la compensation de gravure de fabrication est critique. | AOI (Inspection Optique Automatisée). | Discontinuité d'impédance. |

| Enregistrement des couches | ± 3 mils | Le désalignement affecte le couplage aux plans de référence et aux transitions de via. | Vérification du perçage par rayons X. | Décalages d'impédance, courts-circuits potentiels. |

| Dk du masque de soudure | Faible Dk / Faible perte | Le masque de soudure sur les pistes ajoute de la capacitance et des pertes. | Certification de la fiche technique du matériau. | Chute d'impédance inattendue sur les couches externes. |

| Style de tissage de verre | Verre étalé (1067/1078) | Prévient la charge périodique et le biais du tissage de fibres. | Certification du matériau / Visuel. | Déséquilibre intra-paire, conversion de mode. |

| Épaisseur de placage | IPC Classe 3 (min 25µm) | Assure la fiabilité des vias sous contrainte thermique. | Coupe transversale. | Vias ouverts pendant le refusion ou le fonctionnement. |

| Facteur de gravure | ≥ 0,8 | Les pistes trapézoïdales affectent les calculs d'impédance. | Coupe transversale. | L'impédance calculée ne correspond pas à l'impédance mesurée. |

Checklist SI PCIe Gen6 pour la production de masse : points de contrôle du processus

Pour exécuter avec succès une production de masse de la liste de contrôle SI PCIe Gen6, le processus de fabrication doit suivre ces étapes de validation séquentielles.

Vérification de l'empilement et des matériaux

- Action : Confirmer la disponibilité du stratifié et les valeurs Dk/Df à 32 GHz avec le fournisseur.

- Paramètre : Df < 0,002.

- Vérification : Le certificat de conformité (CoC) du fournisseur correspond aux matériaux de PCB haute vitesse spécifiés.

Imagerie et gravure des couches internes

- Action : Appliquer des facteurs de compensation de gravure basés sur le poids du cuivre pour atteindre la largeur de trace cible.

- Paramètre : Tolérance de largeur de trace ±0,5 mil.

- Vérification : Inspection AOI des paires de signaux de couche interne pour détecter les rétrécissements ou les violations d'espacement.

Stratification & Enregistrement

- Action : Utiliser des systèmes d'alignement optique pour lier les couches.

- Paramètre : Enregistrement couche à couche < 3 mils.

- Vérification : Vérification des cibles de perçage par rayons X après stratification.

Perçage & Déperçage

- Action : Percer des trous traversants suivi d'un déperçage contrôlé en profondeur pour retirer les stubs.

- Paramètre : Stub résiduel max 8 mils.

- Vérification : Analyse de microsection sur des coupons de test pour vérifier la longueur des stubs.

Placage & Finition de Surface

- Action : Appliquer un placage de cuivre suivi d'une finition de surface plane (Argent d'immersion/ENEPIG).

- Paramètre : Variation de la planéité de surface < 2 µm.

- Vérification : Inspection visuelle et test au ruban adhésif pour l'adhérence.

Test d'Impédance (TDR)

- Action : Tester les coupons d'impédance aux deux extrémités du panneau.

- Paramètre : 85Ω ±5%.

- Vérification : Les journaux TDR doivent indiquer le statut de réussite pour toutes les paires différentielles.

Test de Perte d'Insertion (Optionnel/Échantillon)

- Action : Utiliser un VNA pour mesurer S21 sur des structures de test spécifiques si nécessaire.

- Paramètre : Perte < -0,8 dB/pouce @ 32 GHz (cible exemple).

- Vérification : Comparer les paramètres S aux modèles de simulation.

Checklist SI PCIe Gen6 pour la production de masse : dépannage (modes de défaillance et correctifs)

Même avec une liste de contrôle SI PCIe Gen6 robuste, des défauts peuvent survenir. Utilisez ce guide pour diagnostiquer les défaillances courantes en production de masse.

Symptôme: Taux d'erreur binaire (BER) élevé pendant l'entraînement de liaison

- Cause: Désadaptation d'impédance ou gigue excessive.

- Vérification: Examinez les données TDR pour les discontinuités d'impédance > 5Ω. Vérifiez l'inclinaison du tissage de la fibre (fiber weave skew).

- Correction: Ajustez la largeur de la trace dans le CAM pour la prochaine exécution; passez au verre étalé (spread glass).

Symptôme: "Chute" de la perte d'insertion (S21) autour de 16-20 GHz

- Cause: Résonance du stub de via.

- Vérification: Vérifiez la profondeur du contre-perçage (backdrill). Un stub plus long que 10 mils peut provoquer une résonance dans la bande de fréquence Gen6.

- Correction: Augmentez le réglage de la profondeur du contre-perçage; assurez-vous que le foret ne dévie pas.

Symptôme: Perte d'insertion excessive (Signal trop faible)

- Cause: Profil de cuivre rugueux ou matériau diélectrique incorrect.

- Vérification: Effectuez une microsection pour vérifier la rugosité du cuivre (Rz). Confirmez que le bon stratifié a été utilisé.

- Correction: Imposer l'utilisation de cuivre HVLP; vérifiez que le processus de traitement d'oxyde ne rend pas le cuivre excessivement rugueux.

Symptôme: Décalage (Skew) entre les voies P et N

- Cause: Effet de tissage de la fibre ou longueurs de trace inégales.

- Vérification: Inspectez le style de verre (1080 vs 1067). Vérifiez la correspondance des longueurs dans la disposition.

- Correction: Faites pivoter la conception sur le panneau ou spécifiez des stratifiés en verre étalé.

Symptôme: Perte de liaison intermittente

- Cause: Fiabilité des micro-vias ou CAF (Conductive Anodic Filament).

- Vérification : Test de stress thermique (IST). Vérifier la croissance de CAF entre les vias à pas serré.

- Correction : Augmenter l'espacement via-à-via ; améliorer la teneur en résine du préimprégné.

Symptôme : Chute d'impédance de l'empreinte du connecteur

- Cause : Capacitance excessive au niveau des pastilles.

- Vérification : TDR spécifiquement au niveau de la zone de lancement du connecteur.

- Correction : Découper les plans de référence sous les pastilles du connecteur (anti-pads) pour augmenter le pic inductif.

Checklist SI PCIe Gen6 pour la production de masse : décisions de conception et compromis

La mise en œuvre d'un plan de production de masse avec la liste de contrôle SI PCIe Gen6 implique d'équilibrer les performances par rapport aux coûts et à la fabricabilité.

Matériau vs. Coût Pour la Gen6, le FR4 standard est obsolète. Le choix se fait entre "Faible perte" (par exemple, Megtron 6) et "Ultra-faible perte" (par exemple, Megtron 7/8).

- Décision : Si la longueur de la trace est courte (< 4 pouces), le Megtron 6 pourrait suffire. Pour les canaux plus longs (> 10 pouces), vous devez utiliser du Megtron 7 ou équivalent pour respecter le budget de perte.

Nombre de couches vs. Diaphonie Un nombre de couches plus élevé permet une meilleure isolation (Masse-Signal-Masse) mais augmente les coûts et les cycles de lamination.

- Décision : Pour la Gen6, privilégiez le routage en stripline (couches internes) pour contenir les champs électromagnétiques. Évitez les microstrips (couches externes) pour les longues distances en raison du rayonnement et du FEXT (Far-End Crosstalk).

Défonçage (Backdrilling) vs. Vias aveugles/enterrés Le défonçage est moins cher que la lamination séquentielle (HDI) mais laisse un petit moignon.

- Décision : Utiliser le défonçage pour les connecteurs standard. N'utiliser le HDI (vias aveugles/enterrés) que si la densité BGA l'exige, car cela augmente considérablement les coûts de fabrication de PCB en série.

Checklist SI PCIe Gen6 pour la production de masse – FAQ (coût, délai, défauts courants, critères d'acceptation, fichiers DFM)

1. Dans quelle mesure la production de masse conforme à la liste de contrôle SI PCIe Gen6 augmente-t-elle le coût des PCB ? Le passage de Gen4 (type FR4) à Gen6 (Megtron 7/8) augmente généralement le coût de la carte nue de 2,5 à 4 fois en raison des matières premières coûteuses et des étapes de processus supplémentaires comme le défonçage.

2. Quel est le délai de livraison pour les stratifiés compatibles Gen6 ? Les matériaux à très faible perte ont souvent des délais de livraison de 4 à 8 semaines. APTPCB recommande des accords de stockage pour la production de masse récurrente afin d'atténuer les retards.

3. Quels sont les critères d'acceptation pour l'impédance Gen6 ? L'acceptation standard est de ±10 %, mais Gen6 exige souvent ±5 % ou ±7 %. Les coupons TDR doivent respecter cette limite plus stricte.

4. Ai-je besoin d'un test TDR à 100 % pour la production de masse ? Oui. Pour Gen6, l'échantillonnage statistique est risqué. Nous recommandons un test TDR à 100 % sur toutes les paires différentielles haute vitesse.

5. Quels fichiers DFM sont requis pour un devis Gen6 ? Envoyez les fichiers Gerber X2 ou ODB++, un dessin détaillé de la superposition de PCB spécifiant les types de matériaux (par exemple, "Megtron 7"), et une netlist IPC pour la comparaison des tests électriques.

6. Puis-je utiliser la finition HASL pour PCIe Gen6 ? Non. Le HASL est trop irrégulier pour les composants à pas fin et ajoute des pertes. Utilisez ENIG, ENEPIG ou l'argent d'immersion.

7. Comment la rugosité du cuivre affecte-t-elle l'intégrité du signal (SI) Gen6 ? À 32 GHz, le courant circule dans la peau externe du cuivre. Le cuivre rugueux augmente la longueur du chemin, augmentant considérablement la perte résistive. Le cuivre HVLP est obligatoire.

8. Quelle est la longueur maximale autorisée pour un stub de via ? Idéalement zéro, mais pratiquement < 10 mils (0,25 mm). Les stubs > 15 mils peuvent provoquer des creux de résonance fatals dans la bande de fréquences Gen6.

9. Le « verre étalé » est-il obligatoire ? Il est fortement recommandé d'éviter le biais de tissage de fibres. Si le verre étalé n'est pas disponible, l'illustration doit être tournée sur le panneau, ce qui gaspille du matériau.

10. Comment valider les capacités du fabricant ? Demandez un « Rapport d'intégrité du signal » des fabrications précédentes ou demandez des données de corrélation TDR. Vérifiez s'ils disposent de capacités de test VNA en interne.

11. Quelle est la différence entre l'assemblage et la fabrication de la liste de contrôle SI PCIe Gen6 ? La fabrication se concentre sur la carte nue (impédance, matériaux). L'assemblage se concentre sur la qualité des joints de soudure, l'insertion des connecteurs et la garantie que les résidus de flux n'affectent pas l'impédance de surface.

12. Pourquoi le « facteur de gravure » est-il critique dans la liste de contrôle ? Les pistes sont trapézoïdales, pas rectangulaires. Si le fabricant suppose un rectangle pour le calcul de l'impédance mais grave un trapèze, l'impédance réelle sera supérieure à celle calculée.

13. La couleur du masque de soudure affecte-t-elle l'intégrité du signal (SI) ? Oui. Certains pigments (comme le noir) peuvent être plus dissipatifs ou conducteurs. Le vert ou le bleu sont standard ; vérifiez le Dk/Df de l'encre de masque de soudure spécifique utilisée.

14. Quels sont les défauts courants dans la conception de la liste de contrôle SI PCIe Gen6 ? Les plus courants sont : ignorer les stubs de via, utiliser une feuille de cuivre standard et ne pas tenir compte du changement de Dk des zones riches en résine entre les paires différentielles.

Ressources de la checklist SI PCIe Gen6 (pages et outils connexes)

- Données Matériaux : Matériaux PCB Megtron

- Processus de Fabrication : Capacités de PCB Haute Vitesse

- Directives de Conception : Directives DFM

Glossaire de la checklist SI PCIe Gen6 (termes clés)

| Terme | Définition | Pertinence pour Gen6 |

|---|---|---|

| PAM4 | Modulation d'amplitude d'impulsion à 4 niveaux. | Encode 2 bits par symbole ; nécessite un SNR plus élevé que le NRZ. |

| Fréquence de Nyquist | La moitié du débit de données (32 GHz pour Gen6). | La fréquence à laquelle la perte de signal fondamentale est mesurée. |

| Effet de peau | Tendance du courant alternatif à circuler près de la surface. | Fait de la rugosité du cuivre un facteur de perte critique. |

| HVLP | Cuivre à profil hyper très bas. | Feuille de cuivre lisse utilisée pour minimiser la perte par effet de peau. |

| Backdrilling | Perçage de la partie inutilisée d'un via plaqué. | Élimine les stubs pour éviter la réflexion/résonance du signal. |

| TDR | Réflectométrie dans le domaine temporel (Time Domain Reflectometry). | Méthode pour mesurer les profils d'impédance le long d'une trace. |

| VNA | Analyseur de réseau vectoriel (Vector Network Analyzer). | Instrument pour mesurer les paramètres S (perte d'insertion/perte de retour). |

| Perte d'insertion (S21) | Puissance du signal perdue lors de son déplacement le long de la ligne. | La principale contrainte budgétaire pour les canaux Gen6. |

| Perte de retour (S11) | Puissance du signal réfléchie vers la source. | Indique la qualité du désadaptation d'impédance. |

| Skew | Différence de délai temporel entre les signaux P et N. | Détruit l'ouverture de l'œil du signal différentiel. |

| Dk (Constante diélectrique) | Mesure de la capacité d'un matériau à stocker de l'énergie. | Détermine la vitesse de propagation et l'impédance. |

| Df (Facteur de dissipation) | Mesure de l'énergie perdue sous forme de chaleur dans le matériau. | Détermine l'atténuation du signal (perte). |

Demander un devis pour la checklist SI PCIe Gen6 (revue DFM + prix)

APTPCB fournit une analyse DFM détaillée pour garantir que votre empilement et votre géométrie haute vitesse répondent aux rendements de production en série.

Pour obtenir un devis précis et une revue SI, veuillez fournir :

- Fichiers Gerber X2 ou ODB++.

- Plan de fabrication : Doit spécifier le matériau (par exemple, "Megtron 7 ou équivalent"), le tableau d'impédance et les couches de backdrill.

- Diagramme d'empilement : Nombre de couches, poids du cuivre et épaisseur diélectrique.

- Volume : Quantité de prototype par rapport à l'utilisation annuelle estimée (EAU).

Conclusion (prochaines étapes)

Pour réussir la mise à l'échelle vers la production de masse selon la liste de contrôle PCIe Gen6 SI, il est nécessaire de passer de la fabrication de PCB standard à une fabrication à contrôle de précision. En imposant des contrôles stricts sur les matériaux, la rugosité du cuivre et la géométrie des vias, vous pouvez garantir la fiabilité des performances de 64 GT/s. APTPCB est prêt à soutenir votre transition grâce à des capacités d'ingénierie avancées et des contrôles qualité rigoureux.