La conception numérique à haute vitesse n'est plus une niche ; c'est la norme pour l'électronique moderne. À mesure que les débits de données atteignent la plage multi-gigabit, la marge d'erreur disparaît, rendant une liste de contrôle de validation SI rigoureuse essentielle pour les équipes d'ingénierie. Sans un processus de vérification structuré, les conceptions risquent une dégradation du signal, une corruption des données et des reprises de cartes coûteuses.

Ce guide constitue une ressource complète pour les ingénieurs et les chefs de projet. Nous passerons en revue les définitions critiques, les métriques qui définissent le succès et les points de contrôle spécifiques nécessaires pour faire passer une conception du concept à la production de masse avec APTPCB (APTPCB PCB Factory).

Points clés à retenir

- Définition : Une validation SI (Signal Integrity) n'est pas seulement une simulation ; c'est une vérification complète que la conception répond aux exigences de synchronisation, de bruit et électromagnétiques avant la fabrication.

- Métriques critiques : Le succès est mesuré par la continuité de l'impédance, la perte d'insertion, la perte de retour et l'ouverture du diagramme de l'œil.

- Le facteur "caché" : Les tolérances de fabrication (gravure, pression de laminage) affectent l'intégrité du signal autant que la disposition elle-même.

- Co-conception : Une validation efficace nécessite une

stackup and si co designdès le début du projet, et non seulement à la fin. - Validation : La simulation doit être corrélée avec les données de mesure (TDR/VNA) pour valider le

si channel budget. - Conscience de la puissance : Le signoff moderne doit inclure une

analyse SI consciente de la puissance, car le bruit de commutation simultanée (SSN) peut provoquer l'effondrement des diagrammes en œil. - Objectif : L'objectif ultime est une carte "First Pass Success" qui fonctionne de manière fiable dans son environnement prévu.

# intégrité du signal (SI) (portée et limites)

Avant de nous plonger dans des métriques spécifiques, nous devons établir qu'un processus de signoff robuste s'étend bien au-delà de l'exécution d'un outil de simulation logicielle.

Une véritable liste de contrôle de signoff SI est une porte d'assurance qualité qui comble le fossé entre la conception théorique et la réalité physique. Elle définit la portée de la vérification requise pour garantir que les signaux électriques voyagent de l'émetteur au récepteur sans distorsion inacceptable. Ce processus implique trois limites distinctes : le niveau de la puce (modèles IBIS/AMI), le niveau du boîtier (package) et le niveau de la carte (traces et vias PCB).

De nombreux ingénieurs croient à tort que le signoff est terminé une fois que l'autorouteur a fini ou qu'un DRC (Design Rule Check) de base est passé. Cependant, des phénomènes physiques tels que l'effet de peau, la perte diélectrique et l'effet de tissage des fibres n'apparaissent pas dans les DRC standard. La portée du signoff doit inclure :

- Analyse pré-layout : Définition des contraintes et des empilements (stackups).

- Vérification en cours de layout : Vérification en temps réel du couplage et de l'adaptation de longueur.

- Simulation post-layout : Extraction 3D pleine onde des nets critiques.

- Conformité de Fabrication : S'assurer que le fabricant peut construire les structures à impédance contrôlée dans les tolérances.

Cette approche holistique garantit que l'équipe aptpcb si support reçoit une conception qui est non seulement théoriquement solide mais aussi fabricable.

Métriques importantes (comment évaluer la qualité)

Une fois le périmètre défini, nous avons besoin de données quantitatives spécifiques pour mesurer le succès de la stratégie d'intégrité du signal.

Les métriques suivantes sont les indicateurs de performance non négociables pour les conceptions à haute vitesse. Une liste de contrôle de validation SI réussie exige que ces valeurs se situent dans les marges spécifiques définies par la norme d'interface (par exemple, PCIe, DDR, USB).

| Métrique | Pourquoi c'est important | Plage typique ou facteurs influençants | Comment mesurer |

|---|---|---|---|

| Impédance Caractéristique ($Z_0$) | Les désadaptations provoquent des réflexions, réduisant la puissance du signal et augmentant le bruit. | $50\Omega$ (Simple), $85\Omega$ ou $100\Omega$ (Différentiel). Tolérance $\pm 10%$ ou $\pm 5%$. | Simulation TDR (Time Domain Reflectometry) ou test physique sur coupon. |

| Perte d'Insertion (IL) | Détermine la quantité d'énergie du signal perdue lorsqu'il se propage le long de la trace. | Mesurée en dB/pouce. Dépend de la fréquence, du matériau diélectrique (Df) et de la rugosité du cuivre. | Paramètres S ($S_{21}$) via VNA ou simulation. |

| Perte de retour (RL) | Indique la quantité de signal réfléchie vers la source. | Devrait être $<-10\text{dB}$ (ou moins) pour la fréquence d'intérêt. | Paramètres S ($S_{11}$). |

| Diaphonie (NEXT/FEXT) | Le couplage indésirable entre les traces adjacentes perturbe la synchronisation du signal et les niveaux logiques. | $<-40\text{dB}$ est une cible courante. Influencé par l'espacement (règle $3W$) et les plans de référence. | Simulation par solveur de champ 3D. |

| Hauteur/Largeur du diagramme de l'œil | Visualise la qualité du signal et la marge de bruit au niveau du récepteur. | Défini par le protocole spécifique (par exemple, PCIe Gen5 nécessite des masques d'œil spécifiques). | Simulation transitoire (analyse du taux d'erreur binaire). |

| Gigue (Gigue totale) | Déviations de synchronisation pouvant entraîner des erreurs de verrouillage des données. | Mesuré en picosecondes (ps) ou en intervalles unitaires (UI). Inclut la gigue aléatoire et déterministe. | Analyse du diagramme de l'œil. |

| Impédance PDN | Une impédance élevée dans le réseau de distribution d'énergie (PDN) provoque des ondulations de tension (SSN). | L'impédance cible est généralement de l'ordre du milliohm ($m\Omega$) jusqu'à la fréquence de coupure. | Balayage de fréquence AC du plan d'alimentation. |

Guide de sélection par scénario (compromis)

Comprendre ces métriques permet aux ingénieurs de prioriser des paramètres spécifiques en fonction de l'environnement unique et des contraintes opérationnelles de la conception.

Différents protocoles haute vitesse sollicitent différentes parties de la liste de contrôle de validation SI. Il n'est pas possible d'optimiser tout simultanément ; des compromis sont inévitables concernant le coût, la densité et les performances.

1. Interfaces mémoire DDR (DDR4/DDR5)

- Objectif principal : Décalage temporel (Timing Skew) et temps de Setup/Hold.

- Compromis : Vous devez privilégier l'adaptation de longueur (réglage du délai) par rapport à la perte absolue.

- Conseil : Utilisez les topologies fly-by avec prudence. La validation doit vérifier que le bus d'adresses/commandes arrive à chaque puce au bon moment par rapport à l'horloge. L'

analyse SI sensible à la puissanceest critique ici car les bus mémoire commutent simultanément, créant des courants transitoires massifs.

2. Liaisons SerDes (PCIe, Ethernet, USB)

- Objectif principal : Perte d'insertion et perte de retour.

- Compromis : L'adaptation de longueur est moins critique que la minimisation des stubs de vias et des discontinuités d'impédance.

- Conseil : Concentrez-vous sur le

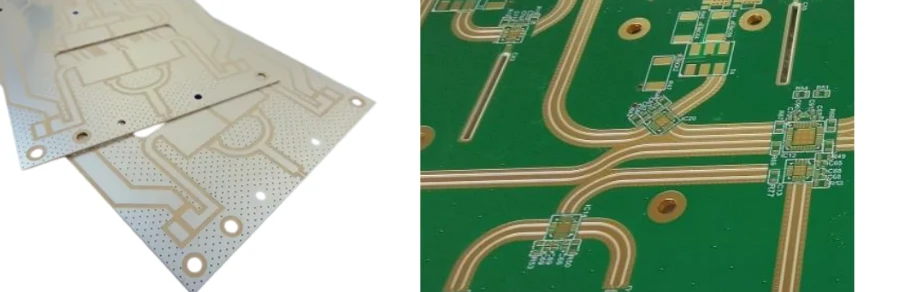

budget du canal SI. Chaque pouce de trace et chaque via consomme une partie de la perte admissible. Vous devrez peut-être sélectionner des matériaux de PCB à faible perte comme le Megtron 6 ou le Rogers, plutôt que le FR-4 standard, pour réussir la vérification.

3. Interconnexion haute densité (HDI)

- Objectif principal : Diaphonie et intégrité de l'alimentation.

- Compromis : Un routage plus serré augmente le risque de diaphonie.

- Conseil : Lors de l'utilisation de la technologie PCB HDI, les microvias sont excellentes pour l'intégrité du signal (SI) car elles ont des stubs minimaux. Cependant, les diélectriques minces augmentent la capacitance. La validation doit garantir que les chemins de retour ne sont pas interrompus par les champs de vias denses.

4. Signal mixte analogique / RF

- Objectif principal : Isolation et plancher de bruit.

- Compromis : La pureté du signal prime sur la densité.

- Conseil : La liste de contrôle doit vérifier la séparation physique. Des pistes de garde et des via stitching sont requis. La simulation doit se concentrer sur le couplage entre les sections numériques bruyantes et les entrées analogiques sensibles.

5. Conceptions Flex et Rigid-Flex

- Objectif principal : Cohérence de l'impédance pendant la flexion.

- Compromis : Flexibilité mécanique vs. stabilité électrique.

- Conseil : Les plans de masse hachurés sont souvent utilisés pour la flexibilité mais modifient la référence d'impédance. La validation doit tenir compte de la géométrie spécifique du maillage utilisée dans l'empilement du PCB Rigid-Flex.

6. Systèmes multi-cartes

- Objectif principal : Discontinuités des connecteurs et modèles de câbles.

- Compromis : Conception modulaire vs. continuité du signal.

- Conseil : La

corrélation SI multi-cartesest vitale. Le signal ne s'arrête pas au bord du PCB. Le jeu de simulation doit inclure des modèles de paramètres S pour les connecteurs et la carte d'accouplement afin de garantir le bon fonctionnement de l'ensemble du canal.

Du design à la fabrication (points de contrôle de l'implémentation)

Une fois la stratégie sélectionnée, nous passons à l'exécution tactique de la liste de contrôle de validation SI à travers des phases de conception spécifiques.

Cette section décrit les points de contrôle étape par étape. Chaque élément comprend une recommandation, le risque associé et la méthode d'acceptation.

Phase 1 : Pré-routage et empilement

- Vérification de l'empilement

- Recommandation : Définir tôt le nombre de couches, les épaisseurs de cuivre et les matériaux diélectriques. Utiliser un Calculateur d'Impédance pour estimer les largeurs de pistes.

- Risque : Si l'empilement change tardivement dans la conception, toutes les pistes d'impédance seront incorrectes.

- Acceptation : Approbation de

Stackup and si co designpar le fabricant (APTPCB).

Sélection des Matériaux

- Recommandation : Choisir les matériaux en fonction des exigences de tangente de perte (Df). Pour >10 Gbps, le FR-4 standard est probablement insuffisant.

- Risque : Atténuation excessive du signal entraînant une défaillance de la liaison.

- Acceptation : Examen de la fiche technique du matériau par rapport au budget de perte.

Configuration de la Gestion des Contraintes

- Recommandation : Saisir toutes les règles électriques (skew, topologie, espacement) dans l'outil CAO avant le routage.

- Risque : Erreurs de routage manuel difficiles à détecter visuellement.

- Acceptation : Vérification du système de contraintes CAO (aucune erreur).

Phase 2 : Implémentation du Layout

Continuité du Plan de Référence

- Recommandation : S'assurer que chaque piste haute vitesse passe au-dessus d'un plan de masse solide. Éviter de traverser des divisions.

- Risque : La discontinuité du chemin de retour crée une grande inductance de boucle, des EMI et une réflexion du signal.

- Acceptation : Inspection visuelle des couches de plan par rapport aux couches de signal.

Optimisation des Vias et Backdrilling

- Recommandation: Minimiser l'utilisation des vias. Pour les cartes épaisses, spécifier le défonçage pour retirer les stubs de via inutilisés.

- Risque: Les stubs de via agissent comme des antennes, provoquant des résonances et de graves creux de signal.

- Acceptation: Simulation 3D des vias montrant une fréquence de résonance acceptable.

Atténuation de la diaphonie

- Recommandation: Maintenir un espacement de $3W$ (la distance centre-à-centre est 3 fois la largeur de la trace) pour les réseaux critiques.

- Risque: Corruption des données due au couplage du bruit.

- Acceptation: Simulation de couplage montrant NEXT/FEXT dans les limites.

Placement du condensateur de découplage

- Recommandation: Placer les condensateurs aussi près que possible des broches d'alimentation de l'IC pour minimiser l'inductance de boucle.

- Risque: Chute de tension provoquant des réinitialisations de l'IC ou des erreurs logiques.

- Acceptation: Simulation d'analyse PDN.

Phase 3 : Post-Layout et Validation

Extraction Full-Wave

- Recommandation: Extraire les paramètres S pour les réseaux les plus critiques (par exemple, les voies PCIe, les groupes de données DDR).

- Risque: Les approximations 2D manquent les effets 3D comme le couplage via.

- Acceptation: Comparaison des paramètres S par rapport au masque de spécification de l'interface.

Simulation IBIS-AMI

- Recommandation: Exécuter des simulations de canal en utilisant les modèles IBIS-AMI fournis par le fournisseur pour Tx et Rx.

- Risque: Les paramètres S passifs semblent bons, mais le silicium actif ne peut pas piloter le canal.

- Acceptation : L'ouverture du diagramme de l'œil répond aux exigences de hauteur/largeur à un BER spécifique (par exemple, $10^{-12}$).

- Analyse des Tolérances de Fabrication

- Recommandation : Simuler les cas extrêmes (par exemple, impédance +10 %, épaisseur diélectrique -10 %).

- Risque : La conception fonctionne en simulation nominale mais échoue en production de masse.

- Acceptation : Analyse Monte Carlo ou réussite des cas extrêmes.

Erreurs courantes (et l'approche correcte)

Même avec une liste de contrôle robuste, des erreurs subtiles peuvent se glisser si l'équipe d'ingénierie néglige les réalités de fabrication.

Ignorer le chemin de retour :

- Erreur : Acheminer une trace haute vitesse sur une division dans le plan de masse ou changer de couches de référence sans via de raccordement.

- Correction : Toujours visualiser la boucle de courant. Le courant de retour suit le chemin de moindre inductance (directement sous le signal). Si vous changez de couches, placez un via de masse à côté du via de signal.

Faire trop confiance aux fiches techniques :

- Erreur : Utiliser les valeurs Dk/Df "marketing" d'une fiche technique de stratifié.

- Correction : Utilisez les valeurs pour la fréquence spécifique et la teneur en résine du préimprégné utilisé. Demandez à APTPCB les paramètres matériels spécifiques pour votre empilement.

Négliger les stubs de via :

- Erreur : Acheminer un signal de la couche 1 à la couche 3 sur une carte à 20 couches et laisser le reste du via plaqué.

- Correction : Utilisez des vias aveugles/enterrés ou spécifiez le défonçage. Un long stub est un tueur pour les signaux supérieurs à 5 Gbps.

Se concentrer uniquement sur le PCB :

- Erreur : Perfectionner la disposition du PCB mais ignorer le connecteur et le câble.

- Correction : Effectuez une

corrélation SI multi-cartes. Le canal inclut tout ce qui se trouve entre la puce de l'émetteur et la puce du récepteur.

Oublier l'effet de la trame de fibre :

- Erreur : Acheminer les paires différentielles parallèlement à la trame de verre du matériau du PCB.

- Correction : Acheminer avec un léger angle (routage en zigzag) ou utiliser des matériaux "spread glass" pour éviter le skew où une branche de la paire passe sur le verre et l'autre sur la résine.

Ignorer l'intégrité de l'alimentation :

- Erreur : Supposer qu'un plan solide est suffisant.

- Correction : Effectuez une

analyse SI sensible à l'alimentation. Le bruit sur le rail d'alimentation se couple au signal, fermant le diagramme de l'œil (SSN).

Questions fréquentes (FAQ)

Pour clarifier davantage ces pièges potentiels, voici les réponses aux questions les plus fréquentes concernant la vérification de l'intégrité du signal.

Q : À quelle fréquence ai-je besoin d'une liste de contrôle formelle d'approbation SI ? R : Généralement, si le temps de montée de votre signal est inférieur à 1 ns, ou si les fréquences dépassent 500 MHz, les effets SI deviennent significatifs. Pour les interfaces comme DDR3/4, PCIe ou Gigabit Ethernet, c'est obligatoire.

Q : APTPCB peut-il aider au calcul de l'impédance ? A: Oui. Nous fournissons une assistance détaillée pour l'empilement et disposons d'un Calculateur d'impédance en ligne pour vous aider à estimer les largeurs de trace avant le début du routage.

Q: Quelle est la différence entre la simulation Pre-layout et Post-layout ? A: Le Pre-layout est destiné à l'exploration (définition des règles, de l'empilement et de la topologie). Le Post-layout est destiné à la vérification (vérification du cuivre réellement routé par rapport à ces règles).

Q: Comment le backdrilling affecte-t-il le coût ? A: Le backdrilling ajoute une étape au processus, augmentant légèrement le coût. Cependant, pour les conceptions de PCB haute vitesse, c'est souvent moins cher que d'utiliser des technologies de fabrication HDI coûteuses pour atteindre la même qualité de signal.

Q: Quelles données dois-je envoyer pour une révision SI ? A: Vous devez généralement fournir les fichiers ODB++ ou Gerber, la netlist IPC-356, l'empilement souhaité et un document spécifiant les objectifs de fréquence et les exigences d'impédance.

Q: Pourquoi ma simulation ne correspond-elle pas à la mesure en laboratoire ? A: Les écarts proviennent souvent de modèles de matériaux imprécis (Dk/Df), de l'ignorance des modèles de connecteurs ou de la non-prise en compte des tolérances de gravure de fabrication (formes de trace trapézoïdales).

Q: Qu'est-ce que la SI "Power Aware" ? A: C'est un mode de simulation qui tient compte des fluctuations des rails d'alimentation en tension pendant que les signaux commutent. La simulation SI standard suppose une alimentation électrique idéale et parfaite, ce qui est irréaliste.

Q: Ai-je besoin d'une simulation 3D pour chaque net ? R: Non. La simulation 3D prend du temps. Utilisez-la uniquement pour les réseaux haute vitesse critiques, les vias et les géométries complexes. Les solveurs 2D standard sont suffisants pour les signaux de commande à basse vitesse.

Glossaire (termes clés)

Pour plus de clarté pour toutes les équipes, nous définissons la terminologie technique utilisée tout au long de ce guide.

| Terme | Définition |

|---|---|

| Atténuation | La réduction de l'amplitude du signal lorsqu'il traverse le milieu (perte). |

| Défonçage (Backdrilling) | Un processus de fabrication pour retirer la partie inutilisée (moignon) d'un via traversant plaqué. |

| BER (Taux d'Erreur Binaire) | Le nombre d'erreurs binaires par unité de temps. Un objectif courant est $10^{-12}$. |

| Diaphonie | Couplage électromagnétique entre deux signaux adjacents (NEXT côté proche, FEXT côté lointain). |

| Dk (Constante Diélectrique) | Une mesure de la capacité d'un matériau à stocker de l'énergie électrique. Affecte la vitesse de propagation et l'impédance. |

| Df (Facteur de Dissipation) | Une mesure de l'énergie perdue sous forme de chaleur dans le matériau diélectrique. Affecte la perte d'insertion. |

| Diagramme de l'œil | Un affichage d'oscilloscope dans lequel un signal numérique est échantillonné de manière répétée pour montrer la qualité du signal. |

| Modèle IBIS | Spécification d'informations de tampon d'entrée/sortie. Un modèle comportemental du tampon du composant. |

| Impédance ($Z_0$) | L'opposition au flux de courant dans une ligne de transmission. Doit être adaptée pour éviter les réflexions. |

| ISI (Interférence Inter-Symboles) | Distorsion d'un signal où un symbole interfère avec les symboles suivants (causée par une perte/dispersion). |

| Gigue (Jitter) | L'écart par rapport à la vraie périodicité d'un signal supposé périodique (bruit de synchronisation). |

| PDN (Réseau de Distribution d'Alimentation) | Le système complet d'alimentation, incluant les VRM, les plans, les condensateurs et les vias. |

| Désalignement temporel (Skew) | La différence de temps entre deux signaux (par exemple, entre l'horloge et les données, ou P et N d'une paire différentielle). |

| Effet de Peau | La tendance du courant haute fréquence à ne circuler que sur la surface extérieure du conducteur. |

| Stub | Une branche à extrémité ouverte d'une ligne de transmission (souvent un via) qui provoque des réflexions. |

| TDR (Réflectométrie dans le Domaine Temporel) | Une technique de mesure utilisée pour déterminer le profil d'impédance d'une piste. |

Conclusion finale (prochaines étapes)

Réaliser une conception haute vitesse fiable est un processus systématique, pas un jeu de hasard. En adhérant à une liste de contrôle complète de validation SI, vous vous assurez que chaque aspect du canal de signal — de la puce de silicium au tissage du matériau du PCB — est pris en compte. Cela réduit le risque de prototypes coûteux échouant en laboratoire et accélère votre mise sur le marché.

La clé du succès réside dans une collaboration précoce. N'attendez pas que le routage soit terminé pour penser à l'intégrité du signal. Engagez-vous immédiatement dans la co-conception de l'empilement et de l'intégrité du signal.

Prêt à passer votre conception en production ? Pour garantir que votre carte haute vitesse est fabriquée exactement comme simulé, veuillez fournir à APTPCB les éléments suivants pendant la phase de devis :

- Fichiers Gerber/ODB++ : La disposition physique complète.

- Définition de l'empilement (stackup) : Incluant les demandes de matériaux spécifiques (par exemple, Rogers, Megtron ou FR4 à Tg élevé).

- Table d'impédance : Listant l'impédance cible, les largeurs de pistes et les couches de référence.

- Exigences SI : Tout besoin de test spécifique comme les rapports TDR ou les emplacements de défonçage (backdrilling).

Contactez APTPCB dès aujourd'hui pour examiner votre conception et vous assurer que votre prochain projet haute vitesse sera un succès dès le premier essai.