La technologie du carbure de silicium (SiC) a révolutionné l'électronique de puissance avec des vitesses de commutation plus rapides et une efficacité accrue, mais ces avantages introduisent de sérieux défis de conception de layout. La mise en œuvre des meilleures pratiques pour les PCB de drivers de grille d'onduleurs SiC est le seul moyen de prévenir les défaillances catastrophiques causées par l'inductance parasite, le ringing et les interférences électromagnétiques (EMI). Contrairement aux IGBT traditionnels, les MOSFET SiC commutent à des taux dV/dt extrêmement élevés, ce qui signifie que même quelques nanohenrys d'inductance parasite peuvent provoquer des dépassements de tension qui détruisent le composant ou corrompent le signal de grille.

Chez APTPCB (APTPCB PCB Factory), nous constatons que de nombreuses conceptions échouent non pas à cause du schéma, mais parce que le layout physique a ignoré la physique unique des semi-conducteurs à large bande interdite. Ce guide fournit une liste de contrôle complète, des plages de spécifications et des étapes de dépannage pour garantir que la conception de votre PCB de driver de grille d'onduleur SiC est robuste, fabricable et fiable.

Réponse Rapide (30 secondes)

Pour les ingénieurs ayant besoin d'une orientation immédiate sur les meilleures pratiques pour les PCB de drivers de grille d'onduleurs SiC, concentrez-vous avant tout sur la minimisation de la surface de la boucle.

- Minimiser l'inductance de la boucle de grille : Placez le driver de grille aussi près que physiquement possible du MOSFET SiC. La longueur totale de la trace devrait idéalement être inférieure à 20 mm.

- Utiliser les connexions Kelvin Source : Séparez toujours le chemin de la source d'alimentation du chemin de retour du driver de grille pour éviter que l'inductance de source commune ne ralentisse la commutation ou ne provoque de faux déclenchements.

- Optimiser les condensateurs de découplage : Placer des condensateurs céramiques à faible ESL (C0G/NP0) directement aux broches d'alimentation du driver.

- Contrôler l'immunité aux transitoires de mode commun (CMTI) : S'assurer que la barrière d'isolation (optocoupleur ou isolateur numérique) a une valeur CMTI >100 kV/µs et minimiser la capacité de couplage à travers l'espace d'isolation.

- Stratégie d'empilement des couches : Utiliser un empilement à 4 ou 6 couches avec un plan de masse solide immédiatement adjacent à la couche de signal pour se protéger du bruit.

- Distances d'isolement pour haute tension : Les onduleurs SiC fonctionnent souvent à 800V+ ; s'assurer que les distances de fuite et d'isolement respectent les normes IEC 60664-1 (typiquement >8mm pour une isolation renforcée).

Quand les meilleures pratiques pour les PCB de drivers de grille d'onduleurs SiC s'appliquent (et quand elles ne s'appliquent pas)

Comprendre quand appliquer strictement ces normes rigoureuses aide à équilibrer les coûts et les performances.

Quand appliquer strictement ces meilleures pratiques :

- Groupes motopropulseurs de VE haute tension : Systèmes fonctionnant avec des architectures de batterie de 400V ou 800V où le dV/dt dépasse 50 V/ns.

- Commutation haute fréquence : Convertisseurs fonctionnant au-dessus de 50 kHz où les pertes de commutation dominent et la résonance parasite est plus probable.

- Conceptions à haute densité de puissance : Onduleurs compacts où la gestion thermique et la proximité des composants augmentent le risque de diaphonie.

- Applications critiques pour la sécurité : Onduleurs de traction automobile ou robotique industrielle où un défaut d'allumage de la grille pourrait entraîner la destruction du matériel ou des risques pour la sécurité.

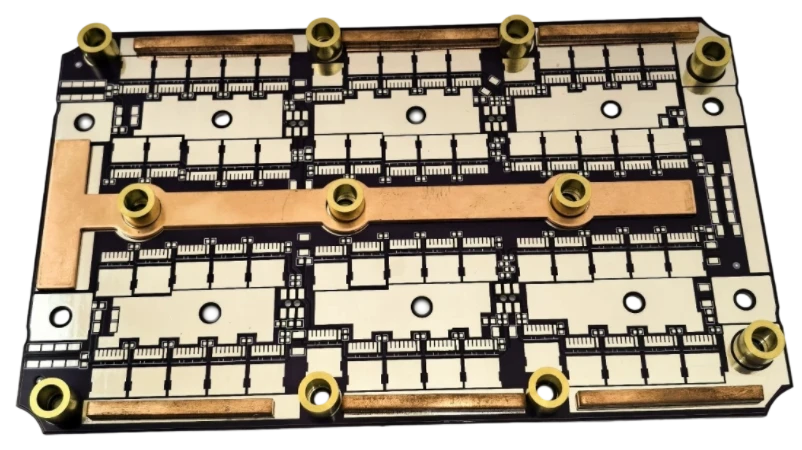

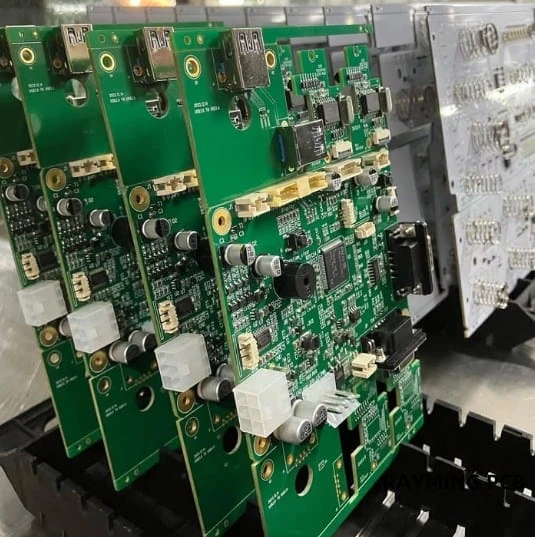

- Assemblage de PCB de pilote de grille d'onduleur SiC : Lorsque le processus d'assemblage implique des puces nues sensibles ou des composants montés en surface densément regroupés qui nécessitent un contrôle précis de la pâte à souder.

Quand les pratiques PCB standard pourraient suffire (et ces règles sont excessives) :

- MOSFETs en silicium basse tension : Si vous utilisez des FET en silicium standard de 24V ou 48V avec des vitesses de commutation lentes, les règles de routage standard sont généralement suffisantes.

- Entraînements IGBT basse fréquence : Les entraînements de moteur hérités commutant à <5 kHz sont moins sensibles à l'inductance parasite par rapport au SiC.

- Électronique grand public sensible aux coûts : Adaptateurs de faible puissance où les gains d'efficacité du SiC ne justifient pas l'augmentation du coût de fabrication du PCB pour des matériaux spécialisés.

- Prototypage sur platines d'expérimentation : Bien que non recommandé pour l'alimentation, les tests logiques initiaux à basse tension ne nécessitent pas de contrôle d'impédance (bien que cela ne reflète pas les performances réelles).

Règles et spécifications

En fonction du contexte d'application, des règles paramétriques spécifiques doivent être définies pour guider le processus de routage. Le tableau suivant présente les spécifications critiques pour les meilleures pratiques de PCB de pilote de grille d'onduleur SiC.

| Règle | Valeur/Plage recommandée | Pourquoi c'est important | Comment vérifier | Si ignoré |

|---|---|---|---|---|

| Longueur de la piste de grille | < 20 mm (Max) | Réduit l'inductance parasite ($L_g$) qui provoque des oscillations. | Mesurer dans l'outil de routage CAO. | Oscillation de grille, destruction potentielle du MOSFET. |

| Largeur de la Piste de Grille | > 20 mils (0,5 mm) | Réduit la résistance et l'inductance; gère les courants de pointe (souvent >5A). | Vérifier les contraintes de largeur de piste. | Commutation lente, pistes surchauffées. |

| Zone de Boucle de Grille | Minimiser (Couplage étroit) | Les grandes boucles agissent comme des antennes pour les EMI et augmentent l'inductance. | Inspection visuelle; faire passer des pistes superposées sur des couches adjacentes. | EMI élevées, faux allumage (effet Miller). |

| Distance de Fuite d'Isolation | > 8 mm (pour systèmes 800V) | Prévient l'amorçage à travers la barrière d'isolation. | DRC (Design Rule Check) dans le CAD. | Claquage diélectrique, défaillance de sécurité. |

| Indice CMTI | > 100 kV/µs | Les commutateurs SiC sont rapides; les composants à faible CMTI présenteront des glitches pendant les transitions. | Vérifier la fiche technique du composant. | Perte de contrôle de la grille pendant la commutation. |

| Distance du Condensateur de Découplage | < 2 mm de la broche | Fournit un courant instantané pour la commutation; stabilise VDD. | Vérification visuelle du placement. | Chute de VDD, comportement erratique du pilote. |

| Inductance du Via | Minimiser (Utiliser plusieurs vias) | Les vias uniques ajoutent ~1nH; plusieurs vias en parallèle réduisent cela. | Compter les vias sur les chemins à courant élevé. | Impédance de chemin accrue, oscillations. |

| Espacement des Pistes de Désaturation | > 0,5 mm de séparation | La détection de désaturation est sensible au couplage de bruit. | Règles de dégagement DRC. | Faux déclenchement de défaut. |

| Plan de Masse | Solide, Ininterrompu | Fournit un chemin de retour et un blindage. | Examiner les fichiers Gerber pour les divisions. | Rebond de masse, perte d'intégrité du signal. |

| Poids du Cuivre | 2 oz ou plus | Gère des courants continus élevés et favorise la dissipation thermique. | Spécifier dans les notes de fabrication. | Points chauds thermiques, fusion des pistes. |

| Tg du Matériau | > 170°C (Tg élevée) | Le SiC chauffe beaucoup ; le FR4 standard peut se délaminer. | Vérifier la fiche technique du matériau (ex. Isola 370HR). | Délaminage du PCB, fissures dans les barillets. |

| Symétrie | Correspondance côté Haut/Bas | L'asymétrie provoque un décalage temporel et une contrainte inégale. | Mesurer les longueurs de chemin pour le pont en H. | Risque de court-circuit traversant, charge thermique inégale. |

Étapes d'implémentation

Une fois les spécifications comprises, la conception doit être exécutée méthodiquement. Voici le flux de travail étape par étape pour l'implémentation des meilleures pratiques pour les PCB de pilotes de grille d'onduleur SiC.

- Stratégie de placement des composants

- Action : Placer d'abord les MOSFETs SiC et les CI de pilote de grille.

- Paramètre clé : Distance < 20mm.

- Vérification d'acceptation : Vérifier que la broche de sortie du pilote fait directement face à la broche de grille du MOSFET pour éviter les pistes sinueuses.

- Routage de la source Kelvin

- Action : Acheminer la piste de retour de grille directement vers la broche de source du MOSFET, séparément du plan de masse principal.

- Paramètre clé : Le point de connexion Kelvin doit être sur le pad.

- Vérification d'acceptation : S'assurer que la "Source d'Alimentation" et la "Source du Pilote" ne partagent pas de chemin jusqu'à la broche du MOSFET.

- Optimisation de la boucle de grille

- Action : Acheminer les pistes de grille et de retour sur des couches adjacentes (par exemple, Couche 1 et Couche 2) exactement l'une au-dessus de l'autre.

- Paramètre clé: Inductance de boucle < 10 nH.

- Vérification d'acceptation: Utiliser un visualiseur de PCB ou un outil 3D pour visualiser la zone de la boucle; elle devrait ressembler à une ligne, pas à un cercle.

- Minimisation de la boucle de puissance

- Action: Placer le condensateur de liaison DC aussi près que possible du demi-pont pour minimiser la boucle de commutation.

- Paramètre clé: Inductance du bus < 20 nH.

- Vérification d'acceptation: Vérifier que les plaques de bus positives et négatives se chevauchent fortement pour annuler les champs magnétiques.

- Conception de la barrière d'isolation

- Action: Créer une zone "keep-out" claire sous les composants d'isolation (optocoupleurs/transformateurs). Retirer tout le cuivre des couches internes dans cette zone.

- Paramètre clé: Distance de fuite > 8mm (dépend du système).

- Vérification d'acceptation: Exécuter un DRC Haute Tension pour s'assurer qu'aucun cuivre n'empiète sur l'espace d'isolation.

- Disposition du condensateur de découplage

- Action: Placer les condensateurs céramiques C0G/NP0 immédiatement aux broches VDD/VEE du driver.

- Paramètre clé: Longueur de la trace vers le condensateur < 2mm.

- Vérification d'acceptation: S'assurer que les vias connectant les condensateurs à la masse sont doublés ou triplés pour réduire l'inductance.

- Raccordement de vias thermiques

- Action: Placer des réseaux de vias thermiques sous les pads exposés du driver et des MOSFET.

- Paramètre clé: Diamètre du via 0.3mm, pas 0.6mm.

- Vérification d'acceptation : Vérifier que l'ouverture du masque de soudure permet la dissipation de la chaleur mais empêche la remontée de la soudure (un tenting ou un bouchage peut être nécessaire).

- Examen DFM pour l'assemblage

- Action : Vérifier l'espacement des composants pour le placement automatisé, en particulier pour les cartes à cuivre épais.

- Paramètre clé : Espacement minimum des composants.

- Vérification d'acceptation : Consulter les directives DFM pour s'assurer que la conception est fabricable à grande échelle.

Modes de défaillance et dépannage

Même avec un processus de conception rigoureux, des problèmes peuvent survenir lors des tests. Le dépannage des meilleures pratiques pour les PCB de pilotes de grille d'onduleurs SiC nécessite l'identification de symptômes spécifiques qui indiquent des défauts de conception.

Symptôme : Oscillation excessive sur la tension de grille

- Cause : Inductance parasite élevée dans la boucle de grille.

- Vérification : Mesurer la longueur de la piste du pilote à la grille. Vérifier la présence de vias dans le chemin de grille.

- Correction : Raccourcir les pistes ; supprimer les vias si possible. Ajouter une perle de ferrite ou augmenter légèrement la résistance de grille ($R_g$) (compromis avec la vitesse de commutation).

- Prévention : Utiliser un routage en stripline ou microstrip avec un plan de masse immédiatement en dessous.

Symptôme : Faux allumage (effet Miller)

- Cause : Couplage dV/dt élevé via la capacité de Miller ($C_{gd}$) qui augmente la tension de grille.

- Vérification : Rechercher des pics de tension sur la grille du dispositif ÉTEINT lorsque le dispositif ALLUMÉ commute.

- Correction : Implémenter un Active Miller Clamp ou utiliser une tension d'extinction négative (par exemple, -5V).

Prévention : Maintenir l'impédance du chemin de coupure de la grille extrêmement basse.

Symptôme : Verrouillage (Latch-Up) ou Réinitialisation du Driver

- Cause : Violation de l'immunité aux transitoires en mode commun (CMTI) ou rebond de masse.

- Vérification : Vérifier la tension d'isolement du driver. Vérifier la différence de potentiel de masse entre les côtés logique et puissance.

- Solution : Ajouter des selfs de mode commun ; améliorer la capacité d'isolement.

- Prévention : Sélectionner des drivers de grille avec CMTI > 100 kV/µs.

Symptôme : Surchauffe du MOSFET (Statique)

- Cause : Tension de grille n'atteignant pas la pleine saturation (par exemple, 15V ou 18V) ou mauvais chemin thermique.

- Vérification : Mesurer $V_{gs}$ à la broche. Vérifier la continuité du via thermique.

- Solution : Augmenter la largeur de la piste pour l'alimentation du driver ; améliorer la fixation du dissipateur thermique.

- Prévention : Utiliser du cuivre épais (2oz+) et des substrats thermiques haute performance.

Symptôme : Échec du test EMI/EMC

- Cause : Grandes boucles de commutation de puissance agissant comme des antennes.

- Vérification : Analyser la zone physique de la boucle DC+ à DC- incluant l'interrupteur.

- Solution : Ajouter des circuits snubber (RC ou RCD) ; améliorer le blindage.

- Prévention : Conception de barres omnibus laminaires ou plans de puissance PCB superposés.

Symptôme : Claquage diélectrique (Arcing)

- Cause : Distances de fuite/d'isolement insuffisantes pour l'altitude de fonctionnement ou le degré de pollution.

- Vérification : Inspecter le PCB pour des traces de carbone ou des brûlures à travers les espaces d'isolement.

Correction : Fraiser des fentes (découpes) dans le PCB pour augmenter la distance de fuite.

Prévention : Suivre strictement les tableaux de la norme IEC 60664-1 lors de la conception.

Décisions de conception

Le dépannage ramène souvent aux choix de conception fondamentaux faits au début du projet.

Sélection de l'empilement des couches Pour les onduleurs SiC, une carte standard à 2 couches est rarement suffisante en raison du besoin de faible inductance.

- Empilement à 4 couches : Signal / Masse / Alimentation / Signal. C'est le minimum recommandé. Le plan de masse interne agit comme un blindage et réduit l'inductance de boucle pour les pistes de la couche supérieure.

- Empilement à 6 couches : Permet des couches de blindage dédiées et une meilleure isolation entre la logique haute tension et basse tension.

Sélection des matériaux Le FR4 standard (Tg 130-140°C) pourrait ne pas résister aux cycles thermiques des applications SiC haute puissance.

- FR4 à Tg élevé : Des matériaux comme Isola 370HR (Tg 180°C) sont recommandés pour la fiabilité.

- Cuivre épais : L'utilisation de cuivre de 2oz, 3oz ou même 4oz aide à la dissipation thermique et à la réduction de la résistance des pistes à courant élevé.

Topologie du pilote de grille

- Isolé vs. Non-isolé : Les onduleurs haute tension nécessitent invariablement une isolation galvanique (optique, capacitive ou magnétique).

- Alimentation bipolaire : L'utilisation de +15V/-5V est une décision de conception standard pour éviter les activations intempestives, nécessitant des considérations spécifiques de disposition de l'alimentation sur le PCB.

Questions fréquentes (FAQ)

Q : Quelle est la règle la plus critique pour la disposition du pilote de grille SiC ? A: La minimisation de l'inductance de la boucle de grille est la plus critique.

- Gardez les pistes courtes (<20mm).

- Faites passer les pistes de grille et de retour parallèles et proches l'une de l'autre.

- Évitez les vias dans le chemin de grille.

Q: Ai-je vraiment besoin d'une tension de grille négative pour le SiC? R: Bien que certains FET SiC puissent fonctionner à 0V à l'état bloqué, une tension négative (de -3V à -5V) est fortement recommandée.

- Elle offre une marge de sécurité contre l'activation par effet Miller.

- Elle accélère les temps de désactivation.

Q: Puis-je utiliser du FR4 standard pour les PCB d'onduleurs SiC? R: Cela dépend de la température et de la tension.

- Pour les prototypes ou les faibles puissances, le FR4 standard convient.

- Pour les applications à haute densité de puissance ou automobiles, utilisez des matériaux à Tg élevé pour prévenir les défaillances thermiques.

Q: Comment calculer la distance de fuite requise? R: Référez-vous aux normes comme IEC 60664-1.

- Déterminez la tension de fonctionnement (par exemple, 800V).

- Déterminez le degré de pollution (généralement 2 pour scellé, 3 pour ouvert).

- Sélectionnez le groupe de matériaux (valeur CTI).

Q: Pourquoi le CMTI est-il important pour le SiC? R: Les commutateurs SiC ont des transitoires de tension très rapides (dV/dt élevé).

- Les pilotes à faible CMTI interprètent ce bruit comme un signal.

- Cela provoque des glitches ou une perte de synchronisation.

Q: Comment la largeur de la piste affecte-t-elle le pilote de grille? R: Les pistes fines ont une inductance et une résistance plus élevées.

- Cela limite le courant de crête que le pilote peut pousser/tirer.

- Cela ralentit la commutation, augmentant les pertes de commutation.

Q: Dois-je utiliser une perle sur la grille? R: Une perle de ferrite peut supprimer le ringing à haute fréquence.

- Il ajoute de la résistance aux hautes fréquences sans affecter la commande en courant continu.

- Placez-le près de la broche de grille.

Q: Quel est l'avantage des connexions de source Kelvin? R: Cela contourne l'inductance de source commune.

- La boucle de grille ne voit pas la chute de tension causée par le courant de charge principal.

- Cela se traduit par une commutation plus propre et plus rapide.

Q: Comment vérifier le contrôle d'impédance sur les pistes de grille? R: Utilisez un calculateur d'impédance pendant la conception.

- Définissez l'empilement et la constante diélectrique.

- Ajustez la largeur de la piste pour correspondre à l'impédance cible (bien que la minimisation de l'inductance soit généralement prioritaire sur l'adaptation d'impédance sur de courtes distances).

Q: Quel est le délai de fabrication des PCB de qualité SiC? R: Cela varie en fonction de la complexité et de la disponibilité des matériaux.

- Cartes High Tg standard: 3-5 jours.

- Cuivre épais ou substrats spécialisés: 7-10 jours.

Pages et outils associés

Pour vous aider davantage avec les meilleures pratiques pour les PCB de pilotes de grille d'onduleurs SiC, utilisez ces ressources:

- Calculateur d'impédance PCB: Essentiel pour calculer la largeur et l'espacement des pistes afin de gérer l'inductance et l'impédance.

- Directives DFM: Assurez-vous que votre conception respecte les contraintes de fabrication pour éviter des refontes coûteuses.

- Obtenir un devis: Prêt à fabriquer? Téléchargez vos fichiers Gerber pour une estimation rapide des coûts.

Glossaire (termes clés)

| Terme | Définition | Pertinence pour les PCB SiC |

|---|---|---|

| :--- | :--- | :--- |

| SiC (Carbure de Silicium) | Un matériau semi-conducteur à large bande interdite permettant une tension plus élevée et une commutation plus rapide que le silicium. | La technologie de base nécessitant des règles de routage de PCB spécialisées. |

| dV/dt | Le taux de changement de tension par rapport au temps. | Un dV/dt élevé dans le SiC crée du bruit et nécessite des pilotes à CMTI élevé. |

| Inductance Parasite | Inductance indésirable inhérente aux pistes de PCB et aux broches des composants. | L'ennemi principal de la commutation rapide ; provoque des oscillations et des dépassements. |

| Effet Miller | Un phénomène où la capacité ($C_{gd}$) couple la tension à la grille, la mettant potentiellement en conduction. | Nécessite une commande de grille négative ou des pinces de Miller dans la conception du PCB. |

| Connexion Kelvin | Une technique de mesure à 4 fils appliquée au routage de PCB pour séparer les chemins de force et de détection. | Critique pour isoler le chemin de retour de la grille des chemins de puissance à courant élevé. |

| CMTI | Immunité aux Transitoires en Mode Commun ; la capacité d'un isolateur à rejeter le bruit transitoire rapide. | Doit être élevé (>100 kV/µs) pour éviter la corruption du pilote. |

| Désaturation (Desat) | Une méthode de protection qui détecte si le MOSFET est en état de court-circuit. | Nécessite un routage soigné des pistes de détection pour éviter les déclenchements intempestifs. |

| Zone de Boucle | La zone physique délimitée par un chemin de courant et son retour. | Doit être minimisée pour réduire les EMI et l'inductance. |

| Distance de fuite | La distance la plus courte entre deux parties conductrices le long de la surface de l'isolation. | Critique pour l'isolation de sécurité haute tension. |

| Distance dans l'air | La distance la plus courte entre deux parties conductrices à travers l'air. | Prévient les arcs électriques dans les conceptions haute tension. |

| Résistance de grille ($R_g$) | Une résistance placée en série avec la grille pour contrôler la vitesse de commutation et amortir les oscillations. | Le placement et la sélection de la valeur sont des paramètres de réglage clés. |

| C0G/NP0 | Un type de diélectrique de condensateur céramique à haute stabilité. | Recommandé pour le découplage et la synchronisation dans des environnements thermiques difficiles. |

Conclusion finale

La mise en œuvre des meilleures pratiques pour les PCB de pilotes de grille d'onduleurs SiC ne consiste pas seulement à suivre une liste de contrôle ; il s'agit de respecter la physique de la commutation à haute vitesse et haute tension. En minimisant l'inductance de boucle, en assurant une isolation robuste et en sélectionnant les bons matériaux, vous pouvez libérer tout le potentiel d'efficacité de la technologie du carbure de silicium sans sacrifier la fiabilité.

Que vous prototypiez un nouvel onduleur de traction pour VE ou que vous optimisiez une alimentation industrielle, la disposition est le fondement de votre succès. APTPCB est spécialisée dans la fabrication de PCB haute performance qui répondent à ces exigences rigoureuses. Si vous avez votre conception prête ou si vous avez besoin de conseils sur le choix des matériaux pour votre prochain projet SiC, contactez-nous pour une évaluation de fabrication.