Points clés à retenir

Avant de plonger dans les profondeurs techniques des interconnexions quantiques, voici les points essentiels que les équipes d'ingénierie doivent comprendre.

- L'importance du matériau : Le fil d'or standard est souvent inadapté aux qubits supraconducteurs en raison de sa résistance résiduelle ; l'aluminium (1 % de silicium) est la norme pour les environnements cryogéniques.

- L'inductance est parasitaire : La longueur et la hauteur de la boucle de la liaison filaire ajoutent directement de l'inductance, ce qui peut désaccorder la fréquence du qubit.

- Critique de la finition de surface : Les matériaux magnétiques (comme le nickel standard dans l'ENIG) détruisent la cohérence des qubits ; les finitions non magnétiques comme l'ENEPIG ou l'or doux sont obligatoires.

- Contrainte mécanique : L'interface doit survivre à des cycles thermiques répétés, de la température ambiante (300 K) aux plages de milliKelvin (mK), sans se décoller.

- Réponse en fréquence : La liaison filaire agit comme une discontinuité dans la ligne de transmission ; maintenir les liaisons courtes minimise le désaccord d'impédance.

- Validation : Les tests de continuité à température ambiante sont insuffisants ; les rapports de résistance CC (RRR) et les tests de traction cryogéniques sont souvent nécessaires.

Ce que signifie réellement le wirebonding pour l'interface de qubit (portée et limites)

Comprendre les exigences fondamentales du wirebonding pour l'interface de qubit commence par reconnaître que la fiabilité standard IPC Classe 3 n'est pas suffisante pour les applications quantiques. Dans l'électronique traditionnelle, le câblage par fil (wirebonding) connecte une puce de silicium à un cadre de connexion ou à un PCB pour transmettre des signaux de puissance et logiques. Dans le domaine quantique, le câblage par fil pour l'interface de qubit a un double objectif : il assure la connectivité électrique tout en maintenant l'état quantique délicat (cohérence) du qubit. Cette interface fonctionne dans un régime où les photons uniques sont importants, et le bruit thermique doit être pratiquement inexistant.

La portée de ce processus diffère de l'assemblage standard de trois manières :

- Régime thermique : La liaison doit conserver son intégrité mécanique à des températures proches du zéro absolu (10 mK à 4 K).

- Environnement électromagnétique : La boucle de fil elle-même devient un élément rayonnant. Si elle n'est pas contrôlée, elle agit comme une antenne, captant du bruit ou rayonnant de l'énergie qui provoque la décohérence.

- Supraconductivité : Pour les qubits supraconducteurs, la liaison par fil elle-même doit souvent devenir supraconductrice pour éviter la dissipation d'énergie (échauffement) au point de connexion.

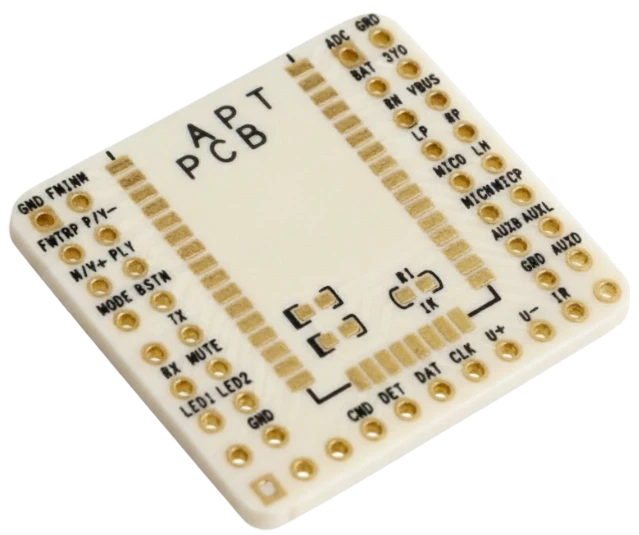

APTPCB (APTPCB PCB Factory) conseille souvent à ses clients que la conception du substrat (PCB) et le processus d'assemblage (câblage par fil) ne peuvent pas être traités séparément dans les applications quantiques. La géométrie des plots sur le PCB dicte la forme de la liaison, ce qui à son tour dicte l'inductance.

Métriques importantes pour le câblage par fil d'interface de qubit (comment évaluer la qualité)

Une fois le périmètre défini, les ingénieurs doivent quantifier le succès en utilisant des métriques spécifiques qui vont au-delà des forces de traction standard. Le tableau suivant présente les indicateurs de performance critiques pour une interface quantique de haute qualité.

| Métrique | Pourquoi c'est important | Plage typique / Facteur | Comment mesurer |

|---|---|---|---|

| Inductance parasite | Une inductance élevée modifie la fréquence de résonance du qubit et limite la bande passante. | 0,5 nH à 2,0 nH (dépend de la géométrie) | VNA (Analyseur de réseau vectoriel) ou simulation TDR. |

| Résistance au cisaillement du fil | Assure la fiabilité mécanique lors de la contraction/dilatation thermique. | > 5 grammes (selon le diamètre du fil) | Testeur de liaison Dage (test de cisaillement). |

| Courant critique (Ic) | Le courant maximal que la liaison peut supporter sans rompre la supraconductivité. | > 10 mA (spécifique à l'application) | Mesure à 4 points de sonde à des températures cryogéniques. |

| Désadaptation d'impédance | Les réflexions à l'interface de liaison provoquent une perte de signal et des ondes stationnaires. | Cible 50 Ohms (VSWR < 1,2) | TDR (Réflectométrie dans le domaine temporel). |

| Rapport de résistance résiduelle (RRR) | Indique la pureté du métal et ses performances à basses températures. | > 10 pour les fils d'Al | Rapport de la résistance à 300K vs 4K. |

| Cohérence de la hauteur de boucle | Les variations de hauteur modifient l'inductance, entraînant une dispersion de la fréquence du qubit. | Tolérance de ± 10 µm | Profilage optique / AOI 3D. |

Comment choisir le fil de liaison pour l'interface de qubit : guide de sélection par scénario (compromis)

Une fois les métriques établies, l'étape suivante consiste à sélectionner la bonne stratégie de liaison en fonction de votre architecture quantique spécifique. Différentes modalités de qubits (supraconducteurs, spin, ions piégés) imposent des contraintes différentes au processus de câblage (wirebonding).

Scénario 1 : Qubits Transmon Supraconducteurs

- Exigence : Chemin de résistance nulle et bruit magnétique minimal.

- Recommandation : Soudure par coin en aluminium (Aluminum Wedge Bonding).

- Compromis : Les fils d'aluminium sont plus difficiles à souder sur certaines surfaces en or que les fils d'or. Vous devez vous assurer que la finition de surface du PCB est compatible (par exemple, or doux épais ou plots en aluminium). La soudure par coin ultrasonique est préférée à la soudure par bille thermosonique pour éviter de chauffer les jonctions Josephson sensibles.

Scénario 2 : Qubits de Spin dans le Silicium

- Exigence : Lignes de grille haute densité, moins sensibles au bruit magnétique que les transmons, mais l'espace est limité.

- Recommandation : Soudure par bille en or (si une barrière non magnétique est utilisée).

- Compromis : L'or est plus facile à souder et permet un pas plus serré (pas fin). Cependant, l'or n'est pas un supraconducteur. Si les lignes transportent un courant significatif, la dissipation thermique devient un problème.

Scénario 3 : Lignes de Contrôle Haute Fréquence (4-8 GHz)

- Exigence : L'adaptation d'impédance est primordiale pour éviter la réflexion du signal.

- Recommandation : Soudure par ruban (Ribbon Bonding).

- Compromis : L'utilisation d'un ruban plat au lieu d'un fil rond réduit l'inductance et améliore l'adaptation d'impédance pour se rapprocher de 50 Ohms. Le compromis est que la liaison par ruban nécessite des outils de coin spécialisés et des plots de liaison plus grands sur le PCB haute fréquence.

Scénario 4 : Intégration 3D / Modules multi-puces

- Exigence : Connexion de plusieurs puces quantiques verticalement ou horizontalement.

- Recommandation : Liaison par coin à boucle courte.

- Compromis : Garder les boucles extrêmement courtes minimise l'inductance mais augmente la contrainte mécanique pendant le cyclage thermique. Le désalignement du CTE (Coefficient de Dilatation Thermique) entre la puce et l'interposeur doit être minimal.

Scénario 5 : Réglage et ajustement de fréquence

- Exigence : Ajustement de l'inductance après fabrication.

- Recommandation : Profilage de boucle adaptatif.

- Compromis : Similaire au réglage et à l'ajustement précis d'antenne dans la fabrication RF, la forme de la liaison filaire peut être ajustée pour "régler" l'inductance. Cela nécessite un équipement de liaison très avancé capable de profils de boucle complexes, augmentant les coûts de fabrication.

Scénario 6 : Prototypage rapide

- Exigence : Délai d'exécution rapide pour tester les conceptions de puces.

- Recommandation : Liaison par coin manuelle ou semi-automatique.

- Compromis : Le bonding manuel est plus lent et moins constant (variation d'inductance plus élevée) mais permet des tests immédiats sans programmation complexe. Convient pour la preuve de concept, pas pour la production.

Points de contrôle pour l'implémentation de l'interface de qubit par wirebonding (de la conception à la fabrication)

Choisir la bonne méthode n'est que la moitié du chemin ; des protocoles d'implémentation rigoureux sont nécessaires pour garantir que l'interface survive à la transition de la conception au réfrigérateur à dilution.

Phase 1 : Conception du PCB/Substrat

- Sélection de la finition de surface : Spécifier ENEPIG (Nickel autocatalytique, Palladium autocatalytique, Or par immersion) ou Or mou. Éviter le HASL standard ou l'Étain par immersion. S'assurer que la couche de Nickel est non magnétique (haute teneur en phosphore) si elle est utilisée, ou l'éliminer entièrement.

- Géométrie des plots : Concevoir les plots pour accueillir le « pied » du wedge bond. Pour le ribbon bonding, les plots doivent être rectangulaires et alignés avec le chemin du signal.

- Mise à la terre : Entourer les plots de signal avec des vias de masse (configuration masse-signal-masse) pour maintenir l'impédance jusqu'au point de liaison.

Phase 2 : Approvisionnement en matériaux

- Pureté du fil : S'approvisionner en fil d'aluminium 99,999 % (5N) ou d'aluminium-1 % silicium. Les impuretés diffusent les électrons et brisent la supraconductivité.

- Qualité du substrat : Utiliser des PCB céramiques (Alumine ou Nitrure d'aluminium) pour une meilleure adaptation thermique avec les puces de silicium par rapport au FR4.

Phase 3 : Préparation avant le bonding

- Nettoyage au plasma : Mettez en œuvre un cycle de nettoyage au plasma Argon/Oxygène immédiatement avant le collage pour éliminer les contaminants organiques des plots. Ceci est essentiel pour la fiabilité du collage par coin.

- Dégazage : Éliminez l'humidité du substrat. L'humidité piégée dans le PCB peut se dégazer dans la chambre à vide ou geler/se dilater pendant le refroidissement, fissurant la liaison.

Phase 4 : Processus de collage

- Optimisation des paramètres : Effectuez un DOE (plan d'expériences) pour la puissance ultrasonique, le temps et la force. La fenêtre pour les puces quantiques est étroite – trop de puissance endommage le qubit ; trop peu entraîne des décollements.

- Contrôle de la boucle : Programmez la machine de collage pour des profils de "boucle basse" ou de "boucle plate" afin de minimiser l'inductance parasite.

Phase 5 : Validation post-collage

- Test de traction non destructif : Appliquez une très légère force (par exemple, 1g) pour s'assurer qu'il n'y a pas de "fausses liaisons".

- Inspection visuelle : Vérifiez les fissures au talon et la précision du placement de la liaison.

- Qualification cryogénique : Échantillonnez aléatoirement des unités pour des tests de choc thermique (immersion dans l'azote liquide) suivis de vérifications de continuité.

Le collage de fils pour les interfaces de qubits : erreurs courantes (et la bonne approche)

Même les ingénieurs expérimentés rencontrent des pièges lorsqu'ils passent des interconnexions classiques aux interconnexions quantiques.

Erreur 1 : Utilisation de sous-couches magnétiques

- L'erreur : Utilisation de l'ENIG standard (Nickel Chimique Or par Immersion) où la couche de Nickel est magnétique.

- La Conséquence : Le champ magnétique du nickel perturbe l'état de spin ou le flux du qubit, réduisant le temps de cohérence.

- La Solution : Spécifier du nickel-phosphore non magnétique ou utiliser une finition directe or sur cuivre ou argent.

Erreur 2 : Ignorer le désalignement du CTE

- L'Erreur : Souder une puce de silicium directement sur une carte FR4 standard avec des fils courts et serrés.

- La Conséquence : Lorsqu'il est refroidi à 10 mK, le FR4 se contracte beaucoup plus que le silicium. La tension fait casser les fils.

- La Solution : Utiliser un interposeur adapté au CTE ou laisser une "boucle de service" (mou) dans le fil, bien que cela entraîne un compromis sur l'inductance.

Erreur 3 : Sur-liaison (Trop de force/puissance)

- L'Erreur : Appliquer une énergie ultrasonique élevée pour assurer une forte adhérence.

- La Conséquence : Cela peut créer des cratères (micro-fissures) dans le substrat sous-jacent ou endommager les délicates jonctions Josephson sur la puce.

- La Solution : Utiliser l'énergie minimale requise pour une liaison fiable. Valider d'abord par des tests de cisaillement sur des échantillons factices.

Erreur 4 : Longues boucles de fil

- L'Erreur : Permettre de grandes boucles arquées pour faciliter le dégagement de la liaison.

- La Conséquence : Augmente considérablement l'inductance ($L \approx 1 \text{nH/mm}$). Cela agit comme un filtre passe-bas et crée des discontinuités d'impédance.

- La Solution : Garder les liaisons aussi courtes et plates que possible. Placer la cavité de la puce ou l'étagère du PCB à la même hauteur que la surface de la puce (montage affleurant).

Erreur 5 : Négliger l'élimination de l'oxyde sur l'aluminium

- L'erreur : Le collage sur des plots en aluminium qui se sont oxydés sans nettoyage approprié.

- La conséquence : Des contacts à haute résistance ou des liaisons non adhérentes.

- La solution : Un nettoyage agressif au plasma ou un frottement mécanique (faisant partie de l'action de thermosoudage par coin) est nécessaire pour briser la couche d'oxyde.

Erreur 6 : Supposer que les tests à température ambiante équivalent aux performances cryogéniques

- L'erreur : Valider une unité uniquement sur la base de contrôles de continuité à 300K.

- La conséquence : Les liaisons peuvent échouer mécaniquement lors du refroidissement (circuit "ouvert") ou présenter une résistance non linéaire.

- La solution : Effectuer des tests de "trempage à froid" sur des lots d'échantillons.

Questions fréquentes (FAQ) sur le câblage pour l'interface de qubit (coût, délai, matériaux, tests, critères d'acceptation)

Q : Comment le câblage pour l'interface de qubit affecte-t-il le coût de l'assemblage de PCB ? R : Il augmente les coûts en raison de la nécessité de matériaux spécialisés (fil d'Al de haute pureté), de substrats spécialisés (céramique ou Rogers) et du débit plus faible du thermosoudage par coin de précision par rapport au thermosoudage par bille à grande vitesse. De plus, les NRE (Non-Recurring Engineering) pour la mise en place des profils de boucles sont plus élevés.

Q : Quel est le délai typique pour les substrats adaptés au câblage quantique ? R : Le FR4 standard est rapide, mais les substrats de qualité quantique comme l'alumine ou les stratifiés haute fréquence ont souvent des délais de 3 à 5 semaines. APTPCB propose des services accélérés pour l'assemblage NPI afin de réduire ce délai. Q: Pouvons-nous utiliser du fil de cuivre au lieu de l'aluminium pour une meilleure conductivité ? A: Généralement, non. Le cuivre s'oxyde rapidement et est plus dur, nécessitant des forces de liaison plus élevées qui peuvent endommager la puce. De plus, l'aluminium devient supraconducteur à 1,2 K, ce qui en fait un conducteur parfait sans résistance pour les circuits quantiques, alors que le cuivre ne l'est pas.

Q: Quels sont les critères d'acceptation pour une liaison filaire quantique ? A: Les critères incluent généralement :

- Résistance au cisaillement > X grammes (basée sur le diamètre du fil).

- Précision de placement à ±10 µm près.

- Variation de la hauteur de la boucle < 5 µm.

- Aucune fissure au talon visible à un grossissement de 100x.

- Résistance CC < 0,5 Ohms (à température ambiante).

Q: Comment testez-vous les liaisons filaires sans détruire le qubit ? A: Nous utilisons des "coupons témoins" ou des puces factices liées avec les mêmes paramètres pour les tests destructifs (traction/cisaillement). Les puces quantiques réelles subissent une inspection visuelle à 100 % (AOI) et des vérifications de continuité à faible courant si la conception le permet.

Q: Pourquoi parle-t-on de "réglage et ajustement d'antenne" dans le contexte du wirebonding ? A: Bien qu'il s'agisse principalement d'un terme RF, le concept s'applique ici. La boucle de fil agit comme un inducteur. En ajustant précisément la forme de la boucle (en ajustant la longueur/hauteur), les ingénieurs peuvent "accorder" l'impédance de l'interconnexion pour qu'elle corresponde à la ligne de transmission, minimisant ainsi la perte de signal.

Q: APTPCB gère-t-il le wirebonding ou seulement la fabrication de PCB ? A: APTPCB propose des solutions clés en main. Nous fabriquons le substrat haute performance et pouvons gérer le processus PCBA, y compris les exigences de liaison spécialisées par l'intermédiaire de nos partenaires d'assemblage avancés.

Ressources pour le wirebonding d'interface de qubit (pages et outils connexes)

Pour vous aider davantage dans votre processus de conception, utilisez les ressources suivantes disponibles sur notre plateforme.

- Sélection de substrat : Explorez les capacités de PCB céramique pour la stabilité cryogénique.

- Intégrité du signal : Utilisez notre calculateur d'impédance pour concevoir vos pistes avant qu'elles n'atteignent le plot de wirebonding.

- Finitions de surface : Lisez à propos des finitions de surface de PCB pour choisir la bonne option non magnétique.

- Services d'assemblage : Découvrez notre assemblage clé en main pour les projets complexes et à forte mixité.

Glossaire du wirebonding pour interface de qubit (termes clés)

| Terme | Définition |

|---|---|

| Wedge Bonding | Une technique de liaison utilisant l'énergie ultrasonique et la pression pour fixer le fil ; préférée pour les pas fins et le fil d'aluminium. |

| Ball Bonding | Une technique formant une bille à l'extrémité du fil ; généralement plus rapide mais nécessite de la chaleur (thermosonique) et utilise typiquement de l'or. |

| Supraconductivité | Un état où un matériau (comme l'aluminium à <1,2 K) a une résistance électrique nulle. |

| Qubit (Bit Quantique) | L'unité de base de l'information quantique ; très sensible au bruit et à la chaleur. |

| Inductance (Parasite) | Inductance indésirable ajoutée par la boucle de fil, affectant la fréquence et la qualité du signal. |

| Cryogénique | Relatif à des températures extrêmement basses (généralement inférieures à 100K, jusqu'à la plage des mK). |

| CTE (Coefficient de Dilatation Thermique) | Le taux auquel un matériau se dilate/se contracte avec les changements de température. Un désaccord provoque une défaillance de la liaison. |

| ENEPIG | Nickel Chimique Palladium Chimique Or par Immersion ; une finition de surface universelle bonne pour le fil de liaison. |

| Effet de Peau | La tendance du courant haute fréquence à circuler près de la surface du conducteur ; pertinent pour les lignes de contrôle micro-ondes. |

| Jonction Josephson | Un composant clé des qubits supraconducteurs ; extrêmement sensible aux décharges électrostatiques et à la chaleur. |

| Interposeur | Une couche intermédiaire (silicium ou céramique) utilisée pour acheminer les signaux entre la puce et la carte PCB principale. |

| Fissure au Talon | Une fracture au point où le fil passe du plot de liaison à la boucle ; un mode de défaillance courant. |

Conclusion finale : le fil de liaison pour l'interface de qubit – prochaines étapes

Maîtriser le fil de liaison pour l'interface de qubit consiste à gérer l'intersection de la robustesse mécanique, de la physique cryogénique et de l'ingénierie des micro-ondes. Cela nécessite de s'éloigner des mentalités standard de "continuité seule" et d'adopter une approche rigoureuse de la pureté des matériaux, de la géométrie des boucles et de la finition de surface. Si vous êtes prêt à passer de la conception à la fabrication de votre processeur quantique ou de votre électronique de contrôle, assurez-vous que votre partenaire de fabrication comprend ces contraintes uniques.

Lorsque vous demandez un devis à APTPCB, veuillez fournir :

- Fichiers Gerber : Avec des indications claires des emplacements des plots de liaison (bond pads).

- Détails de l'empilement (Stackup) : Y compris les matériaux diélectriques spécifiques (par exemple, Rogers, Céramique).

- Spécifications de la finition de surface : Indiquez explicitement "Non-magnétique" si nécessaire.

- Diagramme de liaison filaire (Wirebond) : Spécifiant les hauteurs de boucle cibles et le matériau du fil (Al vs. Au).

- Température de fonctionnement : (par exemple, 4K, 10mK) afin que nous puissions vous conseiller sur les risques liés au CTE.

Un matériel quantique fiable commence par une interface fiable. Contactez-nous dès aujourd'hui pour examiner la fabricabilité de votre conception.