Advanced Engineering Guide

La realite d'ingenierie de la fabrication de PCB a grand nombre de couches

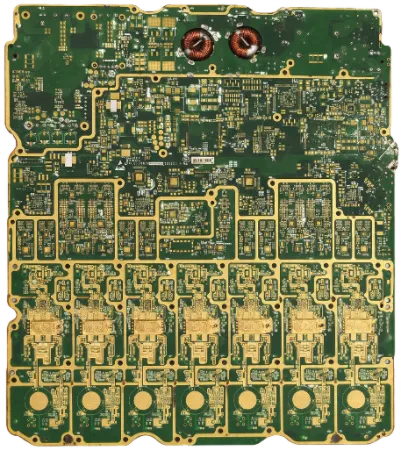

Concevoir un backplane 32 couches ou une motherboard d'AI 24 couches dans un logiciel ECAD est un puzzle de routage complexe, mais sa fabrication est une bataille contre la physique, la chimie et la thermodynamique. A mesure que le nombre de couches augmente, la marge d'erreur se reduit de facon exponentielle. Chez APTPCB, nous collaborons avec des hardware engineers seniors du monde entier pour faire passer ces conceptions extremes du domaine numerique a la realite physique. Voici une analyse approfondie des obstacles d'ingenierie propres a la fabrication a grand nombre de couches et de la facon dont nous les resolvons.

1. La tyrannie du registration et de la mise a l'echelle dimensionnelle

La plus grande menace pour une carte a grand nombre de couches est l'echec du registration. Une PCB est construite en pressant des couches alternees de cores completement cures et de prepreg non cures sous une chaleur extreme et une pression hydraulique. Pendant ce processus de laminage, les materiaux se dilatent puis, lorsque la resine durcit et refroidit, ils se retractent. Cette mise a l'echelle dimensionnelle est anisotrope : elle se retracte differemment dans les directions X et Y du tissage de fibre de verre.

Sur une carte 4 couches, un leger decalage peut etre absorbe facilement par l'annular ring, c'est-a-dire le pad en cuivre entourant un trou perce. Sur une carte 40 couches, si les couches internes se decalent de facon incoherente, un foret mecanique descendant a travers la carte sortira inevitablement du pad de cuivre a la couche 25, coupant la connexion ou provoquant un court-circuit fatal vers un plan de masse voisin.

La solution APTPCB : nos ingenieurs CAM appliquent des facteurs de mise a l'echelle non lineaires a l'artwork de chaque couche et predisent mathematiquement le taux de retrait selon la densite de cuivre propre a cette couche. Pendant le layup, nous utilisons des systemes de X-Ray induction bonding pour aligner physiquement les couches internes entre elles avant le cycle de pressage, garantissant une precision de registration couche a couche de ±1.5 mil.

2. Placage a fort rapport d'aspect : le defi capillaire

A mesure que le nombre de couches augmente, la carte devient plus epaisse. Une carte 32 couches peut facilement atteindre 5.0 mm (200 mil) d'epaisseur. Si vous devez percer un via de 10 mil (0.25 mm) a travers cette carte, vous creez un tube capillaire microscopique avec un rapport d'aspect de 20:1.

Les systemes standard d'electroplacage en courant continu s'appuient sur la dynamique des fluides pour faire circuler des bains chimiques riches en cuivre dans les trous. Dans un via 20:1, le fluide au centre du barrel stagne. Les ions cuivre s'epuisent et le processus de placage s'arrete, ce qui donne un via avec du cuivre epais en surface mais dangereusement fin, voire absent, au milieu. Sous la chaleur extreme du SMT reflow ou du wave soldering, l'expansion sur l'axe Z de la carte dechire facilement ce barrel mince et provoque des circuits ouverts intermittents notoirement difficiles a diagnostiquer.

La solution APTPCB : pour les cartes depassant un rapport d'aspect de 10:1, nous deployons le Periodic Reverse Pulse Plating. Au lieu d'un courant continu constant, le systeme pulse rapidement le courant vers l'avant puis l'inverse brievement. L'impulsion inverse agit comme une "pompe" electrique, retirant les produits chimiques epuises et attirant un fluide frais riche en cuivre jusque dans le centre du via. Cela garantit une paroi de barrel uniforme et epaisse, capable de resister a plusieurs cycles de reflow sans plomb.

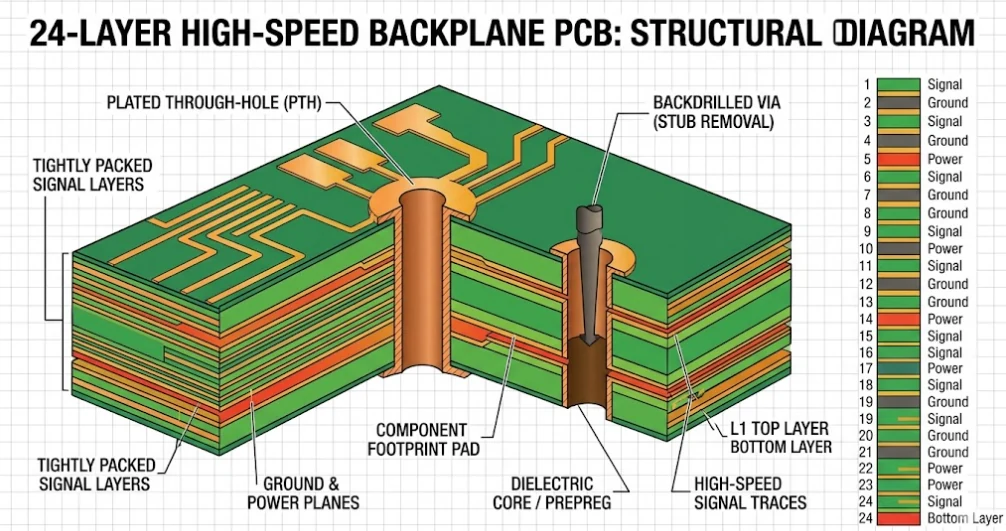

3. Eliminer la resonance de signal grace a un backdrilling de precision

Dans les architectures numeriques haut debit, comme PCIe Gen5, 100G/400G Ethernet et 112G PAM4, la geometrie physique du via devient un composant RF actif. Imaginez un signal voyageant de la Layer 1 a la Layer 5 sur un backplane 24 couches. Le signal sort correctement a la Layer 5, mais le barrel de cuivre restant, qui continue de la Layer 6 jusqu'a la Layer 24, agit comme une antenne non terminee, c'est-a-dire un "via stub". Ce stub reflechit de l'energie electromagnetique dans le canal, cree une interference destructrice et ferme le diagramme de l'oeil.

La solution APTPCB : pour restaurer l'integrite du signal, nous utilisons le Controlled-Depth Backdrilling. A l'aide de machines de perçage CNC avancees equipees d'une technologie de detection conductrice de surface, le foret entre par le dessous de la carte (Layer 24) et retire le stub de cuivre non desire, en s'arretant avec precision avant d'atteindre la couche active de signal (Layer 5). Nous obtenons regulierement des precisions de profondeur de ±50μm, en laissant un stub residuel inoffensif inferieur a 8-10 mil, ce qui nettoie le canal de ses resonances destructrices.

4. Gestion de l'impedance dans les architectures epaisses

Sur une carte 6 couches, une trace single-ended de 50Ω peut necessiter une largeur de 6 mil. Sur une carte 32 couches, comme il faut utiliser des prepregs ultra-fins, par exemple de 2 mil, pour garder l'epaisseur totale maitrisable, la distance entre la trace de signal et son plan de reference se reduit drastiquement. Pour conserver ces memes 50Ω, la largeur de la trace doit diminuer proportionnellement, souvent jusqu'a 2.5 ou 3 mil.

Graver une trace de 3 mil avec une tolerance d'impedance de ±5% demande une maitrise chimique absolue. La solution APTPCB : nous utilisons le Laser Direct Imaging (LDI) pour obtenir une precision d'exposition sub-mil, associee a des lignes de gravure assistees par vide qui extraient l'acide entre les traces serrées afin d'eviter l'undercut. Nous modelisons chaque structure d'impedance dans Polar Si9000 et verifions physiquement le resultat via des coupons TDR sur chaque panneau de production.