Sommaire

- Highlights

- Reduire le cout PCB sans sacrifier le yield : definition et perimetre

- Reduire le cout PCB sans sacrifier le yield : regles et specifications

- Reduire le cout PCB sans sacrifier le yield : etapes d'application

- Reduire le cout PCB sans sacrifier le yield : troubleshooting

- 6 regles essentielles pour reduire le cout sans perdre en yield

- FAQ

- Demander un devis / une revue DFM pour reduire le cout sans sacrifier le yield

- Conclusion

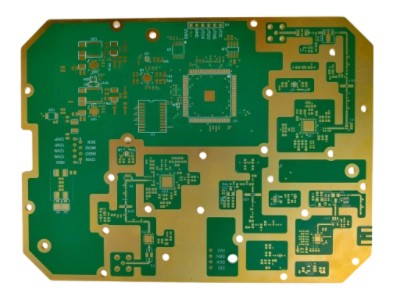

Reduire le cout d'un PCB ne consiste pas a degrader la qualite, mais a supprimer les exigences qui augmentent le prix sans ameliorer reellement la fiabilite ou les performances. Comprendre comment reduire le cout PCB sans sacrifier le yield demande de combiner DFM, choix des matieres et realites de fabrication.

Quick Answer

Pour reduire le cout PCB sans sacrifier le yield, il faut garder le plus possible le design dans les capacites standard.

- Standardiser les materiaux : FR4 TG150 a TG170 sauf besoin RF ou haute vitesse.

- Optimiser la panelisation : viser plus de 80 % d'utilisation matiere.

- Reduire le nombre de forets : moins de changements outil = moins de temps CNC.

- Assouplir les tolerances : adopter +/- 0,10 mm si +/- 0,05 mm n'est pas indispensable.

- Eviter le HDI : blind et buried vias augmentent fortement le cout.

- Verifier en DFM : reperer les cost drivers avant devis.

Highlights

- Utilisation panneau : l'une des plus grosses sources de cout cache.

- Nombre de couches : moins de couches n'aide pas si cela impose du HDI.

- Finition de surface : ENIG est fiable mais cher ; OSP ou HASL sont souvent plus economiques.

- Gestion des vias : un aspect ratio raisonnable protege le yield.

Reduire le cout PCB sans sacrifier le yield : definition et perimetre

Le prix d'un PCB vient de trois composantes : cout matiere, cout process et pertes de yield. Une carte plus petite n'est pas automatiquement moins chere si elle oblige a passer en 3 mil, en microvias laser ou en tolerances excessives.

La vraie reduction de cout apparait quand le design reste dans la zone de process la plus stable. Une FR4 PCB standard avec 5 mil de piste et d'espacement reste bien moins couteuse qu'une version a 3 mil, parce que le rendement de gravure est beaucoup plus eleve. Un stackup pair reste egalement preferable, car les nombres de couches impairs accroissent le risque de warpage.

Levier technique → impact pratique

| Levier / specification | Impact pratique (yield/cout/fiabilite) |

|---|---|

| Utilisation panneau | Impact eleve. Une mauvaise utilisation signifie de la matiere payee mais jetee. |

| Technologie de via | Driver de cout critique. Blind et buried vias imposent des cycles de lamination supplementaires. |

| Trace / Space | Driver yield. Sous 3,5 mil, gravure et inspection deviennent nettement plus critiques. |

| Surface Finish | Cout vs. assembly. HASL est economique, ENIG est plan mais plus cher. |

| Nombre et taille des trous | Temps machine. Beaucoup de trous ou des forets tres petits augmentent le temps CNC. |

Reduire le cout PCB sans sacrifier le yield : regles et specifications

| Regle | Valeur recommandee | Pourquoi c'est important | Comment verifier |

|---|---|---|---|

| Min Trace / Space | ≥ 5 mil / 5 mil | Sous 4 mil, le process de gravure devient plus sensible. | Lancer le DRC dans le CAD. |

| Min Mechanical Drill | ≥ 0,25 mm | Les forets plus petits cassent plus facilement. | Verifier la table de perçage. |

| Annular Ring | ≥ 5 mil | Evite le breakout en cas de leger decalage. | Comparer pad et trou. |

| Layer Count | Nombre pair | Les stacks impairs sont plus sujets au warpage. | Revoir le PCB Stackup. |

| Board Thickness | 1,6 mm | Les epaisseurs speciales coutent plus cher. | Verifier les proprietes carte. |

| Copper Weight | 1 oz | Le cuivre epais demande plus de temps de gravure. | N'augmenter qu'en cas de besoin reel. |

Reduire le cout PCB sans sacrifier le yield : etapes d'application

Processus d'implementation

Approche pas a pas

Partir du stackup le plus simple compatible avec les besoins electriques.

Placer les composants pour reduire pistes, croisements et vias.

Ajuster dimensions et array pour maximiser le nombre d'unites par panneau.

Supprimer les process speciaux non indispensables.

Reduire le cout PCB sans sacrifier le yield : troubleshooting

1. Warpage et bowing

Probleme : stackup asymetrique ou suppression des copper pours.

Fix : conserver un stackup symetrique et equilibrer la densite cuivre.

2. Mauvais alignement de solder mask

Probleme : mask dams trop fines sur une carte de cout standard.

Fix : utiliser un gang relief ou augmenter l'espacement entre pads si possible.

3. Mauvaise metallisation des vias

Probleme : petits vias sur carte epaisse, avec aspect ratio trop eleve.

Fix : rester sous 8:1 pour le cout standard.

Voir aussi nos DFM Guidelines.

6 regles essentielles pour reduire le cout sans perdre en yield

| Regle / recommandation | Pourquoi c'est important | Valeur cible / action |

|---|---|---|

| Standardiser le laminate | Le standard est moins cher et mieux disponible. | FR4 TG150 |

| Maximiser l'usage panneau | Faible rendement = rebut payant. | >80 % |

| Consolider les drills | Chaque outil ajoute du temps CNC. | <10 tailles |

| Eviter blind/buried vias | Les cycles supplementaires coutent cher. | Through-hole only |

| Assouplir les tolerances | Des tolerances trop strictes ralentissent l'usinage. | +/- 0,10 mm |

| Choisir la finition adaptee | L'or est cher si la planeite extreme n'est pas indispensable. | HASL ou OSP |

FAQ

Q: Reduire les couches fait-il toujours baisser le cout ?

A: Pas si cela oblige a passer en HDI ou en routage tres fin.

Q: OSP est-il moins cher que ENIG ?

A: Oui, mais avec une tenue au stockage et au handling plus limitee.

Q: Comment la quantite agit-elle sur le prix unitaire ?

A: En Mass Production, les setup costs sont amortis sur beaucoup de cartes.

Q: Une forme non rectangulaire permet-elle d'economiser ?

A: En general non, car elle panelise moins bien.

Demander un devis / une revue DFM pour reduire le cout sans sacrifier le yield

Envoyez :

- Gerber Files : format RS-274X de preference.

- Drill File : Excellon avec liste d'outils.

- Schema de stackup : ordre des couches et poids de cuivre.

- Fabrication Drawing : couleur, finition et tolerances.

- Quantites : prototype ou production.

Conclusion

Reduire le cout PCB sans sacrifier le yield signifie concevoir intelligemment pour les process standard, mieux utiliser la matiere et retirer la complexite inutile. Avec des regles claires sur trace width, drill size et stackup, il est possible d'obtenir un produit fiable a cout competitif.