Sommaire

- Points cles

- PCB Lead Time Checklist for Npi : definition et perimetre

- PCB Lead Time Checklist for Npi regles et specifications

- PCB Lead Time Checklist for Npi etapes de mise en oeuvre

- PCB Lead Time Checklist for Npi depannage

- 6 regles essentielles pour PCB Lead Time Checklist for Npi (memo)

- FAQ

- Demander un devis / une revue DFM pour PCB Lead Time Checklist for Npi

- Conclusion

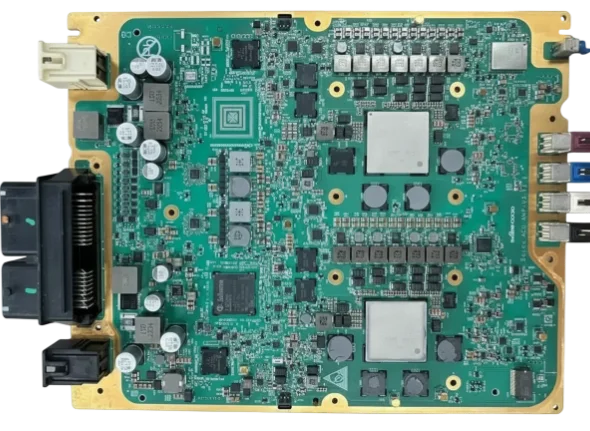

Dans le monde de la fabrication electronique, la phase de New Product Introduction (NPI) est une course contre la montre dans laquelle la precision sert de carburant. Une PCB Lead Time Checklist for Npi solide ne consiste pas seulement a compter les jours de fabrication, mais a identifier et eliminer les retards "caches" qui apparaissent avant meme que le cuivre ne soit grave. En tant que Senior CAM Engineers chez APTPCB, nous voyons chaque annee des milliers de conceptions NPI. La difference entre un turnaround de 3 jours et un retard de 3 semaines se joue souvent sur la clarte des donnees, la disponibilite des materiaux et la conformite DFM (Design for Manufacturing).

L'horloge ne demarre pas lorsque vous chargez vos Gerbers ; elle demarre quand les Engineering Questions (EQ) sont resolues et que l'atelier recoit le "feu vert". Ce guide presente exactement la checklist que nous utilisons pour valider les commandes NPI entrantes du point de vue de la vitesse et de la fiabilite.

Quick Answer

Pour optimiser votre PCB Lead Time Checklist for Npi, concentrez-vous immediatement sur ces trois piliers critiques :

- Regle / plage : restez sur des materiaux standards comme FR4 TG150/170 et des stackups standards. Les laminates speciaux ou des epaisseurs dielectriques atypiques peuvent ajouter 2 a 3 semaines au lead time.

- Piege courant : les drill charts ambigus ou des exigences d'impedance non definies. Si le CAM engineer doit deviner, votre carte passe en "On Hold".

- Methode de verification : lancez un controle DFM et un BOM availability scrub avant de liberer les fichiers. Assurez-vous que votre fichier "Read Me" precise clairement la classe IPC (2 ou 3) et les preferences de stackup.

Points cles

- Etat du stock matiere : 30 % des retards NPI proviennent de la specification de laminates hors stock. Verifiez toujours les listes de stock en premier.

- Reduction des EQ : un fichier "Read Me" clair et une netlist peuvent reduire les cycles d'Engineering Questions (EQ) de 3 jours a 3 heures.

- Impact technologique : passer d'un through-hole standard au HDI (High Density Interconnect) ajoute au minimum 2 a 3 jours par cycle de laminage.

- Preparation a l'assembly : pour un NPI turnkey, les lead times composants depassent souvent le temps de fabrication du PCB ; validez la BOM tres tot.

- Validation : valider le stackup en amont avec le fabricant garantit le controle d'impedance sans redesign iteratif.

PCB Lead Time Checklist for Npi : definition et perimetre

Quand nous parlons d'une PCB Lead Time Checklist for Npi, nous regardons le calendrier complet necessaire pour passer d'un fichier CAO a un prototype physique assemble. En phase NPI, les volumes sont faibles, mais la complexite et l'urgence sont elevees. Le perimetre de cette checklist couvre trois phases distinctes : Pre-CAM (verification des donnees), Fabrication (physique et chimie) et Assembly (logistique composants).

Le "Lead Time" est souvent mal compris. Il ne s'agit pas seulement du temps machine. Il inclut aussi :

- Phase EQ : les allers-retours de questions concernant des donnees manquantes ou des violations DFM.

- Preparation matiere : decoupe et etuvage des laminates, standards ou exotiques.

- Cycles de process : laminage, perçage, metallisation, gravure et finition de surface.

- Tests : test electrique (E-Test) et AOI (Automated Optical Inspection).

Reduire le lead time suppose de prendre des decisions qui simplifient ces etapes sans compromettre l'integrite du signal. Par exemple, l'utilisation de services NPI small batch PCB manufacturing permet souvent d'acceder a des voies "fast-track", a condition que vos donnees soient propres.

Levier technique / decision → Impact pratique

| Levier de decision / specification | Impact pratique (yield/cout/fiabilite) |

|---|---|

| Choix du materiau de base | FR4 standard (stock) = lancement en 24 h. Materiau exotique type Rogers/Teflon = 1 a 3 semaines de lead time si hors stock. |

| Technologie de vias (HDI vs. traversant) | Les blind/buried vias exigent un laminage sequentiel. Chaque cycle ajoute environ 2 a 3 jours au lead time NPI. |

| Finition de surface | ENIG/HASL sont standards et rapides. Hard Gold ou ENEPIG demandent des lignes de metallisation plus complexes et ajoutent 1 a 2 jours. |

| Tolerance d'impedance | Le standard ±10 % est rapide. Un ±5 % serre demande coupon testing et parfois re-spin, donc plus de risque de retard. |

PCB Lead Time Checklist for Npi regles et specifications

Pour que votre NPI traverse l'usine sans s'arreter pour des "Engineering Holds", respectez ces specifications. Il ne s'agit pas de limites theoriques, mais des zones de securite pratiques pour une fabrication quick-turn.

| Regle | Valeur recommandee | Pourquoi c'est important | Comment verifier |

|---|---|---|---|

| Largeur / espacement des pistes | ≥ 4 mil / 4 mil (0,1 mm) | Descendre sous 3,5 mil impose une gravure et une AOI specialisees, ce qui augmente le risque d'opens/shorts et le temps d'inspection. | Lancer un DRC dans la CAO avec une contrainte de 4 mil. |

| Rapport d'aspect du perçage | ≤ 8:1 (par ex. trou de 0,2 mm dans une carte de 1,6 mm) | Les rapports d'aspect eleves sont difficiles a metalliser de facon fiable. Au-dela de 10:1, il faut des cycles de metallisation specialises et plus lents. | Verifier l'epaisseur de carte par rapport au plus petit diametre de perçage. |

| Anneau annulaire | ≥ 4 mil (0,1 mm) au-dela du perçage | Permet d'absorber la derive mecanique de perçage sans casser la connexion. | Verifier que la taille du pad = diametre du trou + 8 mil (0,2 mm). |

| Solder Mask Dam | ≥ 3 mil (0,075 mm) | Evite les ponts de soudure pendant l'assembly. Des dams plus petits risquent de se decoller ou d'exiger du LDI (Laser Direct Imaging). | Verifier l'espace entre les ouvertures de masque dans le Gerber viewer. |

| Finition de surface | ENIG (Electroless Nickel Immersion Gold) | Meilleur compromis entre planete pour les SMD et duree de stockage. Le HASL peut etre irregulier pour les BGA a pas fin. | Le preciser clairement dans les notes de fabrication. |

| Definition du stackup | "Use Vendor Standard" (si possible) | Autoriser le fabricant a utiliser ses combinaisons prepreg/core en stock evite des delais de commande matiere. | Noter "Impedance controlled, vendor to adjust stackup" dans les Fab Notes. |

Respecter ces regles est particulierement crucial lorsque vous traitez des technologies complexes comme le HDI PCB, ou la marge d'erreur est nettement plus faible.

PCB Lead Time Checklist for Npi etapes de mise en oeuvre

Mettre en place une PCB Lead Time Checklist for Npi solide exige un changement de process, pas seulement un document. Suivez ce guide d'execution pour aligner votre equipe design avec le flux de fabrication.

Processus de mise en oeuvre

Guide d'execution etape par etape

Avant de router les pistes, contactez votre fabricant, par exemple APTPCB, pour confirmer le stackup. Demandez un "Stackup Report" base sur des matieres en stock. Cela verrouille vos calculs d'impedance et garantit la disponibilite immediate des cœurs et prepregs.

Pour [Turnkey Assembly](/pcba/turnkey-assembly), le PCB est rarement l'element au plus long lead time : ce sont les puces. Faites un BOM scrub afin d'identifier les composants obsoletes ou hors stock. Definissez des alternatives pour les passifs dans la BOM afin d'eviter les blocages assembly.

Lancez une revue DFM centree sur les "showstoppers" : distance drill-to-copper, slivers et acid traps. Verifiez aussi que les footprints correspondent aux composants reels (DFA) pour eviter les problemes de placement. Consultez les [DFM Guidelines](/resources/dfm-guidelines) pour les regles d'espacement precises.

Soumettez un package complet : Gerbers (RS-274X), Drill file (Excellon), IPC Netlist, fichier Pick & Place, BOM et PDF "Read Me" explicite. L'ambiguite est l'ennemie de la vitesse. Precisez clairement : "No X-outs allowed" ou "X-outs accepted" pour la panelisation.

PCB Lead Time Checklist for Npi depannage

Meme avec une checklist, des problemes surviennent. Voici comment depanner les retards NPI les plus courants :

1. "On Hold for Eq" (Engineering Questions)

- Symptome : vous recevez un e-mail demandant des clarifications sur les tailles de perçage ou les lignes d'impedance.

- Cause racine : informations contradictoires, par exemple un drill file a 0,2 mm alors que le Gerber mesure 0,15 mm, ou couches de reference manquantes.

- Correctif : considerez toujours le Gerber comme la source maitre. Ajoutez la note : "In case of conflict, Gerber data takes precedence." Utilisez notre Impedance Calculator pour verifier avant soumission que les largeurs de piste correspondent bien a l'impedance cible.

2. Penuries de materiaux

- Symptome : l'usine vous informe que le materiau Rogers ou Panasonic specifie a un lead time de 3 semaines.

- Cause racine : specification d'un laminate de niche pour une carte d'usage general.

- Correctif : sauf si vous concevez des cartes RF haute frequence, par exemple du radar 77 GHz, autorisez des materiaux "Equivalent". Ecrivez : "Material: Isola 370HR or equivalent TG170 material."

3. Problemes de soudabilite a l'assembly

- Symptome : les pads ne mouillent pas correctement, ou des voids apparaissent sous les BGA.

- Cause racine : finition expiree ou oxydation liee a un mauvais stockage/manutention entre la Fab et l'Assembly.

- Correctif : s'il existe un delai entre Fab et Assembly, assurez-vous que les cartes soient mises sous vide avec dessiccant. Pour le NPI, l'ENIG est prefere a l'OSP, car l'OSP a une duree de vie plus courte et supporte mal la manipulation.

6 regles essentielles pour PCB Lead Time Checklist for Npi (memo)

| Regle / consigne | Pourquoi c'est important (physique/cout) | Valeur cible / action |

|---|---|---|

| Standardiser les materiaux | Les laminates sur mesure exigent une commande fournisseur et ajoutent des jours/semaines. Les materiaux stockes sont immediats. | FR4 TG150/170 (stock) |

| Drill-to-Copper Clearance | Des marges trop faibles font risquer de percer dans les pistes et donc des courts-circuits. Les assouplir ameliore le yield et la vitesse. | ≥ 8 mil (0,2 mm) |

| Definir clairement l'impedance | L'ambiguite oblige le CAM a calculer puis a demander validation. Un stackup predefini evite cette etape. | Inclure une table de stackup dans le Fab Drawing |

| Eviter le Via-in-Pad (si possible) | Le VIPPO impose des etapes supplementaires de metallisation et de planarisation (POFV), ajoutant 1 a 2 jours. | Dog-bone fanout pour BGA > 0,5 mm de pas |

| Strategie de panelisation | Des arrays inefficaces gaspillent matiere et temps d'assembly. Laissez la fab optimiser ou suivez les specs assembly. | Laisser la fab paneliser (donner la taille max) |

| BOM complete | L'absence de MPNs (Manufacturer Part Numbers) bloque instantanement l'approvisionnement assembly. | 100 % de MPNs correspondants (pas de descriptions generiques) |

FAQ

Q : Combien de temps la technologie HDI ajoute-t-elle au lead time NPI ?

A : Le HDI (High Density Interconnect) ajoute generalement 2 a 4 jours au lead time standard. Cela vient des cycles de laminage sequentiel necessaires pour les blind et buried vias. Un stackup 1+N+1 est plus rapide qu'un 2+N+2.

Q : Puis-je expedier des commandes NPI en 24 heures ?

A : Oui, pour des rigid PCBs standards de 2 a 6 couches avec materiaux standards, un turn 24 heures est possible. Cela demande toutefois des donnees "parfaites" sans aucun retard EQ. Les cartes complexes ou celles qui necessitent un assembly prendront plus de temps.

Q : Quelle est la cause la plus courante des retards NPI ?

A : L'ambiguite des donnees. Des informations contradictoires entre le drill file, les couches Gerber et les notes de fabrication obligent le CAM engineer a suspendre le process et a demander une clarification (EQ).

Q : Dois-je utiliser des pieces consignees ou le turnkey pour le NPI ?

A : Pour la vitesse, le Turnkey est generalement plus rapide, car le fabricant exploite ses chaines d'approvisionnement et stocks existants. Les pieces consignees, c'est-a-dire vos propres composants envoyes, peuvent causer des retards si les kits sont incomplets ou bloques en douane.

Demander un devis / une revue DFM pour PCB Lead Time Checklist for Npi

Pret a lancer votre NPI ? Envoyez vos donnees a APTPCB pour une revue DFM complete et une estimation de lead time precise.

Checklist pour devis / DFM :

- Gerber Files : format RS-274X (toutes les couches).

- Drill File : format Excellon (ASCII).

- Fab Drawing : PDF avec stackup, materiau et specs de finition.

- BOM : format Excel avec Manufacturer Part Numbers (pour assembly).

- Pick & Place : coordonnees XY (pour assembly).

- Quantites : nombre de prototypes, par exemple 5, 10, 50, et volume annuel estime.

Conclusion

Maitriser la PCB Lead Time Checklist for Npi, c'est garder sous controle les variables sur lesquelles vous pouvez agir. En standardisant les materiaux, en validant les stackups en amont et en assurant une clarte totale des donnees, vous transformez le processus NPI d'un goulot d'etranglement en avantage concurrentiel. La vitesse en NPI ne consiste pas seulement a aller vite, mais a faire juste du premier coup.

Cordialement, L'equipe d'ingenierie APTPCB