Les cartes principales de Smart TV rassemblent le traitement applicatif, la mise a l'echelle et le traitement video, plusieurs interfaces haut debit comme HDMI, USB et Ethernet, la connectivite sans fil et les systemes audio sur des cartes qui doivent tenir des objectifs de cout tres agressifs tout en offrant une experience de visionnage premium. Les difficultes de conception PCB vont des interfaces HDMI 2.1 tres haut debit, avec 48 Gbit/s agreges, jusqu'aux interfaces de pilotage des grands panneaux et a l'integration de l'alimentation.

Ce guide traite des points specifiquement lies au PCB dans une Smart TV : la repartition entre carte principale et T-CON, les exigences de routage du SoC video, l'integrite du signal HDMI 2.1, la conception de l'interface panneau, l'architecture de l'alimentation et l'equilibre entre qualite et optimisation des couts de fabrication, essentiel sur les produits televiseurs.

Design Checklist (Fast Pass)

- Partitionner tot : definir carte principale vs T-CON vs carte d'alimentation, puis figer rapidement l'interconnexion et le choix des connecteurs.

- Placer HDMI au plus pres : garder les liaisons HDMI 2.1 FRL courtes ; prevoir d'emblee les empreintes ESD, CMC et retimer.

- Traiter la DDR comme un systeme : stackup, impedance, appairage de longueurs, plans de reference et chemins de retour doivent etre penses ensemble.

- Concevoir PDN et thermique ensemble : cuivre, reseaux de vias et diffusion thermique vers le chassis font partie du vrai design de puissance.

- Faire du DFM pour le cout : eviter le HDI la ou il n'apporte rien ; optimiser l'utilisation de panneau et l'acces au test.

In This Guide

- Architecture des cartes TV : repartition entre carte principale et T-CON

- Exigences de routage du SoC de traitement video

- Mise en oeuvre de l'interface haute vitesse HDMI 2.1

- Conception de l'interface de timing du panneau

- Integration de l'alimentation et considerations thermiques

- Fabrication optimisee en cout pour les produits televiseurs

TV Board Architecture: Main Board and T-CON Partitioning

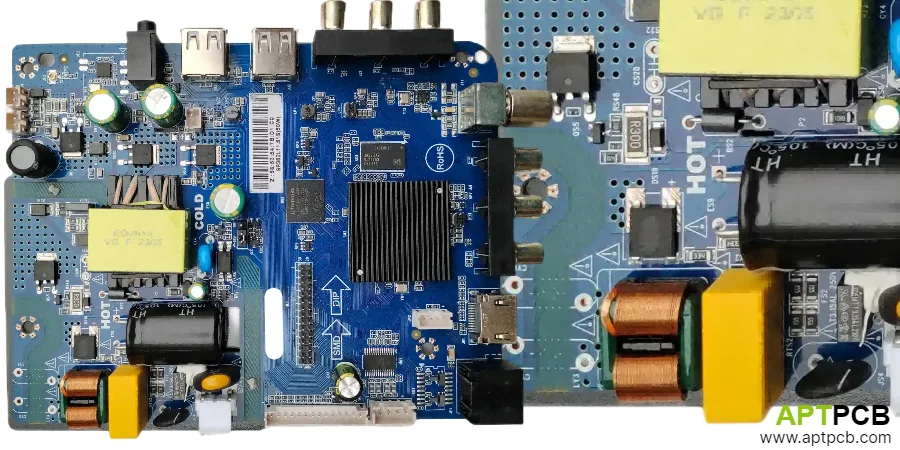

L'electronique d'une Smart TV est generalement repartie sur plusieurs PCB : la carte principale prend en charge le traitement applicatif, la connectivite, ainsi que l'entree et le traitement video ; la carte T-CON, timing controller, pilote le panneau et optimise l'image ; et la carte d'alimentation fournit plusieurs rails de tension. Cette partition repond a la fois a des besoins fonctionnels et a des contraintes de chaine d'approvisionnement, car differents panneaux utilisent differents T-CON, tandis que les cartes principales sont souvent mutualisees entre plusieurs references.

L'interface entre la carte principale et la T-CON transporte un flux video deja entierement traite, jusqu'a des resolutions 8K. Cela impose soit des interfaces paralleles a tres grande bande passante, LVDS necessitant alors des dizaines de paires, soit des protocoles series comme V-by-One ou eDP, qui reduisent le nombre de conducteurs mais exigent une integrite du signal multi-gigabit. Cette interface entre cartes fixe souvent le plafond de performance video du systeme.

Board Partitioning Considerations

- Perimetre de la carte principale : SoC, memoire, recepteurs HDMI, interfaces USB et Ethernet, modules WiFi et Bluetooth, traitement audio et liaisons vers la T-CON et les cartes d'alimentation.

- Niveau d'integration T-CON : Certains panneaux integrent le T-CON dans le panneau lui-meme, d'autres utilisent une carte T-CON separee ; cela modifie directement les exigences d'interface cote carte principale.

- Choix de l'interface : Les specifications du panneau guident la decision. Beaucoup de conceptions 4K60 utilisent V-by-One HS avec environ 8 voies dans la classe de 3 a 4 Gbit/s par voie ; la 8K demande en general plus de voies, des debits plus eleves ou une autre interface.

- Types de connecteurs : Les liaisons haute vitesse s'appuient sur des connecteurs specialises qui preservent l'adaptation d'impedance ; les nappes limitent la bande passante et imposent une conception minutieuse.

- Distribution de puissance : La carte principale peut alimenter la T-CON, ce qui augmente les contraintes de courant sur la carte principale, ou bien la T-CON peut etre alimentee directement par la carte d'alimentation.

- Disposition mecanique : La carte principale se place en general en bas a l'arriere de l'ecran ; les contraintes thermiques imposent un certain degagement vis-a-vis du panneau et des chemins de ventilation suffisants.

Comprendre cette architecture systeme permet de prendre les bonnes decisions de partition PCB, avec un impact direct sur les performances electriques comme sur l'efficacite de fabrication.

Video Processing SoC Routing Requirements

Les SoC de Smart TV integrent une complexite considerable : processeurs applicatifs quad-core ou octa-core, decodeurs video dedies prenant en charge plusieurs codecs en 4K ou 8K, moteurs d'affichage assurant mise a l'echelle et amelioration d'image, et de nombreuses interfaces. Ces composants fortement integres se presentent sous de gros boitiers BGA, souvent de 500 a plus de 1000 broches, avec un pas fin de 0,4 a 0,65 mm. Le routage doit donc concilier performance et fabricabilite.

Les interfaces memoire sont particulierement critiques. La DDR4 ou la LPDDR4/5 fonctionne a des vitesses qui imposent un appairage de longueurs strict et une impedance controlee. Contrairement aux smartphones, ou la memoire est souvent empilee en package-on-package, les SoC TV utilisent en general une memoire discrete, ce qui reporte toutes les contraintes d'integrite du signal au niveau de la carte.

SoC Routing Guidelines

- Strategie de fanout BGA : Les BGA a pas fin exigent du via-in-pad ou du fanout en dog-bone ; les vias traversants limitent les canaux de routage, donc les blind vias peuvent devenir utiles sur les boitiers denses.

- Routage memoire : Une DDR4 a 2666 a 3200 MT/s demande un appairage de longueurs a l'interieur de chaque byte lane a ±5 mm, un appairage DQS a DQ a ±10 mm et une impedance reguliere.

- Exigences sur les plans de reference : Les signaux memoire et haut debit ont besoin de plans de reference continus ; il faut eviter de faire passer des pistes d'alimentation ou des vias dans les zones de plan sous les signaux critiques.

- Strategie de decouplage : Les broches d'alimentation du SoC exigent un decouplage local, par exemple 100 nF sur chaque groupe de broches, plus des capacites de reserve de 10 a 100 uF a proximite. Les condensateurs doivent etre places aussi pres que le routage le permet.

- Acces JTAG et debug : Les interfaces de debug comme JTAG ou UART doivent rester accessibles pour le developpement et le test de production ; il faut positionner correctement points de test ou connecteurs.

- Conception thermique : La dissipation du SoC, typiquement 5 a 15 W, necessite des vias thermiques sous le boitier et une diffusion de chaleur suffisante vers les points de fixation du dissipateur ou du chassis.

Le routage du SoC video beneficie de techniques de PCB haute vitesse afin de garantir des marges suffisantes sur les interfaces memoire et affichage.

HDMI 2.1 High-Speed Interface Implementation

Le HDMI 2.1 fait partie des interfaces grand public les plus exigeantes. Avec 12 Gbit/s par voie sur quatre voies de donnees, soit 48 Gbit/s agreges, il prend en charge la 8K a 60 Hz ou la 4K a 120 Hz avec HDR. Le routage entre le recepteur HDMI et le connecteur doit maintenir l'integrite du signal a des frequences ou la longueur d'onde devient du meme ordre que celle des pistes. Une discipline stricte de ligne de transmission est donc indispensable.

Les anciennes versions HDMI 1.4 et 2.0, jusqu'a 18 Gbit/s agreges, reposaient sur une signalisation differentielle avec terminaison source et une tolerance d'impedance relativement moderee. HDMI 2.1 FRL, Fixed Rate Link, eleve nettement le niveau d'exigence : 100 ohms d'impedance differentielle (±10%), appairage serre des longueurs au sein de chaque paire et maitrise des pertes d'insertion et de retour sur l'ensemble du canal, c'est-a-dire connecteur, PCB et cable.

HDMI 2.1 Routing Requirements

- Controle d'impedance : 100 ohms differentiel ±10 % ; des paires differentielles etroitement couplees reduisent les EMI et preservent le rejet de mode commun.

- Perte de canal : A 12 Gbit/s par voie, la marge de perte disparait tres vite. Il faut garder les pistes courtes ; sinon, envisager des laminates low-loss et/ou un redriver ou retimer.

- Contraintes de longueur : Garder les pistes HDMI aussi courtes que possible ; rester sous 50 mm limite les pertes et l'accumulation de skew, d'ou l'importance de placer le connecteur pres du recepteur.

- Choix de couche : Router HDMI sur des couches adjacentes a des plans de masse continus ; le microstrip en couche externe est possible si l'EMI est maitrisee ; la stripline procure une meilleure protection.

- Transitions par vias : Eviter autant que possible les changements de couche. Lorsqu'ils sont inevitables, reduire les stubs, par exemple avec du backdrill lorsque cela a du sens, et conserver la continuite des plans de reference.

- Protection ESD : Les ports HDMI ont besoin d'une protection ESD. La position du composant influe directement sur l'integrite du signal ; il faut donc utiliser des TVS a tres faible capacite, inferieure a 0,3 pF, au plus pres du connecteur.

La mise en oeuvre HDMI 2.1 peut necessiter une simulation d'integrite du signal pour verifier les marges de conformite, surtout quand les traces sont plus longues ou que l'on utilise du FR-4 standard.

Panel Timing Interface Design

L'interface entre la carte principale, ou la T-CON, et le panneau LCD ou OLED transporte des donnees video a des debits dictes par la frequence pixel et la profondeur de couleur. Un panneau 4K a 60 Hz en couleur 10 bits demande environ 17 Gbit/s de donnees video, transportees via LVDS, V-by-One ou des interfaces proprietaires selon le fabricant du panneau et la resolution.

V-by-One HS domine aujourd'hui les implementations TV 4K. Il utilise moins de voies que le LVDS, typiquement 8 paires au lieu de 16 a 32 paires, mais a des debits plus eleves, generalement 3,6 a 4,0 Gbit/s par voie. Le nombre reduit de voies simplifie le routage, mais il augmente les exigences d'integrite du signal sur chaque voie. Les liaisons flex vers le panneau introduisent en plus des discontinuities d'impedance qu'il faut maitriser par le choix du connecteur et le design des terminaisons sur le PCB.

Panel Interface Implementation

- Choix du protocole : La specification du panneau dicte l'interface. V-by-One HS reste la norme pour la plupart des panneaux 4K ; le LVDS demeure courant sur les resolutions inferieures ; certains panneaux 8K recourent a des interfaces proprietaires haut debit.

- Configuration des voies : V-by-One HS utilise typiquement 8 voies pour une dalle 4K 60 Hz 10 bits ; le nombre de voies augmente avec la resolution, la frequence de rafraichissement et la profondeur de couleur.

- Interface connecteur : Les connecteurs du panneau doivent maintenir l'impedance ; le routage du flex entre carte et panneau ajoute perte et skew, ce qui limite le debit maximal atteignable.

- Horloge de reference : Les interfaces panneau exigent des horloges de reference stables ; le choix du quartz ou de l'oscillateur, le filtrage de l'alimentation et l'isolation du routage influencent directement le jitter.

- Conception des terminaisons : Les recepteurs V-by-One utilisent generalement une terminaison integree ; il faut toutefois verifier les besoins de terminaison cote panneau et adapter l'impedance de sortie de la source.

- Considerations EMI : Les signaux du panneau peuvent rayonner a partir des flex ; une bonne mise a la masse du connecteur, le blindage du cable et l'eloignement des circuits sensibles reduisent l'impact EMI.

La conception de l'interface panneau exige une coordination etroite avec les fournisseurs de panneaux afin de confirmer le timing, les niveaux de tension et la compatibilite mecanique des connecteurs.

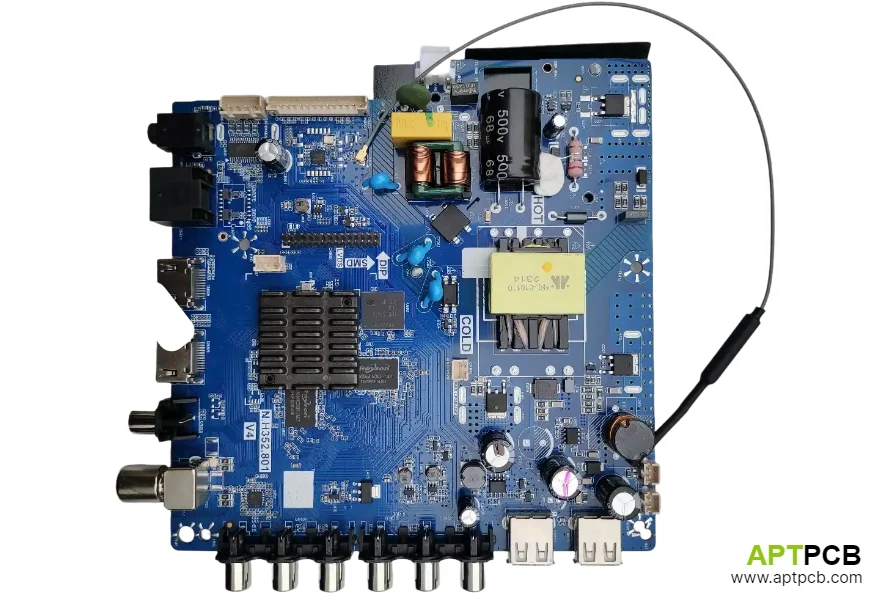

Power Supply Integration and Thermal Considerations

Les cartes principales de Smart TV recoivent generalement du 5 V ou du 12 V depuis la carte d'alimentation, puis generent localement les rails necessaires au SoC, typiquement 0,9 a 1,1 V pour le coeur et d'autres tensions d'E/S, a la memoire, environ 1,2 V pour DDR4 ou LPDDR4, ainsi qu'aux autres sous-systemes. Le reseau de distribution d'alimentation doit accepter les appels de courant transitoires du SoC tout en maintenant la regulation dans des tolerances serrees, souvent de l'ordre de ±3 % sur les rails coeur.

La gestion thermique d'un mainboard TV differe de celle d'un appareil portable. La grande surface de carte facilite la diffusion de chaleur, mais un chassis ferme et la recherche d'un fonctionnement sans ventilateur limitent les moyens de refroidissement. Le PCB sert donc a la fois de support mecanique et de principal heat spreader, la chaleur etant evacuee vers le chassis metallique par l'intermediaire de thermal interface materials.

Power and Thermal Design

- Rendement des convertisseurs DC-DC : Les convertisseurs buck multiphases destines au SoC depassent souvent 90 % d'efficacite ; le choix des inductances et des MOSFET influence a la fois le rendement et la temperature.

- Sequencement des tensions : Le SoC impose une sequence de mise sous tension precise, generalement coeur, puis E/S, puis memoire. Un controleur de sequence ou un PMIC integre assure le bon timing.

- Reseau de decouplage : Le PDN du SoC demande des capacites de reserve, MLCC, polymeres ou electrolytiques, ainsi que des ceramiques de moyenne et haute frequence, reparties sur l'ensemble du reseau.

- Couverture cuivre : Maximiser les plans de cuivre sur les couches internes sous le SoC et les etages de conversion ; 1 oz ou 2 oz de cuivre sur les couches de puissance ameliorent a la fois la capacite en courant et la diffusion thermique.

- Reseaux de vias thermiques : Des matrices de vias denses sous le SoC et les MOSFET de puissance conduisent la chaleur vers les couches internes et la face arriere ; des vias remplis evitent l'aspiration de la soudure a l'assemblage.

- Interface dissipateur : Les zones thermiques du mainboard se connectent au chassis via des thermal interface materials ; un cuivre bien plan fournit un contact thermique regulier, et il faut eviter les bosses de vias dans la zone d'appui.

L'interaction entre distribution de puissance et thermique suppose de maitriser a la fois les principes d'electronique de puissance et les strategies thermiques propres a l'electronique grand public.

Cost-Optimized Manufacturing for Television Products

Les televiseurs subissent une pression extreme sur les couts. Les consommateurs attendent des TV 4K grand format a des prix qui imposent une optimisation agresive a chaque etape du design. Le cout du PCB pese de facon sensible dans le BOM total, ce qui rend le choix des materiaux, l'optimisation du nombre de couches et l'utilisation du panneau critiques. La qualite, en revanche, ne peut pas etre sacrifiee, car les couts de garantie lies aux pannes terrain depassent tres vite les gains de fabrication.

Trouver le bon equilibre entre cout et qualite demande des decisions methodiques : utiliser des materiaux standard quand les performances le permettent, limiter le nombre de couches sans perdre en fonctionnalite, optimiser le contour de la carte pour mieux exploiter le panneau et concevoir en pensant au rendement de production. Associer tot le partenaire de fabrication aide a identifier des pistes d'economie qui preservent la qualite.

Cost Optimization Strategies

- Choix des materiaux : Le FR-4 standard, Tg 140 a 150 degres C, convient a la plupart des applications TV ; les materiaux haute vitesse ne doivent etre utilises que la ou HDMI 2.1 ou une interface critique l'exige reellement.

- Reduction du nombre de couches : Une construction 6 couches convient a beaucoup de cartes principales TV ; 4 couches peuvent suffire sur des conceptions moins complexes avec un routage tres soigne.

- Utilisation du panneau : Les cartes rectangulaires de dimensions standardisees optimisent l'utilisation du panneau ; les formes sur mesure la degradent et augmentent le cout unitaire.

- Optimisation des vias : Les vias traversants coutent bien moins cher que les vias borgnes ou enterres ; il faut donc privilegier le traversant chaque fois que possible et reserver le HDI aux zones vraiment necessaires.

- Finition de surface : HASL reste l'option la plus economique pour les composants traversants ou a grand pas ; ENIG fournit une surface plane pour le pas fin mais rencherit la carte.

- Couverture de test : Un design pensant au test, avec des points de test accessibles, reduit le cout des fixtures et ameliore la detection des defauts ; le flying probe convient bien a des volumes moderes.

Les partenariats en fabrication serie de PCB ouvrent des marges d'optimisation de cout via l'efficacite de process et les economies d'echelle, tout en maintenant les controles qualite.

Technical Summary

La conception d'un PCB de Smart TV doit concilier des exigences avancees d'integrite du signal, notamment pour HDMI 2.1 et les interfaces panneau rapides, avec les objectifs de cout tres stricts propres aux televiseurs grand public. La reussite repose sur des choix architecturaux solides, qu'il s'agisse de la repartition des cartes, du choix des interfaces ou des materiaux, afin de tenir les performances visees tout en maitrisant le cout systeme global.

Les decisions techniques majeures concernent la strategie d'implementation HDMI, donc longueur des pistes, choix de materiau et gestion EMI, la compatibilite de l'interface panneau, c'est-a-dire protocole et connecteur, l'architecture de distribution de puissance du point de vue efficacite et transitoires, et enfin la solution thermique, ou le PCB participe directement au refroidissement.

Le choix du partenaire de fabrication doit examiner a la fois les capacites techniques, comme le routage haute vitesse et la qualite multicouche, et la competitivite economique. Les volumes TV justifient souvent des optimisations que des produits plus faibles volumes ne peuvent pas soutenir. Malgre la pression sur les couts, des systemes qualite robustes restent indispensables, car les depenses de garantie liees aux defauts de fabrication depassent rapidement les gains de production.