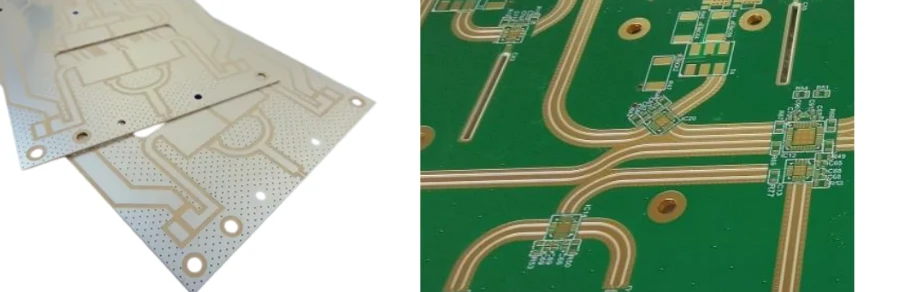

Das Design einer 5G Small Cell Leiterplatte erfordert die Bewältigung einer komplexen Schnittmenge aus Hochfrequenz-Signalintegrität, kompaktem Wärmemanagement und Herstellbarkeit. Im Gegensatz zu herkömmlichen Makro-Basisstationen arbeiten Small Cells (einschließlich Femto-, Pico- und Mikro-Zellen) in beengten Umgebungen, in denen Wärmeableitung und Signalverlust kritische Fehlerpunkte darstellen. APTPCB (APTPCB Leiterplattenfabrik) ist spezialisiert auf die Herstellung dieser Hochleistungsplatinen und stellt sicher, dass strenge HF-Spezifikationen sowohl für Sub-6GHz- als auch für mmWave-Implementierungen erfüllt werden.

Kurzantwort (30 Sekunden)

Für eine erfolgreiche Entwicklung einer 5G Small Cell Leiterplatte müssen Ingenieure verlustarme Materialien und thermische Effizienz priorisieren.

- Materialauswahl: Verwenden Sie Hochfrequenzlaminate (Rogers, Taconic oder Panasonic Megtron 6/7) mit Df < 0,003 und stabilem Dk über weite Frequenzbereiche.

- Lagenaufbau-Strategie: Implementieren Sie hybride Lagenaufbauten (FR4 + Hochfrequenzmaterial), um Kosten und HF-Leistung auszugleichen.

- Wärmemanagement: Integrieren Sie Kupfermünzen, schwere Kupferschichten (2oz+) oder dichte thermische Via-Arrays unter PA-Komponenten (Leistungsverstärker).

- Impedanzkontrolle: Halten Sie eine strenge Toleranz von ±5% oder ±7% auf HF-Leitungen ein; die Standardtoleranz von ±10% ist oft unzureichend für 5G mmWave.

- Oberflächenveredelung: Bevorzugen Sie ENIG oder ENEPIG, um ebene Oberflächen für Fine-Pitch-Komponenten und Drahtbonden zu gewährleisten, und vermeiden Sie HASL aufgrund seiner Unebenheit.

- PIM-Minderung: Minimierung der passiven Intermodulation (PIM) durch die Verwendung von flachem Kupferfolie (VLP/HVLP) und die Begrenzung der Lötstoppmaske über Hochfrequenzleiterbahnen.

Wann 5G Small Cell PCBs eingesetzt werden (und wann nicht)

Das Verständnis des spezifischen Einsatzszenarios ist entscheidend, bevor die PCB-Architektur finalisiert wird. Small Cells überbrücken die Lücke zwischen massiven Makro-Türmen und Endbenutzergeräten.

Wann 5G Small Cell PCB-Technologie eingesetzt werden sollte:

- Städtische Gebiete mit hoher Dichte: Wenn die Netzwerkkapazität in Stadien, Einkaufszentren oder Stadtzentren erhöht werden muss, wo die Infrastruktur von 5G Makrozellen-PCBs nicht eindringen oder die Last bewältigen kann.

- mmWave-Bereitstellung: Für Kurzstrecken-Anwendungen mit hoher Bandbreite (24 GHz und höher), die spezielle Substrate zur Minimierung der Signaldämpfung erfordern.

- Innenraumabdeckung: Unternehmensumgebungen, die dedizierte 5G Femto Cell PCB oder 5G Pico Cell PCB Einheiten benötigen, um ein konsistentes Signal durch Wände zu gewährleisten.

- Lückenfüllung: Um Funklöcher am Rande des Abdeckungsbereichs einer Makrozelle zu eliminieren.

- Anwendungen mit geringer Latenz: Industrielle IoT (IIoT)-Setups, bei denen die Verarbeitung näher am Benutzer erfolgen muss (Edge Computing).

Wann es möglicherweise nicht die richtige Lösung ist:

- Ländliche Abdeckung großer Gebiete: Ein Standard 5G Makrozellen-PCB ist kostengünstiger für die Abdeckung großer, dünn besiedelter geografischer Gebiete.

- Nur Niederfrequenz-IoT: Wenn das Gerät nur sporadische Datenpakete auf NB-IoT- oder LoRaWAN-Frequenzen (unter 1 GHz) ohne hohe Durchsatzanforderungen überträgt, sind Standard-FR4-Leiterplatten ausreichend.

- Extrem kostengünstige Unterhaltungselektronik: Die für 5G-Small Cells benötigten Materialien (PTFE, keramikgefüllte Kohlenwasserstoffe) sind deutlich teurer als Standard-Epoxidglas.

- Passive Repeater: Wenn das Gerät Signale nicht verarbeitet, sondern nur reflektiert, kann ein vollständiger aktiver PCB-Lagenaufbau unnötig sein.

Regeln & Spezifikationen

Um die Zuverlässigkeit einer 5G Small Cell PCB zu gewährleisten, müssen spezifische Designregeln eingehalten werden. Abweichungen von diesen Werten führen oft zu Signalverschlechterung oder thermischem Versagen.

| Regel | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Bei Missachtung |

|---|---|---|---|---|

| Dielektrizitätskonstante (Dk) | 3.0 – 3.5 (Stabil) | Ein niedrigerer Dk reduziert die Signalverzögerung; Stabilität gewährleistet eine konsistente Impedanz über Frequenzen hinweg. | Datenblatt vs. Frequenzdiagramme überprüfen. | Signal-Timing-Fehler und Impedanzfehlanpassungen. |

| Verlustfaktor (Df) | < 0.003 @ 10GHz | Minimiert den Signalverlust (Einfügedämpfung), der für die Energieeffizienz in Small Cells entscheidend ist. | Vektor-Netzwerkanalysator (VNA)-Tests an Coupons. | Hohe Signaldämpfung; reduzierte Reichweite; Überhitzung. |

| Kupferrauheit | < 2 µm (VLP/HVLP) | Der Skin-Effekt bei 5G-Frequenzen zwingt den Strom an die Oberfläche; raues Kupfer erhöht den Widerstand und die Verluste. | REM-Analyse oder Spezifikationsblatt-Verifizierung. | Erhöhte Einfügedämpfung und Phasenverzerrung. |

| Impedanztoleranz | ±5% (HF), ±10% (Digital) | Gleicht Übertragungsleitungen an Quelle/Last an, um Reflexionen (VSWR) zu verhindern. | Impedanzrechner & TDR-Tests. | Hohe Rückflussdämpfung; Signalreflexion; reduzierte Datenraten. |

| Wärmeleitfähigkeit | > 0.5 W/mK (Dielektrikum) | Kleine Zellen sind umschlossen; die Leiterplatte selbst muss Wärme von aktiven Komponenten ableiten. | Thermische Simulationssoftware (CFD). | Bauteilüberhitzung; Drosselung; Geräteausfall. |

| Via-Aspektverhältnis | < 8:1 (Durchkontaktierung), < 0.8:1 (Mikro) | Gewährleistet zuverlässige Beschichtung und Konnektivität in HDI-Leiterplatten mit hoher Lagenzahl. | Querschnittsanalyse (Mikroschliff). | Unterbrechungen; Risse im Via-Zylinder während des Reflow-Lötens; unzuverlässige Vias. |

| Lötstopplacksteg | > 3 mil (0.076mm) | Verhindert Lötbrücken zwischen Fine-Pitch-Pads, die in HF-Modulen üblich sind. | DFM-Prüfung in CAM-Software. | Kurzschlüsse während der Montage; geringere Ausbeute. |

| Schälfestigkeit | > 0.8 N/mm | Hochfrequenzmaterialien (PTFE) weisen oft eine schlechte Haftung auf; entscheidend für die Zuverlässigkeit. | Schältest gemäß IPC-TM-650. | Pad-Ablösung während der Nacharbeit oder thermischen Zyklen; Delamination. |

| Lagenregistrierung | ± 3 mil | Fehlausrichtung beeinflusst die Kopplung zwischen Lagen in HF-Strukturen (z.B. breitseitig gekoppelte Leitungen). | Röntgeninspektion. | Unvorhersehbare HF-Leistung; Impedanzschwankungen. |

| Feuchtigkeitsaufnahme | < 0,1% | Wasser ist polar und absorbiert HF-Energie; hohe Absorption verändert Dk/Df. | Umwelttestkammerprüfung. | Leistungsdrift in feuchten Umgebungen; Delamination. |

Implementierungsschritte

Der Übergang von Spezifikationen zu einer physischen Platine erfordert einen disziplinierten Arbeitsablauf. Die Einhaltung dieser Schritte stellt sicher, dass die 5G Small Cell Leiterplatte sowohl elektrische als auch mechanische Anforderungen erfüllt.

Frequenzbänder & Architektur definieren

- Aktion: Bestimmen Sie, ob das Design Sub-6GHz, mmWave oder beides ist.

- Schlüsselparameter: Betriebsfrequenz (z.B. 3,5 GHz vs. 28 GHz).

- Abnahmekontrolle: Blockschaltbild mit dem HF-Ingenieurteam bestätigt.

Materialauswahl & Lagenaufbau-Design

- Aktion: Wählen Sie ein Laminat basierend auf dem Verlustbudget. Für mmWave wählen Sie Rogers- oder Taconic-Materialien. Für kostensensible Sub-6GHz-Anwendungen ziehen Sie Megtron 6 in Betracht.

- Schlüsselparameter: Df-Wert und CTE (Wärmeausdehnungskoeffizient).

- Abnahmekontrolle: Die Lagenaufbau-Simulation zeigt, dass Impedanzziele mit Standard-Prepreg-Dicken erreichbar sind.

Planung der Wärmestrategie

- Aktion: Hochleistungskomponenten (PAs, FPGAs) identifizieren und Wärmeableitungspfade planen. Entscheidung zwischen thermischen Vias, Kupfer-Inserts oder metallkaschierten PCBs.

- Schlüsselparameter: Sperrschicht-Umgebung-Wärmewiderstand.

- Abnahmekontrolle: Thermische Simulation bestätigt, dass die maximale Sperrschichttemperatur unter 100°C (oder der Bauteilgrenze) bleibt.

Layout & HF-Leitungsführung

- Aktion: HF-Leitungen zuerst verlegen. Leiterbahnen kurz und direkt halten. 90-Grad-Biegungen vermeiden; 45-Grad- oder gekrümmte Leitungsführung verwenden, um Reflexionen zu minimieren.

- Schlüsselparameter: Leiterbahnbreite und -abstand (für 50Ω berechnet).

- Abnahmekontrolle: DRC (Design Rule Check) besteht für Mindestabstand und Leiterbahnbreite.

Erdung & Abschirmung

- Aktion: Stitching-Vias entlang der HF-Leiterbahnen (Via-Fencing) platzieren, um Felder einzudämmen. Sicherstellen, dass durchgehende Masseflächen unter HF-Leitungen nicht unterbrochen sind.

- Schlüsselparameter: Via-Abstand (< λ/20 der höchsten Frequenz).

- Abnahmekontrolle: Keine Rückwegdiskontinuitäten in der Simulation gefunden.

DFM & Prototypenbau

- Aktion: Eine DFM-Richtlinienprüfung durchführen, um sicherzustellen, dass das Design von APTPCB herstellbar ist.

- Schlüsselparameter: Mindestbohrungsgröße, Restring und Leiterbahn/Abstand.

- Abnahmekontrolle: Sauberer CAM-Bericht ohne kritische Fertigungsverletzungen.

Fertigung & Prüfung

- Aktion: Gerber-Dateien zur Fertigung senden. TDR-Berichte (Time Domain Reflectometry) anfordern.

- Schlüsselparameter: Überprüfung der Impedanztoleranz.

- Abnahmekontrolle: Physische Platinen bestehen die Sichtprüfung und TDR-Impedanztests.

Fehlermodi & Fehlerbehebung

Selbst bei sorgfältigem Design können während des Tests oder der Bereitstellung Probleme auftreten. Hier erfahren Sie, wie Sie häufige Ausfälle von 5G Small Cell PCBs beheben können.

1. Hohe Einfügedämpfung (Signaldämpfung)

- Symptom: Signalstärke am Ausgang ist niedriger als berechnet; reduzierte Reichweite.

- Ursachen: Falsches Material (hoher Df), raue Kupferfolie, Lötstopplack über HF-Leiterbahnen.

- Prüfungen: Materialchargendaten überprüfen; prüfen, ob Lötstopplack von HF-Leitungen entfernt wurde (Lötstopplack erhöht die Dämpfung).

- Behebung: Neuentwicklung mit VLP-Kupfer oder Material mit niedrigerem Df; Lötstopplack von Hochgeschwindigkeitsleiterbahnen entfernen.

- Prävention: "Lötstopplacköffnung" über HF-Leiterbahnen in den Fertigungsnotizen angeben.

2. Passive Intermodulation (PIM)

- Symptom: Rauschen steigt an; Interferenzen in Empfangsbändern; reduzierter Datendurchsatz.

- Ursachen: Ferromagnetische Materialien (Nickel) im Signalpfad, schlechte Lötstellen, rostige Steckverbinder, raues Kupfer.

- Prüfungen: PIM-Tests; Oberflächenveredelung prüfen (ENIG kann aufgrund von Nickel PIM verursachen; Silber oder OSP sind besser für reines HF).

- Behebung: Oberflächenveredelung auf Immersion Silber oder OSP umstellen; Lötqualität verbessern.

- Prävention: Vermeiden Sie nickelbasierte Oberflächen auf Hochleistungs-HF-Leitungen; verwenden Sie PIM-zertifizierte Steckverbinder.

3. Thermische Abschaltung / Überhitzung

- Symptom: Gerät startet zufällig neu oder drosselt die Leistung nach Minuten des Betriebs.

- Ursachen: Unzureichende thermische Vias, eingeschlossene Wärme in inneren Schichten, schlechter Kontakt zum Kühlkörper.

- Prüfungen: Wärmebildkamera-Aufnahmen; Überprüfung der Wärmeleitpasten-Anwendung; Überprüfung der Via-Plattierungsdicke.

- Behebung: Externen Kühlkörper hinzufügen; Luftstrom verbessern.

- Prävention: Design mit eingebetteten Kupfer-Coins oder deutliche Erhöhung der thermischen Via-Dichte unter Leistungsverstärkern (PAs).

4. Impedanzfehlanpassung (Hoher VSWR)

- Symptom: Signalreflexion, Leistungsverlust, potenzielle Beschädigung des Senders.

- Ursachen: Ätzschwankungen, falsche Lagenaufbauhöhe, Variation der Dielektrikumsdicke.

- Prüfungen: TDR-Messung; Querschnittsanalyse der Leiterbahnbreite.

- Behebung: Abstimmen von Anpassungsnetzwerken (falls möglich); andernfalls Leiterplattenausschuss.

- Prävention: Impedanz-Coupons auf dem Panel anfordern; strenge Toleranz von ±5% spezifizieren.

5. Delamination während des Reflow-Lötens

- Symptom: Blasenbildung oder Trennung der Schichten nach der Bestückung.

- Ursachen: Feuchtigkeit im PCB eingeschlossen; CTE-Fehlanpassung zwischen Hybridmaterialien (z.B. PTFE und FR4).

- Prüfungen: Backprotokolle; Materialkompatibilitätstabellen.

- Behebung: Keine für betroffene Leiterplatten.

- Prävention: Leiterplatten vor der Bestückung backen; hoch-Tg-Materialien verwenden; sicherstellen, dass Hybridmaterialien einen kompatiblen Z-Achsen-CTE aufweisen. 6. Via-Fehler (Unterbrechung)

- Symptom: Zeitweise Konnektivität, besonders nach thermischer Zyklisierung.

- Ursachen: Rissbildung im Via-Zylinder aufgrund von Z-Achsen-Ausdehnung; schlechte Beschichtungsqualität.

- Prüfungen: Mikroschnittanalyse; Durchgangsprüfung.

- Behebung: Keine.

- Prävention: Materialien mit niedrigem Z-Achsen-Wärmeausdehnungskoeffizienten (CTE) verwenden; sicherstellen, dass das Aspektverhältnis innerhalb der Fertigungsgrenzen liegt (z.B. < 8:1).

Designentscheidungen

Die Fehlerbehebung zeigt oft, dass die Grundursache in frühen Designentscheidungen liegt. Bei der Planung einer 5G Small Cell Leiterplatte stehen Ingenieure vor mehreren kritischen Kompromissen.

Hybrid- vs. Homogener Lagenaufbau

- Entscheidung: Soll die gesamte Platine aus Hochfrequenzmaterial bestehen oder nur die äußeren Lagen?

- Auswirkung: Eine homogene PTFE-Platine bietet die beste elektrische Leistung, ist aber mechanisch weich, schwer zu verarbeiten und teuer. Ein Hybrid-Lagenaufbau (PTFE außen / FR4 innen) reduziert die Kosten und verbessert die Steifigkeit, birgt jedoch Risiken durch CTE-Fehlanpassung.

- Empfehlung: Für 5G Micro Cell Leiterplatten-Designs, bei denen Kosten ein Faktor sind, sollte ein Hybridansatz verwendet werden. Für Ultra-Hochleistungs-mmWave-Einheiten kann ein homogener oder mehrschichtiger Fusionsbond-Ansatz erforderlich sein.

HDI vs. Durchkontaktierung

- Entscheidung: High Density Interconnect (HDI) mit Microvias oder Standard-Durchkontaktierungen verwenden?

- Auswirkung: 5G-Chipsätze (BGA) haben oft feine Raster (0,4 mm oder weniger), die HDI erfordern. HDI verbessert die Signalintegrität durch Reduzierung von Via-Stubs, erhöht aber die Kosten.

- Empfehlung: HDI ist für moderne 5G Small Cell PCB-Designs nahezu obligatorisch, um BGA-Breakout zu ermöglichen und parasitäre Kapazitäten zu minimieren.

Oberflächenauswahl

- Entscheidung: ENIG, ENEPIG, Tauchsilber oder OSP?

- Auswirkung: ENIG ist robust, aber Nickel ist magnetisch und kann PIM verursachen. Tauchsilber ist hervorragend für HF, läuft aber leicht an. OSP ist günstig und gut für HF, hat aber eine kurze Haltbarkeit.

- Empfehlung: Verwenden Sie Tauchsilber oder ENEPIG für Hochfrequenz-5G-Leiterplatten, um Lötbarkeit und HF-Leistung auszugleichen.

Häufig gestellte Fragen

F1: Was ist der Hauptunterschied zwischen einer 5G Small Cell PCB und einer Macro Cell PCB? A: Der Hauptunterschied liegt in Größe und Leistung. 5G Small Cell PCB-Designs sind kompakt, haben eine geringere Leistung und erfordern oft eine höhere Integrationsdichte (HDI) im Vergleich zum großen, leistungsstarken, modularen Aufbau einer 5G Macro Cell PCB.

F2: Warum sind Hybrid-Stackups für 5G Small Cells beliebt? A: Sie gleichen Kosten und Leistung aus.

- HF-Schichten verwenden teure verlustarme Materialien (Rogers/Taconic).

- Digital-/Leistungsschichten verwenden Standard-FR4.

- Dies reduziert die gesamten Materialkosten bei gleichzeitiger Aufrechterhaltung der Signalintegrität.

F3: Kann ich Standard-FR4 für 5G Small Cell PCBs verwenden? A: Im Allgemeinen nein, besonders nicht für den HF-Pfad.

- Standard-FR4 hat einen hohen Df (Verlust) und einen instabilen Dk bei 5G-Frequenzen.

- Es kann für den digitalen Steuerteil oder die Stromverteilungsschichten in einem Hybrid-Stackup verwendet werden.

F4: Wie lange ist die Lieferzeit für die Herstellung dieser PCBs? A: Die Lieferzeiten sind aufgrund der Materialverfügbarkeit typischerweise länger als bei Standardplatinen.

- Standard FR4: 3-5 Tage.

- Hybrid-/HF-Materialien: 10-15 Tage (abhängig vom Lagerbestand an Rogers-/Panasonic-Materialien).

Q5: Wie manage ich die Wärme in einem so kleinen Gehäuse? A: Ein aggressives Wärmedesign ist erforderlich.

- Verwenden Sie Kupfer-Coins (eingebettetes Metall).

- Verwenden Sie Metallkern-Leiterplatten (MCPCB) für Leistungsstufen.

- Maximieren Sie die Anordnung von thermischen Vias.

Q6: Was ist der Unterschied zwischen Femto-, Pico- und Micro-Cell-Leiterplatten? A: Sie unterscheiden sich hauptsächlich in der Ausgangsleistung und der Abdeckungsreichweite.

- 5G Femto Cell PCB: Geringste Leistung (Zuhause/Büro), kleinster Formfaktor.

- 5G Pico Cell PCB: Mittlere Leistung (Unternehmen/öffentliche Innenbereiche), etwas größer.

- 5G Micro Cell PCB: Höhere Leistung (städtischer Außenbereich), robust, die größte der Small Cells.

Q7: Warum ist PIM (Passive Intermodulation) ein Problem? A: PIM erzeugt Interferenzen, die die Upload-Geschwindigkeiten blockieren.

- Es wirkt wie eine Selbststörung.

- Kritisch in 5G, wo die Bandbreite maximiert wird.

Q8: Benötige ich für 5G Small Cell PCBs eine Rückbohrung? A: Ja, wenn Durchkontaktierungen für Hochgeschwindigkeitssignale verwendet werden.

- Die Rückbohrung entfernt den ungenutzten Via-Stumpf.

- Stümpfe wirken als Antennen/Filter, die die Signalqualität bei hohen Frequenzen verschlechtern.

Q9: Welcher Kupferfolientyp wird bevorzugt? A: VLP (Very Low Profile) oder HVLP (Hyper Very Low Profile).

- Glatteres Kupfer reduziert Verluste durch den Skin-Effekt.

- Unerlässlich für die Effizienz von mmWave.

Q10: Wie überprüft APTPCB die Impedanzkontrolle? A: Wir verwenden TDR (Zeitbereichsreflektometrie) an Testcoupons, die auf der Produktionsplatte enthalten sind.

- Wir messen die tatsächliche Impedanz im Vergleich zum Designziel.

- Berichte werden mit der Lieferung bereitgestellt.

F11: Ist die Blind- und Buried-Via-Technologie erforderlich? A: Oft, ja.

- Um Platz in kompakten Small Cells zu sparen.

- Um die Signalintegrität durch Verkürzung der Via-Stubs zu verbessern.

F12: Welche Kostenauswirkungen hat die Verwendung von Rogers-Material? A: Rogers-Materialien können das 3- bis 10-fache der Kosten von FR4 betragen.

- Aus diesem Grund werden Hybrid-Stackups verwendet, um das Volumen teuren Materials zu minimieren.

Verwandte Seiten & Tools

- Materialdaten: Rogers PCB-Materialien

- Design-Tool: Impedanzrechner

- Fertigungsprüfungen: DFM-Richtlinien

Glossar (Schlüsselbegriffe)

| Begriff | Definition | Kontext in 5G Small Cell PCB |

|---|---|---|

| mmWave | Millimeterwelle (24 GHz - 100 GHz). | Erfordert Materialien mit extrem geringen Verlusten und engen Toleranzen. |

| Sub-6GHz | Frequenzen unter 6 GHz. | Die "Abdeckungsschicht" von 5G; weniger anspruchsvoll als mmWave, aber schwieriger als 4G. |

| PIM | Passive Intermodulation. | Signalverzerrung, verursacht durch Nichtlinearitäten in passiven Komponenten (Steckverbinder, Leiterbahnen). |

| Dk (Dielektrizitätskonstante) | Maß für die Fähigkeit eines Materials, elektrische Energie zu speichern. | Beeinflusst Impedanz und Signalpropagationsgeschwindigkeit. |

| Df (Dissipationsfaktor) | Maß dafür, wie viel Energie als Wärme im Material verloren geht. | Ein niedrigerer Df ist entscheidend für die 5G-Effizienz. |

| CTE | Koeffizient der thermischen Ausdehnung. | Wie stark sich das Material bei Erwärmung ausdehnt; eine Fehlanpassung führt zu Delamination. |

| MIMO | Multiple Input Multiple Output. | Verwendung mehrerer Antennen; erhöht die PCB-Komplexität und die Routing-Dichte. |

| Beamforming | Fokussierung des Signals auf einen bestimmten Benutzer. | Erfordert eine präzise Phasensteuerung auf dem PCB-Antennenarray. |

| Backhaul | Die Verbindung von der Small Cell zum Kernnetzwerk. | Die Leiterplatte muss Hochgeschwindigkeits-Glasfaser- oder drahtlose Backhaul-Schnittstellen unterstützen. |

| Small Cell | Drahtlose Zugangspunkte mit geringer Leistung (Femto, Pico, Mikro). | Das Gerät, das die Leiterplatte beherbergt; wird zur Verdichtung verwendet. |

| Hybrid Stackup | Kombination verschiedener Laminatmaterialien. | Wird verwendet, um Kosten/Leistung in 5G Small Cell PCB-Designs zu optimieren. |

Fazit

Das Design einer 5G Small Cell PCB ist ein Balanceakt zwischen Hochfrequenzleistung, thermischer Beständigkeit und Fertigbarkeit. Ob Sie eine 5G Femto Cell PCB für den Innenbereich oder eine robuste 5G Micro Cell PCB für die Verdichtung im Außenbereich bauen, die physikalischen Regeln bezüglich Dk, Df und Wärmeableitung bleiben absolut. Durch die Einhaltung der oben genannten Spezifikationen – insbesondere hinsichtlich Materialauswahl, Hybrid-Stackups und PIM-Minderung – können Ingenieure kostspielige Neuentwicklungen und Feldausfälle vermeiden. APTPCB unterstützt diesen Prozess vom Prototyp bis zur Serienproduktion und bietet die spezialisierten Materialien und DFM-Expertise, die für Netzwerke der nächsten Generation erforderlich sind.

Für eine detaillierte Überprüfung Ihres spezifischen Stackups oder um genaue Preise für Hochfrequenzlaminate zu erhalten, fordern Sie noch heute ein Angebot an.