Lagenaufbau & CAM

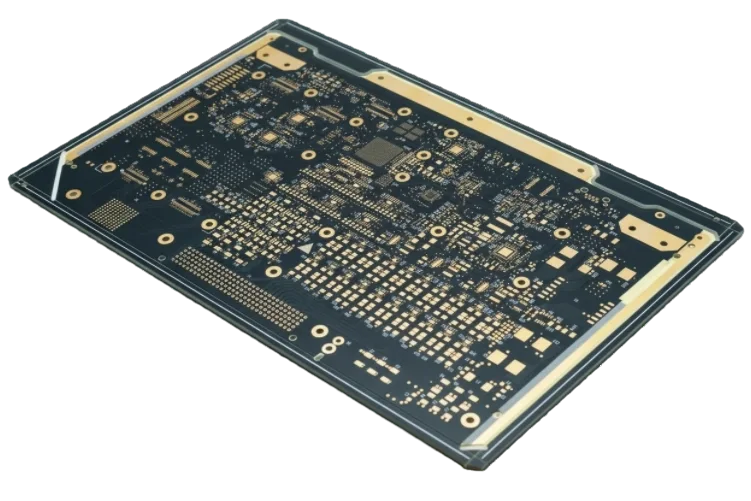

Wir simulieren Impedanz, Kupferausgleich und Laminationssequenzen vor der Freigabe.

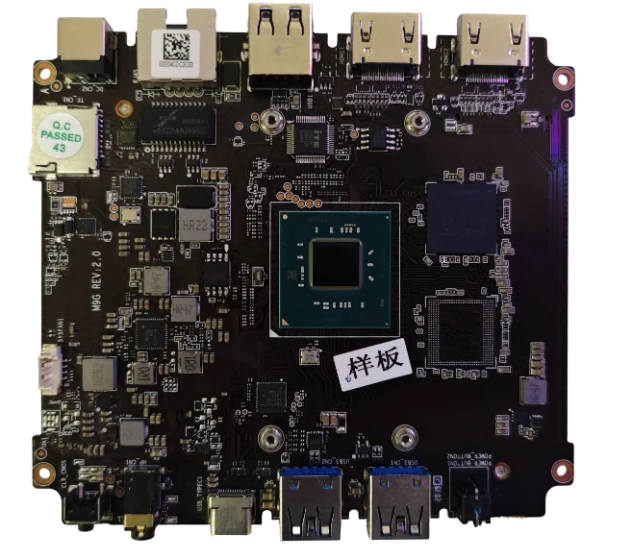

- Bestätigen Sie Materialien und akzeptable Alternativen.

- Definieren Sie den sequenziellen Laminationsplan.

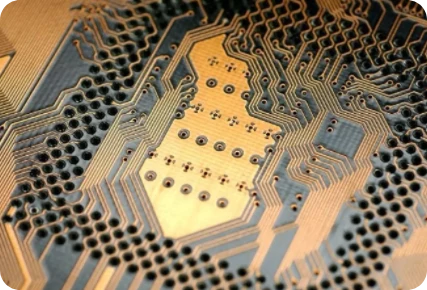

- Planen Sie Impedanz-Coupons und Referenzebenen.

- Spezifizieren Sie Via-Strukturen, Füllung und Backdrill-Anforderungen.

- Dokumentieren Sie Oberflächenveredelung, Beschichtung und Backanweisungen.