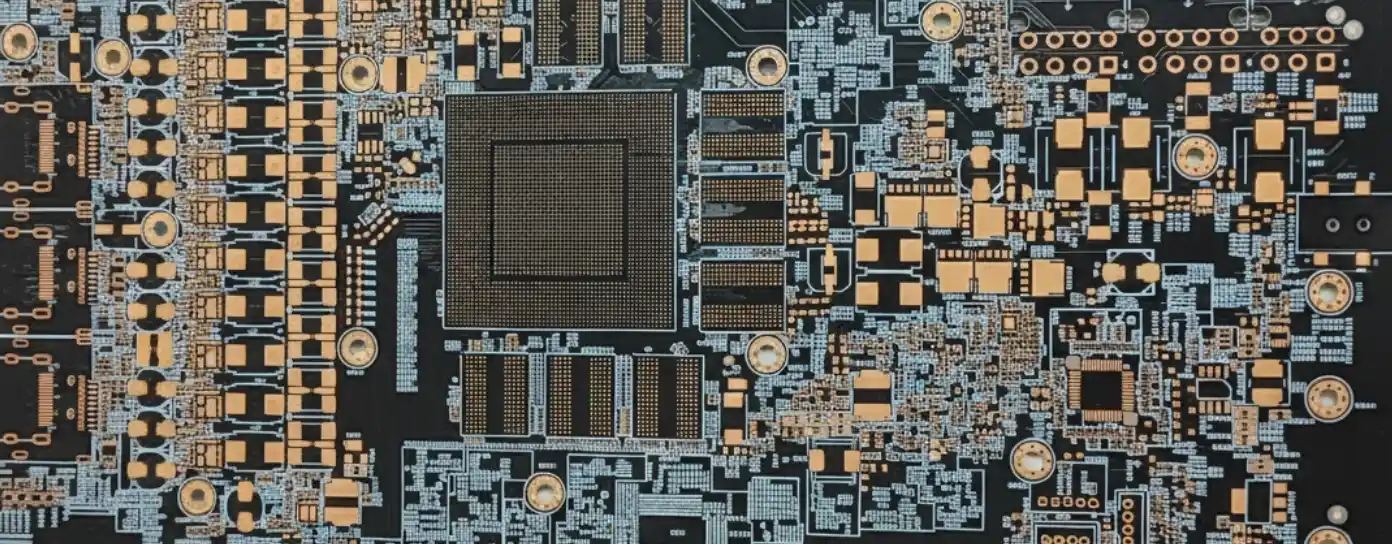

CAM-Engineering-Workflow — Design-Daten in einen fertigungstauglichen HDI-Prozess überführen

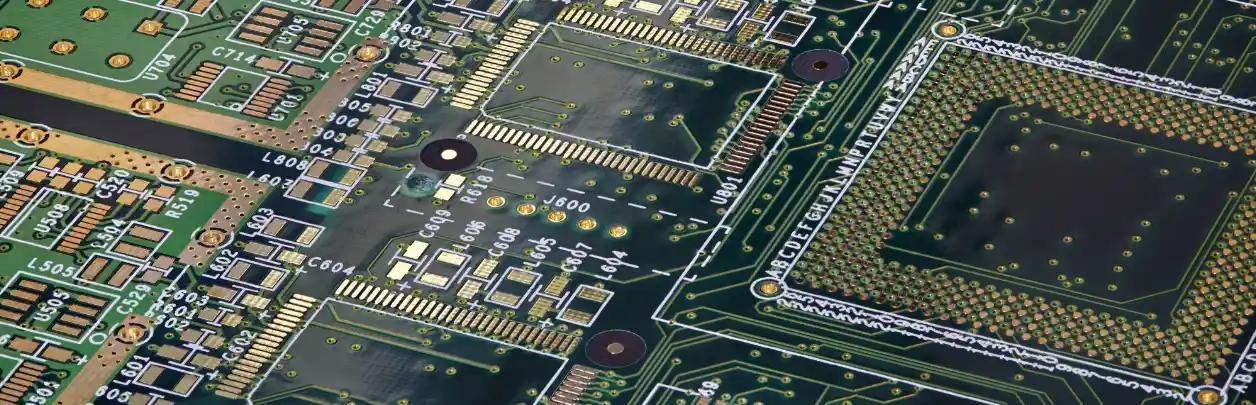

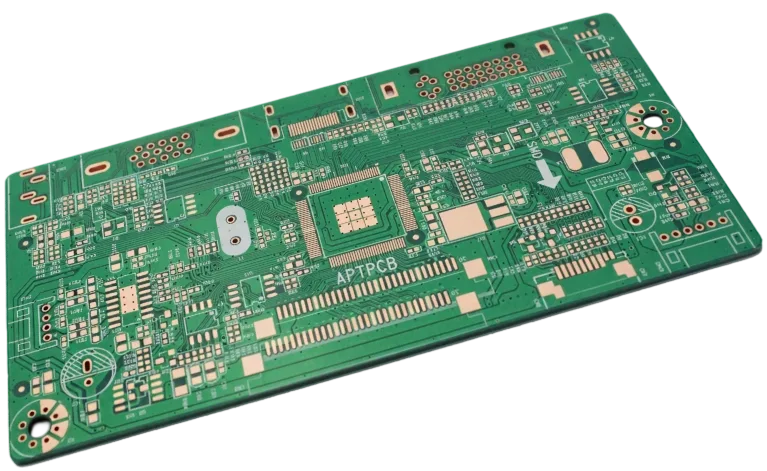

Im HDI-PCB Fertigungsprozess wird die erste zentrale Phase von CAM-Ingenieuren geführt, die die Designabsicht in einen präzisen, fertigungstauglichen Produktionsplan übersetzen. Nach Eingang von Gerber- oder ODB++-Daten prüfen sie Stackup-Strukturen, Microvia-Konfigurationen und Impedanzanforderungen. Durch DFM-Analyse, Bohrprogrammierung und Erstellung von Fertigungsnotizen stellen CAM-Ingenieure sicher, dass jedes Designmerkmal mit den Fertigungsmöglichkeiten übereinstimmt.

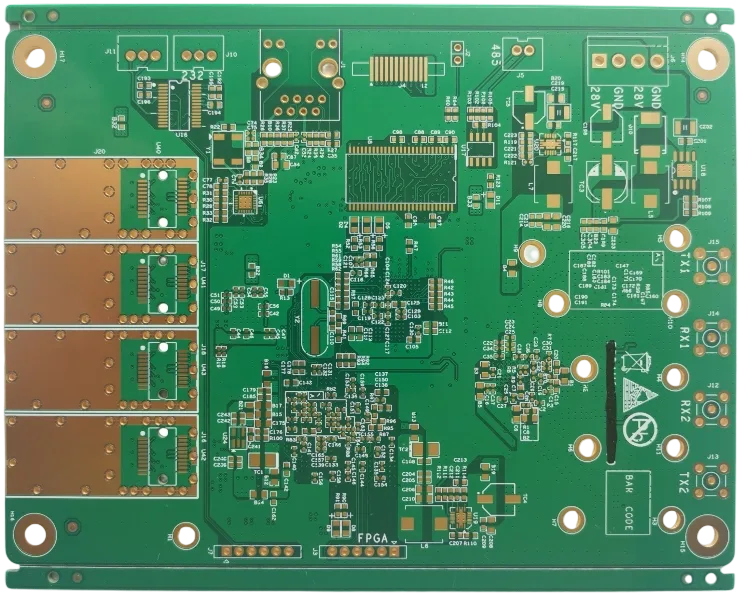

- Stackup-Struktur und SBU-Layer-Konfiguration bestätigen.

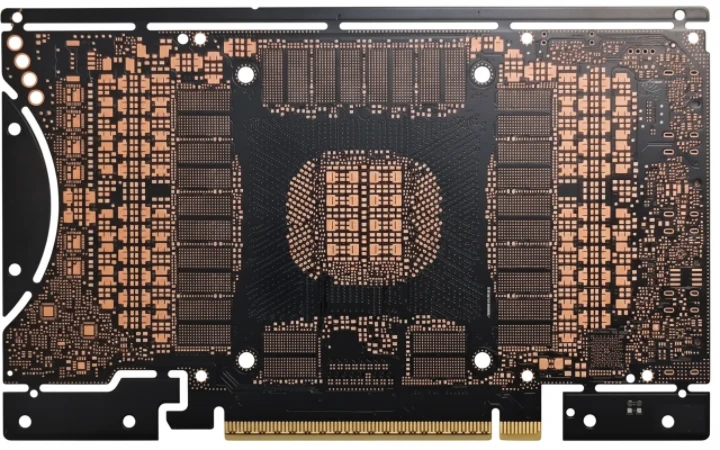

- Microvia-Typ (staggered/stacked), VIPPO und Via-in-Pad-Regeln festlegen.

- DFM-Analyse für Leiterbahn/Abstand, Annular Ring und Via-zu-Trace-Abstände durchführen.

- Laserbohrprogramme und Kupferfüllprofile definieren.

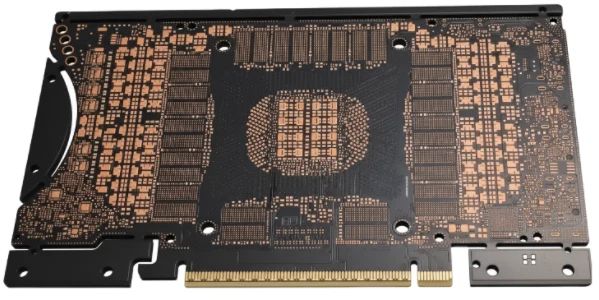

- Impedanzcoupons planen und TDR-Messstrategie festlegen.

- Materialauswahl (FR-4/Low-Loss) und Tg/CTE-Kompatibilität verifizieren.

- Mit Production Engineering die Fertigbarkeit und Prozessfolge vor Freigabe validieren.