Hochgeschwindigkeits-CAM & SI-Koordination

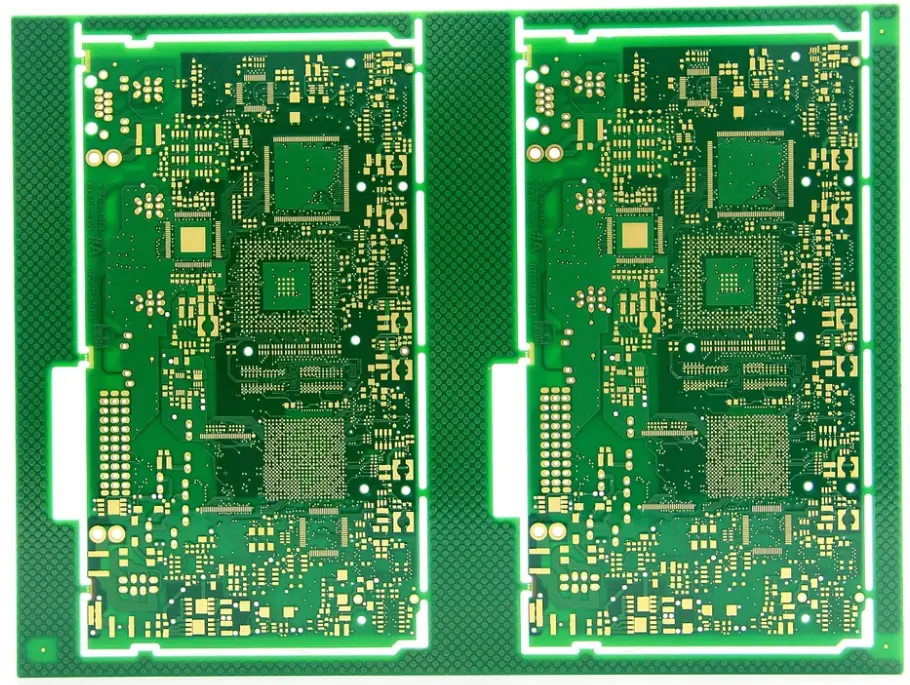

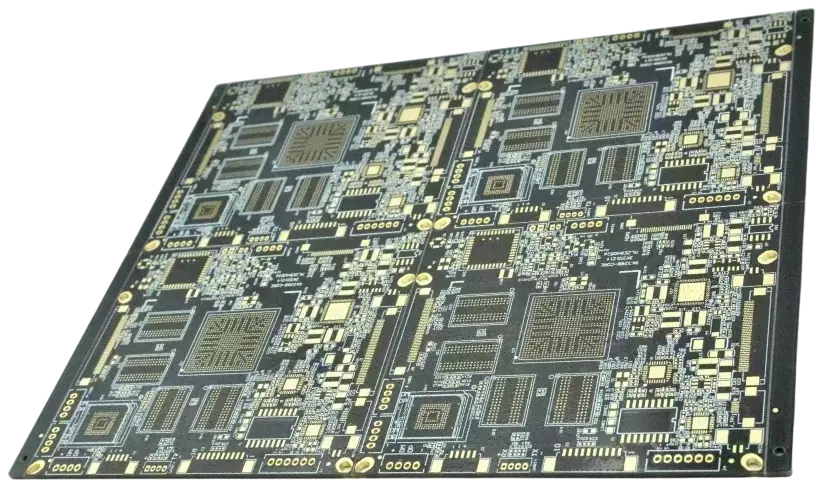

CAM-Ingenieure übersetzen SI-Beschränkungen in Fertigungsdateien, definieren Lagenaufbauten, Bohrkarten, Impedanz-Coupons und Backdrill-Koordinaten.

- Dokumentieren Sie Dielektrikumsziele, Kupferrauheit und Harzgehalt pro Lage.

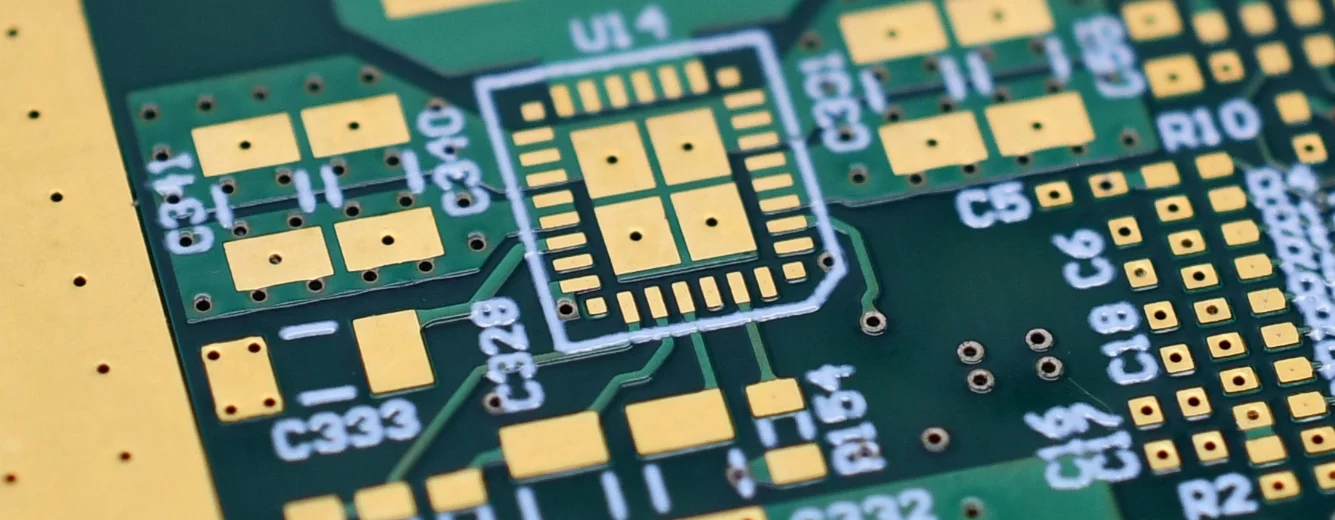

- Definieren Sie Impedanz-Coupons, differentielle Paargeometrien und Toleranz-Lagenaufbauten.

- Planen Sie Backdrill-Tiefen, VIPPO-Füllungen und Referenzebenen-Stitching-Vias.

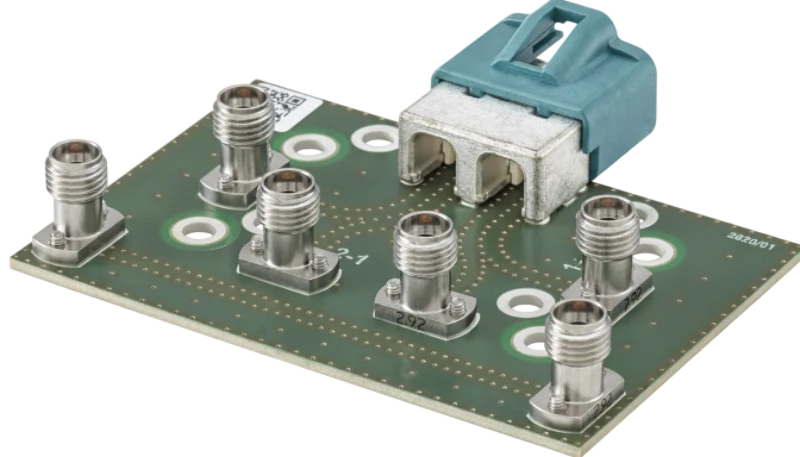

- Koordinieren Sie Press-Fit-Steckverbinder-Footprints und Tear-Drop-Anforderungen.

- Simulieren oder validieren Sie Via-Übergänge mit SI-Tool-Ausgaben.

- Geben Sie Handhabungs- und Backanweisungen für verlustarme Materialien.

- Geben Sie Fertigungsnotizen heraus, die zulässige Substitutionen und QC-Prüfpunkte detaillieren.