Compute

Compute Accelerator

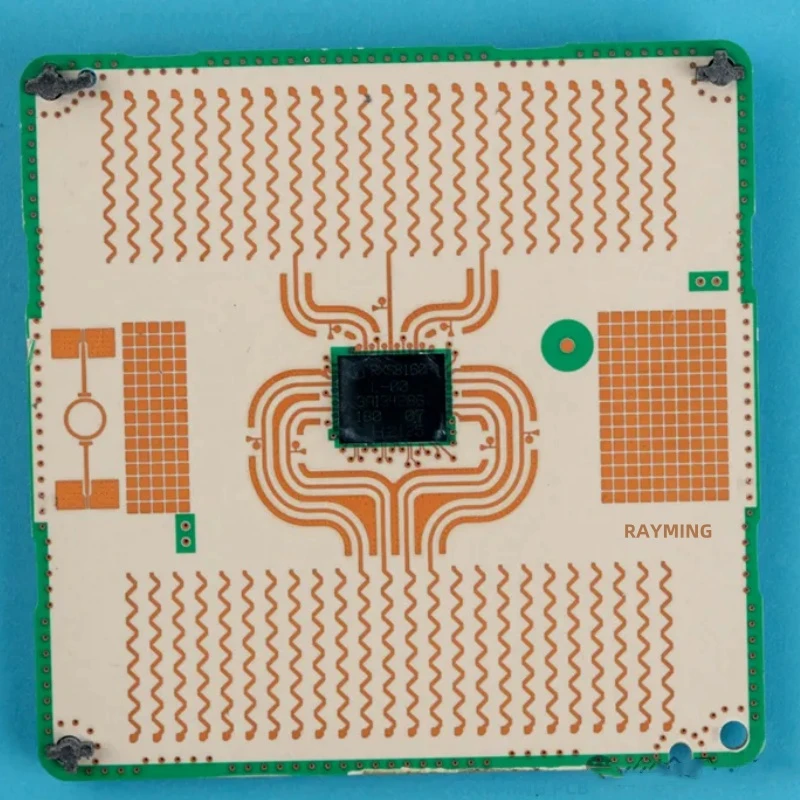

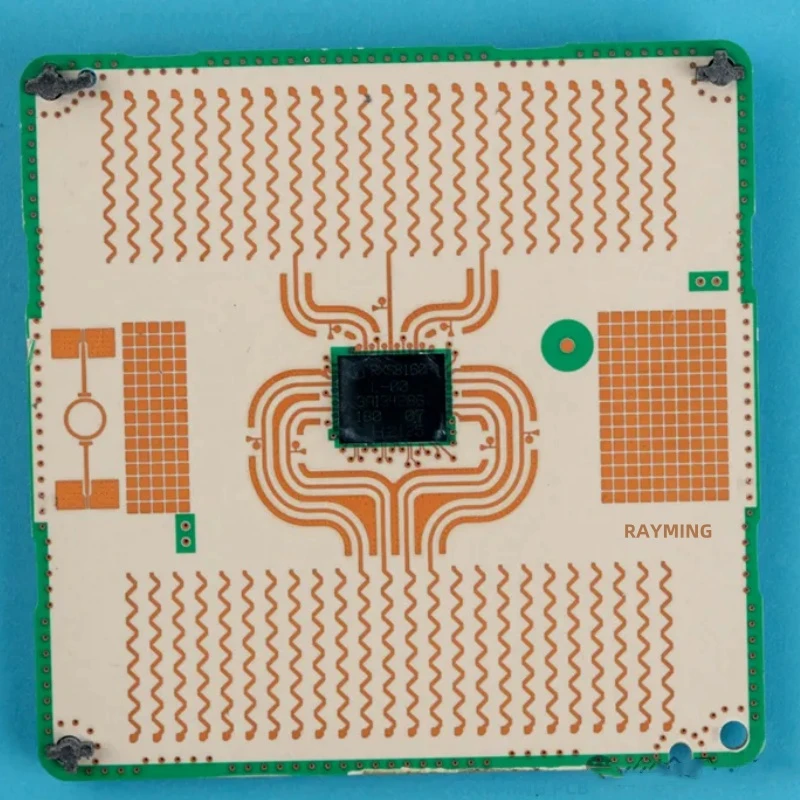

0.3 mm BGA mit Boundary-Scan, Underfill und Vacuum-Reflow-Logs.

Boundary-scanUnderfillVacuum

0.3 MM PITCH • 01005 • VOID CONTROL

DFM, Stencil/Paste, ±25 µm Placement, Stickstoff-Reflow, AXI/Void-Tracking, Underfill und kontrollierter Rework halten verdeckte Lötstellen stabil – vom Pilot bis zur Serie.

Wir kombinieren Prozesskontrolle mit Inspektionsdaten, damit verdeckte Lötstellen mit Nachweisen ausgeliefert werden.

Via-in-pad, PoP und kupfergefüllte Microvias unterstützt.

Vision + Vacuum Support sichern CpK ≥1.33.

Stencil/Paste/Profile Tuning + Vacuum Dwell.

UMFANG

Jedes Gate – DFM, Schablone, Placement, Reflow, Inspektion, Underfill, Rework – wird vom selben Team geführt, damit Yield stabil bleibt und Rework-Zyklen kontrolliert sind.

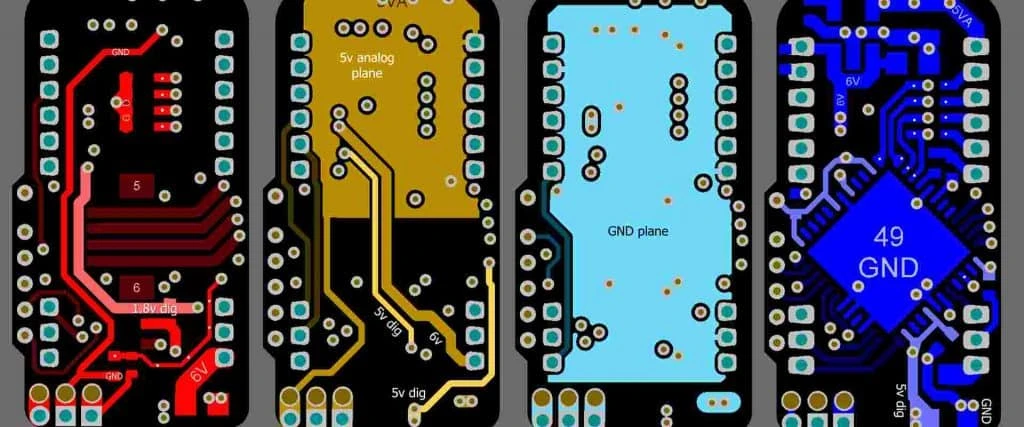

DFM & Land Pattern

Pad-Design, Mask Clearance, via-in-pad Fills und Copper-Balance-Review reduzieren Warpage.

Schablone & Paste

Area Ratio, Step-Stencil, Type 5/6 Paste und SPI-Feedback stabilisieren Deposits.

Placement & Reflow

±25 µm Placement, Vacuum Support, Stickstoff-Reflow ΔT ≤5 °C mit Thermocouples.

Inspektion & Rework

3D AOI, AXI-Sampling, Void-Reports, Underfill, Staking und Rework-Prozeduren ≤3 Zyklen.

PLAYBOOK

Definierte Gates halten High-Density BGA/QFN Builds vom Intake bis zum Rework stabil.

Package Intake

Zeichnungen, Pad-Stacks, Paste-Spezifikationen und Void-Ziele aufnehmen.

Prozess-Tuning

Stencil/Paste-Auswahl, Placement-Setup und Reflow-Simulationen.

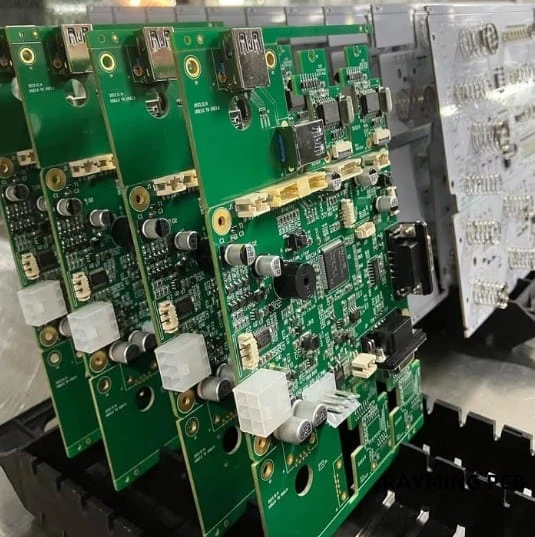

Production Run

SMT mit 100% SPI/AOI, Vacuum Support und Stickstoff-Reflow.

Inspektion & Analytik

AXI, Void-Reports, Ionics Checks und SPC-Dashboards.

Underfill & Rework

Underfill/Staking und kontrollierten Rework ≤3 Zyklen mit Post-AXI ausführen.

PORTFOLIO

Hidden-joint Builds, die wir quartalsweise fahren – mit dokumentierter Void-Control und Rework-Limits.

CAPABILITIES

Tools, Fixtures und Analytik für Hidden-Joint-Success.

Dedizierte Reflow-, AXI-, Underfill- und Rework-Labs mit Feuchtekontrolle.

QUALITÄT

Inline-Inspektion, AXI und Void-Analytik machen verdeckte Lötstellen messbar.

Area-Ratio Checks, Paste-Height SPC und Printer-Feedback-Loops.

AXI-Sampling und C-SAM/Void-Reports mit <10% BTC Zielen.

≤3 Zyklen mit Site Dressing, Paste Print und Post-AXI Verifikation.

High-Density BGAs mit Boundary-Scan, Underfill und Rework-Traceability.

Cleanliness, AOI/AXI und Rework-Logs für Class II/III Devices.

Void-/Hi-Pot-Daten und PPAP-ready Evidence für ECUs und Inverter.

Shielded RF-Module mit kontrolliertem Reflow und definierten Void Targets.

Everything you need to know about HDI PCB technology

Laden Sie Ihre Daten hoch und erhalten Sie DFM-, Prozess- und Inspektionsplan für verdeckte Lötstellen.