Advanced Engineering Guide

Die technische Realitaet der PCB-Fertigung mit hoher Lagenzahl

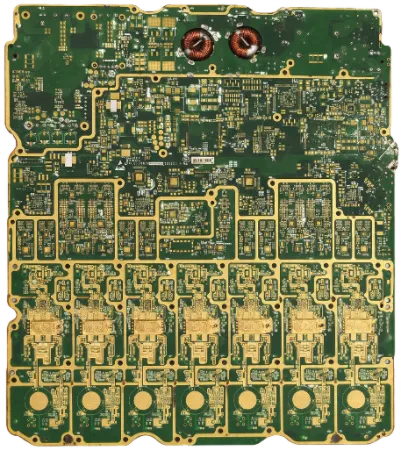

Ein 32-lagiges Backplane oder ein 24-lagiges AI-Motherboard in einer ECAD-Software zu entwerfen, ist ein komplexes Routing-Puzzle. Die Fertigung ist jedoch ein Kampf gegen Physik, Chemie und Thermodynamik. Mit steigender Lagenzahl schrumpft die Fehlertoleranz exponentiell. Bei APTPCB arbeiten wir mit erfahrenen Hardware-Ingenieuren weltweit zusammen, um diese extremen Designs aus der digitalen in die physische Welt zu ueberfuehren. Nachfolgend ein tiefer Einblick in die technischen Huerden der Fertigung mit hoher Lagenzahl und wie wir sie loesen.

1. Die Tyrannei von Registrierung und Dimensionsskalierung

Die groesste Bedrohung fuer eine Leiterplatte mit hoher Lagenzahl ist Registrierungsversagen. Eine PCB entsteht, indem abwechselnde Lagen aus vollstaendig ausgehaerteten Cores und unausgehaertetem Prepreg unter extremer Hitze und hydraulischem Druck gepresst werden. Waehren dieses Laminationsprozesses dehnen sich die Materialien aus und schrumpfen beim Aushaerten und Abkuehlen wieder. Diese Dimensionsaenderung ist anisotrop und faellt in X-Richtung (Kette) und Y-Richtung (Schuss) des Glasgewebes unterschiedlich aus.

Bei einer 4-lagigen Leiterplatte wird ein leichter Versatz noch vom Annular Ring aufgefangen, also vom Kupferring rund um ein gebohrtes Loch. Bei einer 40-lagigen Leiterplatte fuehrt uneinheitlicher Innenlagenversatz dazu, dass ein mechanischer Bohrer zwangslaeufig ausserhalb des Kupferpads auf Layer 25 austritt und so die Verbindung trennt oder einen fatalen Kurzschluss zum benachbarten Ground-Plane verursacht.

Die APTPCB-Loesung: Unsere CAM-Ingenieure wenden auf das Artwork jeder einzelnen Lage nichtlineare Skalierungsfaktoren an und sagen die Schrumpfrate mathematisch auf Basis der jeweiligen Kupferdichte voraus. Waehren des Layups nutzen wir X-Ray-Induction-Bonding-Systeme, um die Innenlagen vor dem Presszyklus physisch zueinander auszurichten und so eine Lage-zu-Lage-Registrierungsgenauigkeit von ±1.5 mil sicherzustellen.

2. Plattierung mit hohem Aspect Ratio: die Kapillar-Herausforderung

Mit zunehmender Lagenzahl wird die Leiterplatte dicker. Eine 32-lagige Leiterplatte erreicht leicht 5.0 mm (200 mil) Gesamtdicke. Muss darin ein 10-mil-Via (0.25 mm) gebohrt werden, entsteht eine mikroskopische Kapillarroehe mit einem Aspect Ratio von 20:1.

Standard-DC-Elektroplattierungssysteme verlassen sich auf Stroemungsdynamik, um kupferreiche Chemiebads durch die Loecher zu zirkulieren. In einem 20:1-Via stagniert die Fluessigkeit im Zentrum des Barrels. Kupferionen werden dort aufgebraucht, die Plattierung stoppt und das Ergebnis ist ein Via mit dickem Kupfer an der Oberflaeche, aber gefaehrlich duennen oder fehlenden Kupferbereichen in der Mitte. Waehren der extremen Hitze von SMT-Reflow oder Wave Soldering reisst die Z-Achsen-Ausdehnung der Leiterplatte dieses duenne Barrel leicht auseinander und verursacht schwer zu diagnostizierende intermittierende Unterbrechungen.

Die APTPCB-Loesung: Bei Leiterplatten ueber einem Aspect Ratio von 10:1 setzen wir Periodic Reverse Pulse Plating ein. Statt eines kontinuierlichen Gleichstroms pulst das System den Strom schnell vorwaerts und dann kurz rueckwaerts. Der Rueckwaertspuls wirkt wie eine elektrische "Pumpe", entfernt verbrauchte Chemie und zieht frische, kupferreiche Fluessigkeit tief in das Zentrum des Via. So entsteht eine gleichmaessige, dicke Kupfer-Barrel-Wand, die mehrere bleifreie Reflow-Zyklen ueberlebt.

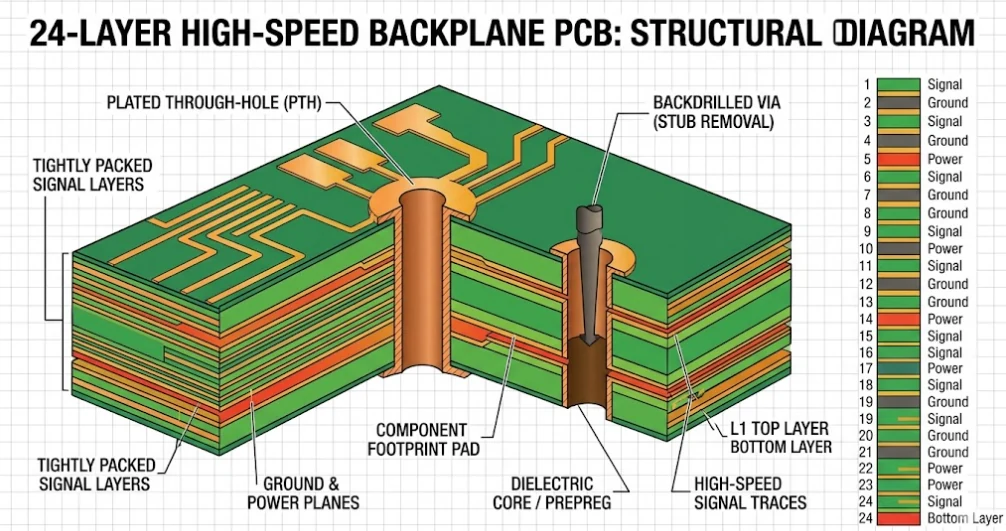

3. Signalresonanzen mit praezisem Backdrilling beseitigen

In digitalen High-Speed-Architekturen wie PCIe Gen5, 100G/400G Ethernet oder 112G PAM4 wird die physische Geometrie eines Via zu einer aktiven RF-Komponente. Man stelle sich ein Signal vor, das auf einer 24-lagigen Backplane von Layer 1 zu Layer 5 verlaeuft. Das Signal steigt bei Layer 5 aus, doch das verbleibende Via-Barrel aus Kupfer, das von Layer 6 bis Layer 24 weiterreicht, wirkt wie eine unterminierte Antenne, also ein "Via Stub". Dieser Stub reflektiert elektromagnetische Energie in den Kanal zurueck, verursacht destruktive Interferenz und schliesst das Daten-Auge.

Die APTPCB-Loesung: Um die Signalintegritaet zu retten, setzen wir Controlled-Depth Backdrilling ein. Mit fortschrittlichen CNC-Bohrmaschinen, die ueber leitfaehige Oberflaechensensorik verfuegen, fuehrt der Bohrer von der Unterseite der Leiterplatte aus, also ab Layer 24, und bohrt den unerwuenschten Kupferstub aus, waehrend er praezise stoppt, bevor er die aktive Signallage Layer 5 erreicht. Wir erzielen routinemaessig Tiefengenauigkeiten von ±50μm und lassen einen harmlosen Reststub von weniger als 8 bis 10 mil zurueck, wodurch der Kanal von destruktiven Resonanzen befreit wird.

4. Impedanzmanagement in dicken Architekturen

In einer 6-lagigen Leiterplatte benoetigt eine 50Ω-Single-Ended-Leitung vielleicht 6 mil Breite. In einer 32-lagigen Leiterplatte muss die Leiterbahnbreite proportional schrumpfen, haeufig auf 2.5 bis 3 mil, weil ultraduenne Prepregs, etwa 2 mil dick, eingesetzt werden muessen, um die Gesamtdicke noch beherrschbar zu halten, und damit der Abstand zwischen Signalleitung und Referenz-Ground-Plane drastisch sinkt.

Eine 3-mil-Leiterbahn mit ±5% Impedanz-Toleranz zu aetzen, erfordert absolute chemische Beherrschung. Die APTPCB-Loesung: Wir setzen Laser Direct Imaging (LDI) fuer Belichtungsgenauigkeit im Sub-mil-Bereich ein und kombinieren dies mit vakuumunterstuetzten Aetzlinien, die Saeure zwischen engen Leiterbahnen herausziehen, um Undercut zu verhindern. Jede Impedanzstruktur wird in Polar Si9000 modelliert und auf jedem einzelnen Fertigungspanel physisch ueber TDR-Testcoupons verifiziert.