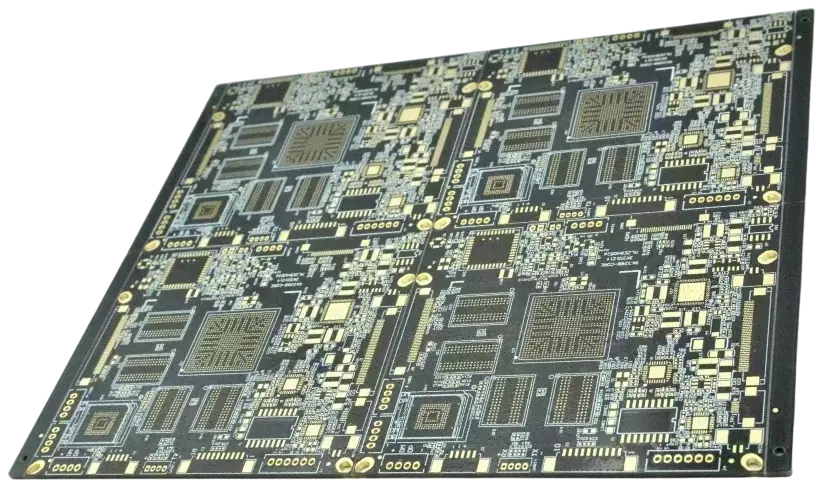

AI-Native PCB: Definition, Umfang und für wen dieser Leitfaden gedacht ist

Der Begriff AI-Native PCB bezieht sich auf Hochleistungs-Leiterplatten, die speziell für die Unterstützung von Hardware-Ökosystemen der Künstlichen Intelligenz entwickelt wurden, einschließlich Trainingsservern, Inferenzbeschleunigern und Edge-Computing-Knoten. Im Gegensatz zu Standardelektronik müssen diese Platinen gleichzeitig massive Datendurchsätze, extreme thermische Belastungen und ultra-niedrige Signallatenz bewältigen. Da die KI-Infrastruktur mit der Telekommunikation konvergiert, überschneiden sich die Anforderungen an diese Platinen oft mit denen von Hochfrequenzinfrastrukturen wie 5G AAU PCB (Aktive Antenneneinheit) und 5G ADC PCB (Analog-Digital-Wandler)-Modulen, was eine komplexe Fertigungsherausforderung darstellt, die Präzision jenseits der IPC Class 2 Standards erfordert.

Dieses Playbook richtet sich an Hardware-Ingenieure, NPI-Manager und Beschaffungsleiter, die von der Standard-Digitalelektronik auf Hochleistungsrechen-Hardware (HPC) umsteigen. Es filtert das Marketingrauschen heraus, um sich auf die physikalischen Realitäten der Fertigung zu konzentrieren: Materialauswahl, Lagenaufbau-Integrität und die spezifischen Validierungsschritte, die erforderlich sind, um Feldausfälle in teuren KI-Clustern zu verhindern. Bei APTPCB (APTPCB PCB Factory) haben wir festgestellt, dass die Hauptursache für Projektverzögerungen in diesem Sektor nicht die Designfähigkeit ist, sondern eine Diskrepanz zwischen Designabsicht und Fertigungsrealität. Dieser Leitfaden dient als Entscheidungsrahmen, um diese Lücke zu schließen und sicherzustellen, dass Ihre Spezifikationen in zuverlässige Hardware umgesetzt werden.

Wann man AI-Native PCBs verwendet (und wann ein Standardansatz besser ist)

Das Verständnis des oben definierten Umfangs ermöglicht es uns, genau zu bestimmen, wann die Kosten und die Komplexität einer AI-Native PCB gerechtfertigt sind, im Vergleich dazu, wann ein Standard-Hochgeschwindigkeitsdesign ausreicht.

Verwenden Sie einen AI-Native Ansatz, wenn:

- Signalgeschwindigkeiten 56 Gbit/s PAM4 überschreiten: Standard-FR4 kann die für moderne KI-Verbindungen erforderliche Signalintegrität ohne massive Dämpfung nicht unterstützen.

- Lagenanzahl 18 Lagen überschreitet: KI-Beschleuniger erfordern oft eine hohe Routing-Dichte und umfangreiche Leistungsebenen, die Standard-Laminierpressen ohne spezielle Werkzeuge nicht präzise ausrichten können.

- Wärmedichte kritisch ist: Wenn Ihre GPU oder TPU Wärme erzeugt, die Flüssigkeitskühlung oder Tauchkühlung erfordert, können Standard-Lötstopplack- und Substratmaterialien degradieren.

- Integration mit 5G-Infrastruktur: Designs, die die 5G AAU PCB-Technologie für Edge AI integrieren, erfordern Mixed-Signal-Fähigkeiten (HF + Digital), die hybride Lagenaufbauten erfordern.

Bleiben Sie bei Standard-Hochgeschwindigkeits-PCBs, wenn:

- IoT-Edge-Geräte: Einfache Inferenz auf Mikrocontrollern (z. B. Spracherkennung) benötigt selten exotische Materialien; Standard-FR4 mit kontrollierter Impedanz ist normalerweise ausreichend.

- Legacy-Schnittstellen: Wenn die Platine hauptsächlich PCIe Gen 3 oder niedriger verarbeitet, ist der Kostenaufschlag für KI-taugliche Materialien mit extrem geringen Verlusten unnötig.

- Nur Logik-Prototyping: Wenn Sie die Logik bei niedrigen Geschwindigkeiten validieren, bevor Sie auf volle Geschwindigkeit skalieren, können Standardmaterialien während früherer Revisionen erhebliche Kosten sparen.

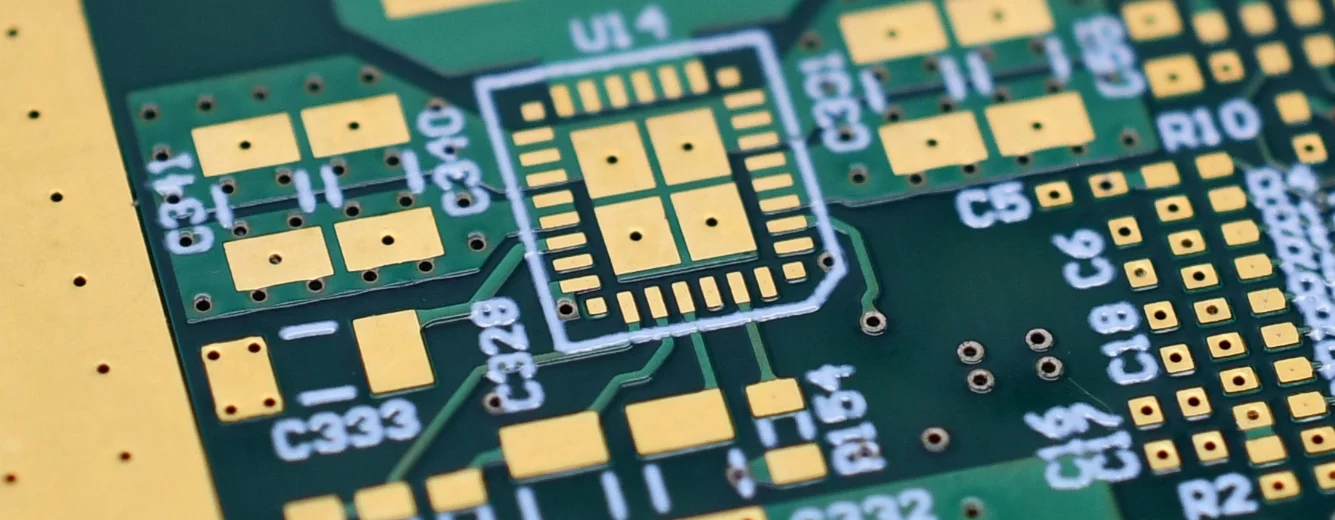

KI-native Leiterplatten-Spezifikationen (Materialien, Lagenaufbau, Toleranzen)

Sobald Sie festgestellt haben, dass Ihr Projekt eine KI-native Leiterplatte erfordert, besteht der nächste Schritt darin, die strengen Spezifikationen festzulegen, die den Herstellungsprozess steuern werden.

- Basismaterialien (Laminate):

- Anforderung: Materialien mit extrem geringen Verlusten sind nicht verhandelbar.

- Ziel: Df (Verlustfaktor) < 0,002 bei 10 GHz; Dk (Dielektrizitätskonstante) < 3,6.

- Beispiele: Panasonic Megtron 7/8, Isola Tachyon 100G oder Rogers RO3000-Serie für hybride HF-Abschnitte.

- Kupferfolienrauheit:

- Anforderung: HVLP (Hyper Very Low Profile) oder HVLP2 Kupfer.

- Ziel: Oberflächenrauheit (Rz) < 1,5 µm, um Skin-Effekt-Verluste bei hohen Frequenzen zu minimieren.

- Lagenanzahl & Lagenaufbau:

- Bereich: Typischerweise 20 bis 40+ Lagen für Server-Grade-Platinen.

- Struktur: Mehrere Laminierungszyklen (3+); erfordert oft "any-layer" HDI (High Density Interconnect) oder ELIC (Every Layer Interconnect).

- Bohren & Vias:

- Rückbohren: Obligatorisch für Hochgeschwindigkeitssignalschichten zur Entfernung von Via-Stummeln.

- Toleranz: Die Tiefentoleranz der Rückbohrung muss innerhalb von ±0,05 mm bis ±0,10 mm kontrolliert werden, um die Signalintegrität zu erhalten, ohne interne Schichten zu beschädigen.

- Aspektverhältnis: Eine hohe Aspektverhältnis-Beschichtungsfähigkeit (15:1 bis 20:1) ist für dicke Leiterplatten (3,0 mm+) erforderlich.

- Impedanzkontrolle:

- Toleranz: Strenge Kontrolle von ±5% oder ±7% (Standard ist ±10%) bei Single-Ended- und Differentialpaaren.

- Prüfung: 100% TDR (Time Domain Reflectometry) Prüfung an Coupons und Produktionsplatinen.

- Oberflächenveredelung:

- Bevorzugt: ENIG (Electroless Nickel Immersion Gold) oder ENEPIG zur Unterstützung des Drahtbondens.

- Alternative: Immersionssilber für geringere Einfügedämpfung, obwohl die Haltbarkeit kürzer ist.

- Thermische Zuverlässigkeit:

- Tg (Glasübergangstemperatur): > 180°C (Hohe Tg).

- Td (Zersetzungstemperatur): > 350°C, um mehrere Reflow-Zyklen während der Montage großer BGA-Komponenten zu überstehen.

- Registrierungsgenauigkeit:

- Ziel: Schicht-zu-Schicht-Registrierung innerhalb von ±2-3 mil (50-75µm), um sicherzustellen, dass Pads mit Vias in Hochlagenstapeln ausgerichtet sind.

- Sauberkeit:

- Ionische Verunreinigung: < 0,65µg/cm² NaCl-Äquivalent, entscheidend zur Verhinderung elektrochemischer Migration in Hochspannungs-Rechenzentrumsumgebungen.

Fertigungsrisiken von KI-nativen PCBs (Grundursachen und Prävention)

Wenn die Spezifikationen festgelegt sind, verlagert sich der Fokus auf die Minderung der spezifischen Ausfallarten, die mit der Herstellung von Hochleistungs-KI-nativen PCB-Designs verbunden sind.

- Wachstum von leitfähigen anodischen Filamenten (CAF)

- Grundursache: Hohe Spannungsdifferenz zwischen eng beieinander liegenden Vias kombiniert mit Feuchtigkeitsaufnahme im Harzsystem.

- Erkennung: CAF-Tests (1000+ Stunden bei hoher Temperatur/Luftfeuchtigkeit).

- Prävention: Verwendung von CAF-beständigen Materialien (verbreitetes Glasgewebe) und Maximierung des Via-zu-Via-Abstands, wo möglich.

- Pad-Kraterbildung

- Grundursache: Spröde Laminatmaterialien (häufig bei Hochgeschwindigkeitsmaterialien) brechen unter der mechanischen Belastung der thermischen Ausdehnung großer BGAs.

- Erkennung: Akustische Mikroskopie oder Dye-and-Pry-Tests während der Validierung.

- Prävention: Verwendung von harzverstärkten Laminaten und Eckverklebung/Underfill bei großen BGAs.

- Signalintegritätsverlust durch Ätzvariation

- Grundursache: Über- oder Unterätzung von trapezförmigen Leiterbahnen verändert das Impedanzprofil.

- Erkennung: Querschnittsanalyse und TDR-Tests.

- Prävention: Angabe von "Ätzkompensations"-Faktoren im CAM-Engineering und Verwendung von Vakuumätzgeräten.

- Delamination während des Reflow-Lötens

- Ursache: Eingeschlossene Feuchtigkeit in dicken Leiterplatten verdampft bei bleifreien Reflow-Temperaturen (260°C).

- Erkennung: SAM (Scanning Acoustic Microscopy) nach Reflow-Simulation.

- Prävention: Strenge Backprotokolle (4-8 Stunden) vor der Bestückung und feuchtigkeitsdichte Verpackung (MBB).

- Backdrill-Stummelrückstände

- Ursache: Bohrerverschleiß oder Tiefenfehlberechnung hinterlässt einen kleinen leitfähigen Stummel.

- Erkennung: Röntgeninspektion oder spezifische TDR-Analyse zur Suche nach Reflexionsanomalien.

- Prävention: Automatisierte optische Bohrerprüfungen und Röntgenverifizierung des Erstmusters.

- Verzug / Wölbung und Verdrehung

- Ursache: Asymmetrische Kupferverteilung oder unausgewogener Lagenaufbau bei großformatigen Leiterplatten.

- Erkennung: Schatten-Moiré-Messung.

- Prävention: streng ausgewogene Kupferfüllung auf allen Lagen; Verwendung von Materialien mit niedrigem WAK.

- Plattierungsfehlstellen in Vias mit hohem Aspektverhältnis

- Ursache: Die Plattierungslösung zirkuliert in tiefen, engen Löchern (z.B. 3 mm dicke Leiterplatte mit 0,2 mm Vias) nicht effektiv.

- Erkennung: Querschnittsanalyse und Thermoschockprüfung.

- Prävention: Pulsplattierungstechnologie und Designgrenzen für das Aspektverhältnis (wenn möglich unter 15:1 halten).

- Impedanzdiskontinuität an Lagenübergängen

- Ursache: Fehlausrichtung zwischen dem Via-Pad und dem Freiraum der Referenzebene.

- Erkennung: VNA (Vector Network Analyzer) Prüfung.

- Prävention: Laser-Direktbelichtung (LDI) für Innenlagen zur Sicherstellung präziser Ausrichtung.

Validierung und Abnahme von KI-nativen PCBs (Tests und Bestehenskriterien)

Um sicherzustellen, dass die oben genannten Risiken gemanagt werden, muss vor der Massenproduktion jeder KI-nativen PCB ein robuster Validierungsplan ausgeführt werden.

- Verbindungstest (IST):

- Ziel: Überprüfung der Durchkontaktierungszuverlässigkeit unter thermischen Zyklen.

- Methode: Prüfmuster wiederholt von Umgebungstemperatur auf 150°C (oder höher) zyklisch belasten.

- Akzeptanzkriterium: Kein Widerstandsanstieg > 10% nach 500 Zyklen.

- Verifizierung der Signalintegrität (S-Parameter):

- Ziel: Bestätigung, dass Einfügedämpfung und Rückflussdämpfung den Simulationsmodellen entsprechen.

- Methode: VNA-Messung bis 28GHz oder 56GHz.

- Akzeptanzkriterium: Abweichung der Einfügedämpfung < 1dB/Zoll von der Simulation; Rückflussdämpfung < -15dB.

- Hipot-Test (Hochspannungstest):

- Ziel: Sicherstellung der Isolierung zwischen Hochspannungs-Stromschienen (üblich bei der Stromversorgung von KI-Servern).

- Methode: Anlegen hoher Spannung (z.B. 500V-1000V) zwischen Netzen.

- Akzeptanzkriterium: Leckstrom < 1mA; kein Durchschlag.

- Thermoschocktest:

- Ziel: Test der Materialhaftfestigkeit und der Integrität der Durchkontaktierungsbeschichtung.

- Methode: -55°C bis +125°C Flüssig-zu-Flüssig-Transfer.

- Akzeptanzkriterium: Keine Delamination, Blasenbildung oder offene Stromkreise nach 100 Zyklen.

- Lötbarkeitstest:

- Ziel: Sicherstellen, dass die Oberflächenveredelung Lot ordnungsgemäß annimmt.

- Methode: IPC J-STD-003 (Dip and Look oder Benetzungsbalance).

- Akzeptanz: > 95% Abdeckung; Benetzungszeit < 2 Sekunden.

- Ionenverunreinigungstest (ROSE):

- Ziel: Überprüfung der Sauberkeit der Leiterplatte.

- Methode: IPC-TM-650 2.3.25.

- Akzeptanz: < 1,56 µg/cm² NaCl-Äquivalent (oft strenger für KI: < 0,65).

- Kupfer-Schälfestigkeit:

- Ziel: Überprüfung der Haftung von Kupfer am Dielektrikum.

- Methode: Mechanischer Schältest.

- Akzeptanz: > 0,8 N/mm (oder gemäß Materialdatenblatt-Spezifikation).

- Dimensionsstabilität:

- Ziel: Sicherstellen, dass die Leiterplatte in das Gehäuse passt und mit den Sockeln übereinstimmt.

- Methode: KMG (Koordinatenmessmaschine).

- Akzeptanz: Toleranzen innerhalb von ±0,1 mm für die Umrisse; Verzug < 0,75%.

Qualifizierungs-Checkliste für KI-native Leiterplattenlieferanten (Angebotsanfrage, Audit, Rückverfolgbarkeit)

Bei der Auswahl eines Partners wie APTPCB verwenden Sie diese Checkliste, um sicherzustellen, dass die Fabrik wirklich in der Lage ist, die Anforderungen für KI-native Leiterplatten zu erfüllen, anstatt nur Standardproduktionen.

Gruppe 1: RFQ-Eingaben (Was Sie bereitstellen müssen)

- Vollständige Gerber X2- oder ODB++-Dateien (bevorzugt für komplexe Daten).

- IPC-356 Netlist zur Überprüfung des elektrischen Tests.

- Detaillierte Lagenaufbauzeichnung mit Angabe von Materialtypen (Marke/Serie) und Dielektrikumsdicke.

- Impedanztabelle mit Bezug auf spezifische Lagen und Leiterbahnbreiten.

- Bohrzeichnung, die zwischen Durchkontaktierungen, Sack-/Vergrabenen Vias und Backdrills unterscheidet.

- Fertigungszeichnung mit Hinweisen zu Class 3 Anforderungen (falls zutreffend).

- Nutzenanforderungen (falls die Bestückung spezifische Schienen/Fiducials erfordert).

- Readme-Datei, die kritische Netze hervorhebt (z.B. "Leitungsführung auf Netz X nicht ändern").

Gruppe 2: Fähigkeitsnachweis (Was der Lieferant zeigen muss)

- Geräteliste: Laser Direct Imaging (LDI) Maschinen für Innenlagen.

- Geräteliste: Vakuumätzlinien (für feine Linien < 3 mil).

- Geräteliste: Automatisierte Backdrilling-Maschinen mit Tiefenkontrollsensorik.

- Erfahrung: Fallstudien oder anonymisierte Muster von Leiterplatten mit 20+ Lagen.

- Materialbestand: Nachweis des Lagerbestands oder direkter Lieferkette für Megtron/Rogers-Materialien.

- HDI-Fähigkeit: Nachgewiesene Fähigkeit für gestapelte Microvias (z.B. 3+N+3).

Gruppe 3: Qualitätssystem & Rückverfolgbarkeit

- Zertifizierungen: ISO 9001 (Allgemein), IATF 16949 (falls Automotive AI), UL 94V-0.

- Rückverfolgbarkeit: Können sie eine spezifische Leiterplatte bis zur Rohmaterialcharge und dem Laminierpresszyklus zurückverfolgen?

- IQC (Wareneingangskontrolle): Verfahren zur Überprüfung der Eigenschaften von Pre-preg und Kernmaterial.

- AOI (Automatisierte Optische Inspektion): Wird AOI auf jeder Innenlage durchgeführt?

- Querschnittsanalyse: Häufigkeit der Mikroschnittanalyse pro Produktionslos.

Gruppe 4: Änderungskontrolle & Lieferung

- PCN (Product Change Notification) Richtlinie: Verpflichtung zur Benachrichtigung vor Material- oder Unterlieferantenwechsel.

- EQ (Engineering Question) Prozess: Wie sie DFM-Diskrepanzen handhaben (formeller Bericht vs. E-Mail).

- Verpackung: Feuchtigkeitsschutzbeutel (MBB) mit Feuchtigkeitsindikatorkarten (HIC) und Trockenmittel.

- Logistik: Erfahrung im internationalen Versand von Schwerlast-/Schwergewichtssendungen (z.B. mit viel Kupfer).

So wählen Sie KI-native Leiterplatten (Kompromisse und Entscheidungsregeln)

Jede technische Entscheidung beinhaltet einen Kompromiss. Hier erfahren Sie, wie Sie die häufigsten Konflikte bei der Spezifikation von KI-nativen Leiterplatten-Architekturen bewältigen.

- Materialkosten vs. Signalintegrität

- Regel: Wenn Ihre gesamte Leiterbahnlänge kurz ist (< 5 Zoll) und die Geschwindigkeit < 25 Gbit/s beträgt, können Sie "Mid-Loss"-Material (z.B. Isola FR408HR) verwenden.

- Regel: Wenn die Leiterbahnlänge lang ist oder die Geschwindigkeit > 25 Gbit/s beträgt, müssen Sie "Ultra-Low Loss"-Material (z.B. Megtron 7) wählen. Die Signaldämpfungskosten von FR4 würden teure Neuentwicklungen erfordern.

- HDI vs. Durchkontaktierung

- Regel: Wenn Sie BGA-Komponenten mit einem Rastermaß < 0,65 mm haben, müssen Sie HDI (Microvias) verwenden.

- Regel: Wenn das BGA-Rastermaß > 0,8 mm beträgt, bleiben Sie bei Durchkontaktierungen oder einfachen Sacklöchern, um die Leiterplattenkosten um 30-50 % zu senken.

- Backdrilling vs. Sacklöcher

- Regel: Wenn Sie Stubs auf einer dicken Leiterplatte (3 mm+) entfernen müssen, ist Backdrilling im Allgemeinen kostengünstiger als sequentielle Lamination (Sacklöcher) für die einfache Stub-Entfernung.

- Regel: Wenn Sie Routing-Platz auf äußeren Lagen oberhalb des Vias benötigen, verwenden Sie Blind Vias.

- Oberflächenveredelung: ENIG vs. OSP

- Regel: Wenn Zuverlässigkeit und Haltbarkeit von größter Bedeutung sind (Server/Rechenzentrum), wählen Sie ENIG.

- Regel: Wenn Signalintegrität bei extrem hoher Frequenz (> 50GHz) die einzige Priorität ist, hat OSP (Organic Solderability Preservative) keine Nickelschicht, die magnetische Verluste verursachen könnte, aber die Montage muss sofort erfolgen.

- Leiterplattendicke vs. Aspektverhältnis

- Regel: Wenn die Leiterplatte dick sein muss (für Steifigkeit/Lagen), müssen Sie den Via-Durchmesser erhöhen, um ein Beschichtungs-Aspektverhältnis < 15:1 beizubehalten.

- Regel: Wenn die Via-Größe fest (klein) ist, müssen Sie die Leiterplattendicke reduzieren oder höhere Ausbeuteverluste/Kosten in Kauf nehmen.

KI-Native Leiterplatten FAQ (Kosten, Lieferzeit, DFM-Dateien, Materialien, Tests)

F: Wie vergleichen sich die Kosten von KI-Native Leiterplatten mit Standard-Leiterplatten? A: Rechnen Sie mit Kosten, die 3- bis 10-mal höher sind als bei Standard-FR4-Leiterplatten. Dies wird durch teure Rohmaterialien (Megtron/Rogers können das 5-fache der FR4-Kosten betragen), Prozesse mit geringer Ausbeute (HDI, Rückbohren) und umfangreiche Testanforderungen verursacht.

F: Was ist die typische Lieferzeit für KI-Native Leiterplatten-Prototypen? A: Die Standardlieferzeit beträgt 15-20 Arbeitstage aufgrund sequenzieller Laminierungszyklen.

- Beschleunigt: Kann mit Premiumgebühren auf 10-12 Tage verkürzt werden.

- Materialverzögerung: Überprüfen Sie immer den Lagerbestand für exotische Materialien; die Bestellung von Materialien kann 2-4 Wochen hinzufügen, wenn sie nicht auf Lager sind. F: Welche spezifischen DFM-Dateien werden für die KI-native PCB-Impedanzmodellierung benötigt? A: Sie müssen eine Lagenaufbau-Datei bereitstellen, die explizit die Dielektrizitätskonstante (Dk) und den Verlustfaktor (Df) bei der Betriebsfrequenz (z. B. 10 GHz) angibt, nicht nur den 1-MHz-Wert, der in allgemeinen Datenblättern zu finden ist.

F: Können wir Materialien (Hybrid-Lagenaufbau) mischen, um Kosten zu sparen? A: Ja, dies ist bei 5G AAU PCB-Designs üblich.

- Methode: Verwenden Sie teures Hochfrequenzmaterial für Signallagen und günstigeres FR4 für Strom-/Masse-/mechanische Lagen.

- Risiko: CTE-Fehlanpassung zwischen Materialien kann zu Verzug führen; erfordert eine sorgfältige technische Validierung.

F: Was sind die Abnahmekriterien für die Rückbohrtiefe? A: Der Industriestandard ist typischerweise "Darf nicht in das Kupfer der Ziellage schneiden" und "Verbleibende Stummelänge < 10 mil (0,25 mm)". Engere Toleranzen (z. B. < 6 mil) erhöhen die Kosten und das Risiko von offenen Stromkreisen.

F: Wie testen Sie die Zuverlässigkeit in 5G ADC PCB-Bereichen? A: Über den Standard-E-Test hinaus empfehlen wir spezifische Rauschpegelmessungen und passive Intermodulations-(PIM)-Messungen, wenn der ADC mit HF-Übertragungsleitungen integriert ist.

F: Warum ist "Thieving" oder Kupferausgleich für diese Leiterplatten entscheidend? A: KI-Leiterplatten sind oft groß. Eine ungleichmäßige Kupferverteilung führt während des Reflow-Lötens zu "Verbiegung und Verwindung", was BGA-Lötstellenfehler verursacht. Automatischer Kupferausgleich wird in leere Bereiche hinzugefügt, um die Spannungen auszugleichen.

F: Muss ich IPC Klasse 3 für KI-Hardware spezifizieren? A: Während IPC Klasse 2 Standard ist, spezifizieren die meisten Eigentümer von KI-Infrastrukturen „IPC Klasse 2 mit Beschichtungsanforderungen der Klasse 3“ (d.h. dickeres Kupfer in Vias), um langfristige Zuverlässigkeit ohne die vollen Kosten-/Inspektionslasten der Klasse 3 zu gewährleisten.

Ressourcen für KI-native PCBs (verwandte Seiten und Tools)

- Fertigung von Hochgeschwindigkeits-Leiterplatten: Ein tiefer Einblick in die spezifischen Fertigungstechniken für Signalintegrität > 25 Gbit/s.

- Server- & Rechenzentrums-Leiterplatten: Verstehen Sie die spezifischen Zuverlässigkeitsstandards, die für den 24/7-Betrieb erforderlich sind.

- HDI-Leiterplatten-Fähigkeiten: Erfahren Sie mehr über Microvia-Strukturen und sequentielle Laminierung, die für hochdichte KI-Chips benötigt werden.

- Impedanzrechner: Ein Tool zur Schätzung von Leiterbahnbreite und -abstand, bevor Sie Ihren endgültigen Lagenaufbau einreichen.

- Panasonic Megtron Leiterplattenmaterialien: Spezifikationen für das gängigste verlustarme Material, das in KI-Beschleunigern verwendet wird.

- DFM-Richtlinien: Wesentliche Designregeln, um sicherzustellen, dass Ihre KI-Platine in großem Maßstab herstellbar ist.

Angebot für KI-native Leiterplatten anfordern (DFM-Überprüfung + Preisgestaltung)

Bereit, vom Design zur Validierung überzugehen? Bei APTPCB bieten wir eine umfassende DFM-Überprüfung zusammen mit Ihrem Angebot an, um potenzielle Risiken für die Signalintegrität oder den Lagenaufbau zu identifizieren, bevor die Produktion beginnt.

Um ein genaues Angebot und DFM zu erhalten, bereiten Sie bitte vor:

- Gerber/ODB++-Dateien: Vollständiger Datensatz.

- Lagenaufbau & Impedanz: Gewünschte Lagenanzahl und Zielimpedanz.

- Materialspezifikation: Spezifische Laminatanforderungen (z.B. "Megtron 7 oder gleichwertig").

- Volumen: Prototypenmenge vs. Massenproduktionsziele.

Klicken Sie hier, um ein Angebot & eine DFM-Überprüfung anzufordern

Fazit: Nächste Schritte für AI-Native PCBs

Der erfolgreiche Einsatz einer AI-Native PCB erfordert einen Mentalitätswandel vom "Verbinden von Komponenten" zum "Entwerfen eines Übertragungsleitungssystems". Indem Sie Ihre Materialspezifikationen streng definieren, die Risiken des Aufbaus mit vielen Lagen verstehen und die Fähigkeit Ihres Lieferanten zur Handhabung von Backdrilling und HDI validieren, können Sie die Hardware-Grundlage sichern, auf die Ihre KI-Algorithmen angewiesen sind. Ob Sie eine 5G AAU PCB oder einen massiven Trainingscluster bauen, die Physik der Fertigung bleibt der ultimative Torwächter für die Leistung.