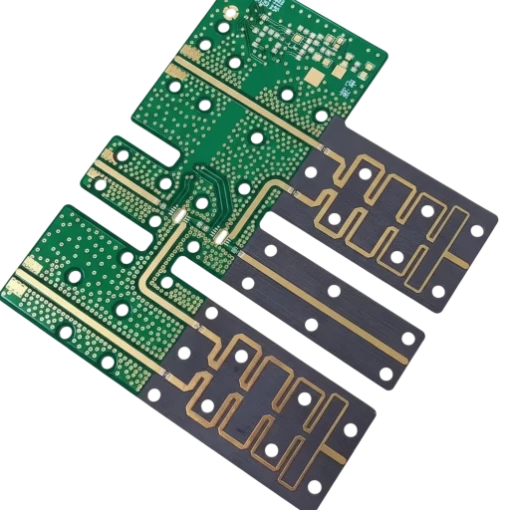

Elektronische Kriegsführung und sichere Kommunikation erfordern Hardware, die absichtlicher Störung standhält. Eine Anti-Jamming-Leiterplatte ist nicht nur eine Standardplatine; sie ist eine präzisionsgefertigte Komponente, die entwickelt wurde, um elektromagnetische Interferenzen (EMI) zu unterdrücken, die Signalintegrität unter Belastung aufrechtzuerhalten und fortschrittliche Filteralgorithmen zu unterstützen. Ingenieure, die für Verteidigungs-, Luft- und Raumfahrt- oder Hochsicherheits-Industriesektoren entwickeln, müssen strenge Layout- und Materialprotokolle einhalten, um Widerstandsfähigkeit zu gewährleisten. APTPCB (APTPCB Leiterplattenfabrik) ist spezialisiert auf die Herstellung dieser hochzuverlässigen Platinen und stellt sicher, dass theoretische Anti-Jamming-Fähigkeiten in physische Leistung umgesetzt werden.

Anti-Jamming-Leiterplatte: Kurzantwort (30 Sekunden)

Die Entwicklung einer robusten Anti-Jamming-Leiterplatte erfordert die Konzentration auf Signalisolierung und Materialstabilität.

- Materialauswahl: Verwenden Sie verlustarme Laminate (Rogers, Taconic oder Isola) mit einer stabilen Dielektrizitätskonstante (Dk) über weite Frequenzbereiche, um Signalphasenverschiebungen zu verhindern.

- Massekonzept: Implementieren Sie eine durchgehende Massereferenzebene für jede Signalschicht. Verwenden Sie "Via Stitching" entlang der Platinenkanten und kritischer Leiterbahnen, um Faradaysche Käfige zu erzeugen.

- Impedanzkontrolle: Halten Sie strenge Impedanztoleranzen (typischerweise ±5% oder ±7%) ein, um Signalreflexionen zu minimieren, die Störsender ausnutzen können.

- Isolation: Trennen Sie analoge (HF) Bereiche physisch von der digitalen Logik, um zu verhindern, dass internes Rauschen die Störschwelle senkt.

- Abschirmung: Integrieren Sie Footprints für Abschirmgehäuse auf Platinenebene oder verwenden Sie eingebettete Kapazitätsmaterialien, um hochfrequentes Rauschen zu dämpfen.

- Validierung: Überprüfen Sie die Leistung mittels Zeitbereichsreflektometrie (TDR) und Vektornetzwerkanalysator (VNA)-Tests während der Prototypenphase.

Wann Anti-Jamming-Leiterplatten angewendet werden (und wann nicht)

Das Verständnis der Betriebsumgebung ist entscheidend, bevor man sich den höheren Kosten einer störfesten Leiterplatte verschreibt.

Wann Anti-Jamming-Leiterplatten zu verwenden sind:

- AESA-Radarsysteme: Aktiv elektronisch gesteuerte Phased-Array-Radare erfordern präzise Phasensteuerung und Isolation zwischen Tausenden von Sende-/Empfangsmodulen.

- GNSS/GPS-Empfänger: Navigationssysteme für Militär und kritische Infrastruktur, die Spoofing- und Störsignale abweisen müssen.

- Sichere taktische Funkgeräte: Kommunikationsgeräte, die in umkämpften elektromagnetischen Umgebungen betrieben werden.

- Hochspannungsumspannwerke: Steuerplatinen, die zuverlässig in der Nähe massiver Schaltrauschquellen funktionieren müssen.

- Autonome Drohnenabwehr: UAVs, die kompromisslose Steuerverbindungen in feindlichen Gebieten benötigen.

Wann Standard-Leiterplatten ausreichen:

- Unterhaltungselektronik: Haushaltsgeräte und Spielzeug sind keinen absichtlichen Störbedrohungen ausgesetzt.

- Digitale Logik mit niedriger Geschwindigkeit: Einfache Mikrocontroller, die unter 50 MHz arbeiten, benötigen typischerweise keine exotischen Anti-Jamming-Materialien.

- Indoor-IoT-Sensoren: Geräte in kontrollierten Wi-Fi-Umgebungen genügen in der Regel mit Standard-FR4 und grundlegenden EMI-Praktiken.

- Allgemeine Industriesteuerungen: Sofern sie nicht direkt neben Hochleistungs-Frequenzumrichtern (VFDs) oder Lichtbogenschweißgeräten platziert werden, sind Standard-Industrieplatinen der IPC Klasse 2 ausreichend.

Regeln und Spezifikationen für Anti-Jamming-Leiterplatten (Schlüsselparameter und Grenzwerte)

Um eine hohe Störungsunterdrückung zu erreichen, muss der Herstellungsprozess strenge Toleranzen einhalten. Die folgende Tabelle zeigt kritische Spezifikationen für eine effektive Anti-Jamming-Leiterplatte.

| Regel | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Wenn ignoriert |

|---|---|---|---|---|

| Dielektrizitätskonstante (Dk) | 3,0 – 3,5 (Stabil ±0,05) | Bestimmt die Signalausbreitungsgeschwindigkeit; Variationen verursachen Phasenfehler. | Materialdatenblatt & TDR-Test. | Phasenfehlanpassung verschlechtert die Genauigkeit der Strahlformung. |

| Verlustfaktor (Df) | < 0,002 @ 10 GHz | Minimiert die Signaldämpfung und schützt schwache Signale vor Rauschen. | VNA-Einfügedämpfungsmessung. | Signalverlust reduziert die effektive Reichweite und Empfindlichkeit. |

| Leiterbahnbreitentoleranz | ±0,5 mil (±12 µm) | Beeinflusst direkt die Impedanzkontrolle. | Querschnittsanalyse (Mikroschliff). | Impedanzfehlanpassung verursacht Reflexionen (VSWR). |

| Via-Stitching-Abstand | < λ/20 der höchsten Frequenz | Erzeugt einen effektiven Faradayschen Käfig, um seitliche EMI zu blockieren. | Sichtprüfung & Gerber-Überprüfung. | HF-Leckage ermöglicht das Eindringen von Störsignalen. |

| Kupferrauheit | VLP oder HVLP (< 2 µm) | Reduziert Skin-Effekt-Verluste bei hohen Frequenzen. | SEM (Rasterelektronenmikroskop). | Erhöhte Einfügedämpfung bei mmWave-Frequenzen. |

| Lagenregistrierung | ±3 mil (±75 µm) | Gewährleistet die vertikale Ausrichtung von gekoppelten Strukturen und Masseverbindungen. | Röntgeninspektion. | Fehlausrichtung ruiniert Breitseitenkopplung und Impedanz. |

| Masseflächenkontinuität | 100% durchgehend (keine Unterbrechungen) | Bietet einen Rückweg mit geringer Induktivität. | AOI (Automatische Optische Inspektion). | Masseschleifen und hohe EMI-Anfälligkeit. |

| Wand des durchkontaktierten Lochs (PTH) | > 25 µm Kupfer | Gewährleistet eine robuste Masseverbindung und thermische Zuverlässigkeit. | Mikroschnittanalyse. | Via-Rissbildung unter thermischer Belastung; intermittierende Masseverbindung. |

| Lötstopplacksteg | > 3 mil (0,075 mm) | Verhindert Lötbrücken zwischen Fine-Pitch-Pads. | Visuell / AOI. | Kurzschlüsse bei hochdichten HF-Komponenten. |

| Oberflächenveredelung | ENIG oder Immersion Silver | Bietet eine flache Oberfläche für Fine-Pitch-Komponenten und Skin-Effekt-Leitfähigkeit. | Röntgenfluoreszenz (XRF). | Signalverlust oder schlechte Lötstellen bei BGA/QFN. |

Implementierungsschritte für Anti-Jamming-PCBs (Prozess-Checkpoints)

Der Bau einer Anti-Jamming-PCB erfordert spezifische Maßnahmen in jeder Phase des Design- und Fertigungs-Workflows.

- Frequenz- und Bedrohungsprofil definieren:

- Aktion: Identifizieren Sie den Betriebsfrequenzbereich (z.B. L-Band, X-Band) und die erwarteten Störsenderleistungspegel.

- Überprüfen: Bestätigen Sie, ob das Design Hochfrequenz-Leiterplattenmaterialien oder Hybrid-Lagenaufbauten erfordert.

- Substratmaterial auswählen:

- Aktion: Wählen Sie Materialien wie Rogers RO4350B oder RO3003 für HF-Schichten, möglicherweise verbunden mit FR4 für digitale Schichten, um Kosten zu sparen.

- Überprüfen: Überprüfen Sie die WAK (Wärmeausdehnungskoeffizient)-Kompatibilität zwischen Hybridmaterialien.

- Lagenaufbau entwerfen:

- Aktion: Konfigurieren Sie einen symmetrischen Lagenaufbau mit Masseebenen, die unmittelbar an Hochgeschwindigkeitssignalschichten angrenzen.

- Überprüfen: Verwenden Sie einen Leiterplatten-Lagenaufbau-Rechner, um die Impedanzziele zu bestätigen.

- Kritische Leiterbahnen layouten (3W-Regel):

- Aktion: Routen Sie HF-Leiterbahnen mit einem Abstand von mindestens dem 3-fachen der Leiterbahnbreite (3W), um Übersprechen zu minimieren.

- Überprüfen: Führen Sie eine DRC (Design Rule Check) speziell für den Leiterbahn-zu-Leiterbahn-Abstand durch.

- Via Stitching implementieren:

- Aktion: Platzieren Sie Masse-Vias entlang des Umfangs der Platine und um empfindliche HF-Blöcke (Schutzringe).

- Überprüfen: Stellen Sie sicher, dass das Via-Raster eng genug ist, um die Ziellänge zu blockieren.

- Rückwege optimieren:

- Aktion: Stellen Sie sicher, dass keine Leiterbahnen Spalten in der Referenzmasseebene kreuzen.

- Überprüfen: Visuelle Überprüfung von Schicht 2 und Schicht 3 (oder benachbarten Referenzschichten).

- Abschirmungs-Footprints hinzufügen:

- Aktion: Landeflächen für Metallabschirmungsgehäuse über empfindlichen Oszillatoren und Frontend-Modulen entwerfen.

- Prüfung: Mechanischen Freiraum für die Abschirmung in der 3D-Ansicht überprüfen.

- Generierung von Fertigungsdaten:

- Aktion: ODB++- oder Gerber X2-Dateien exportieren, die Impedanztabellen und Materialspezifikationen enthalten.

- Prüfung: Eine "Read Me"-Datei beifügen, die "Anti-Jamming-Anforderungen" und gegebenenfalls IPC Klasse 3 spezifiziert.

Fehlerbehebung bei Anti-Jamming-Leiterplatten (Fehlermodi und Korrekturen)

Selbst bei robusten Designs können Probleme auftreten. Hier erfahren Sie, wie Sie häufige Fehler bei der Implementierung von Anti-Jamming-Leiterplatten diagnostizieren können.

- Symptom: Hohe Bitfehlerrate (BER) unter Last.

- Ursache: Die Stromversorgungsunterdrückung (PSRR) ist zu niedrig; Rauschen von den Stromschienen koppelt in die HF-Leitungen ein.

- Prüfung: Stromschienen auf Restwelligkeit prüfen; Platzierung der Entkopplungskondensatoren überprüfen.

- Behebung: Ferritperlen und Kondensatoren mit niedrigem ESR nahe den aktiven Pins hinzufügen; die Kapazität der Leistungsebene erhöhen.

- Symptom: Signalverschiebung oder Verlust der Synchronisation.

- Ursache: Thermische Instabilität des Dielektrikums (hoher Tcdk).

- Prüfung: Betriebstemperatur im Vergleich zu den Materialspezifikationen überprüfen.

- Behebung: Wechsel zu einem thermisch stabilen Material wie der Rogers RO4000-Serie; Verbesserung des Wärmemanagements (Kühlkörper).

- Symptom: Unerwartete Störemissionen.

- Ursache: Resonanzhohlräume, die zwischen Masseebenen aufgrund unzureichender Via-Stitching entstehen.

- Prüfung: Nahfeldsonden-Scan zur Lokalisierung von Hot Spots.

- Behebung: Hinzufügen von "randomisierten" Stitching-Vias, um Resonanzmoden aufzubrechen.

- Symptom: Schlechte Isolation zwischen Kanälen (Übersprechen).

- Ursache: Parallele Leiterbahnführungen sind zu lang oder zu nah beieinander.

- Prüfung: Überprüfung des Layouts auf Verstöße gegen die 3W-Regel.

- Behebung: Trennen der Leiterbahnen mit einer Masse-Schutzleiterbahn; Verwendung von differentieller Signalübertragung, wo möglich.

- Symptom: Impedanzfehlanpassung (Hoher VSWR).

- Ursache: Überätzen während der Fertigung, wodurch die Leiterbahnbreite reduziert wird.

- Prüfung: TDR-Messung und Querschnittsanalyse.

- Behebung: Anpassung der Leiterbahnbreitenkompensation in CAM-Dateien; Verschärfung der Ätztoleranz in der Fabrik.

- Symptom: Delamination unter thermischer Belastung.

- Ursache: Nicht übereinstimmende CTE in Hybrid-Lagenaufbauten (z.B. PTFE vs. FR4).

- Prüfung: Ergebnisse des Thermoschocktests.

- Behebung: Verwendung von Prepregs mit hohem Tg, die mit dem HF-Kern kompatibel sind; Anpassung der Laminierungszyklusparameter.

Wie man Anti-Jamming-Leiterplatten auswählt (Designentscheidungen und Kompromisse)

Die Auswahl der richtigen Konfiguration für eine Anti-Jamming-Leiterplatte erfordert eine Abwägung zwischen Leistung, Kosten und Herstellbarkeit.

1. Hybrid- vs. reine HF-Lagenaufbau

- Hybrid: Verwendet teures HF-Material nur auf den oberen/unteren Schichten und Standard-FR4 für den Kern.

- Vorteile: Geringere Kosten, ausreichend für viele L-Band-/S-Band-Anwendungen.

- Nachteile: Komplexer Laminierungsprozess; potenzielle Verzugsprobleme.

- Reine HF: Verwendet durchgehend einheitliches Hochfrequenzmaterial.

- Vorteile: Beste elektrische Leistung, konsistenter CTE.

- Nachteile: Deutlich höhere Materialkosten.

2. Auswahl der Oberflächenveredelung

- ENIG (Chemisch Nickel/Immersionsgold): Gute Lagerfähigkeit und ebene Oberfläche. Nickel ist jedoch magnetisch und kann passive Intermodulation (PIM) in empfindlichen HF-Schaltungen verursachen.

- Immersionssilber: Ausgezeichnete Leitfähigkeit und nicht magnetisch. Am besten für Hochfrequenz-Anti-Jamming geeignet, aber läuft leicht an, wenn es nicht richtig gehandhabt wird.

- OSP: Geringste Kosten, gut für HF, aber kurze Lagerfähigkeit.

3. Abschirmung: Gehäuse vs. Eingebettet

- Metallgehäuse: Traditionell, effektiv und nachbearbeitbar. Erhöht Gewicht und Höhe.

- Eingebettete/Hohlraumabschirmung: Fräsen von Hohlräumen in die Leiterplatte zur Aufnahme von Komponenten, dann Beschichten. Reduziert das Profil, erhöht aber die Herstellungskosten und Komplexität.

4. Via-Technologie

- Durchkontaktierte Vias: Am günstigsten, erzeugen aber Stummel, die bei hohen Frequenzen als Antennen wirken.

- Rückgebohrte Vias: Entfernt den ungenutzten Stummelabschnitt. Wesentlich für Signale > 5 Gbit/s oder > 3 GHz zur Aufrechterhaltung der Signalintegrität.

Anti-Jamming PCB FAQ (Kosten, Lieferzeit, häufige Defekte, Abnahmekriterien, DFM-Dateien)

F: Wie viel kostet eine Anti-Jamming-Leiterplatte im Vergleich zu einer Standard-Leiterplatte? A: Rechnen Sie mit Kosten, die 3- bis 10-mal höher sind als bei Standard-FR4-Leiterplatten. Der Preistreiber sind das spezialisierte Laminat (z.B. Rogers PCB Materialien), engere Toleranzanforderungen (Impedanzkontrolle) und oft die Notwendigkeit hybrider Laminierungszyklen.

F: Was ist die typische Lieferzeit für die Herstellung dieser Leiterplatten? A: Die Standardlieferzeit beträgt 10–15 Arbeitstage. Wenn spezialisierte Materialien (wie bestimmte Rogers- oder Taconic-Kerne) nicht auf Lager sind, kann sich die Lieferzeit auf 3–4 Wochen verlängern. APTPCB lagert gängige Hochfrequenzmaterialien, um diesen Prozess zu beschleunigen.

F: Was sind die Abnahmekriterien für Anti-Jamming-Leiterplatten? A: Die Abnahme basiert in der Regel auf den IPC-6012 Klasse 3 Standards. Zu den Hauptkriterien gehören die TDR-Impedanzprüfung (bestanden/nicht bestanden basierend auf Toleranz), saubere Querschnitte ohne Delamination und das Bestehen von ionischen Kontaminationstests zur Vermeidung von Leckströmen.

F: Kann ich Standard-FR4 für ein Anti-Jamming-Design verwenden? A: Im Allgemeinen nein. FR4 hat einen hohen Verlustfaktor (Df) und eine instabile Dielektrizitätskonstante (Dk) bei hohen Frequenzen, was die Signalintegrität beeinträchtigt. FR4 kann jedoch in hybriden Lagenaufbauten für unkritische digitale Schichten verwendet werden.

F: Welche Dateien sind für eine DFM-Überprüfung einer Anti-Jamming-Leiterplatte erforderlich? A: Sie müssen Gerber-Dateien (oder ODB++), eine detaillierte Lagenaufbauzeichnung mit Angabe der Materialtypen und Lagenreihenfolge, eine IPC-Netzliste zur Überprüfung des elektrischen Tests und gegebenenfalls eine Bohrzechnung zur Identifizierung von Back-Drill-Positionen bereitstellen.

F: Wie unterscheidet sich eine AESA-Radar-Leiterplatte von einer Standard-Anti-Jamming-Leiterplatte? A: Eine AESA-Radar-Leiterplatte ist eine Untergruppe von Anti-Jamming-Leiterplatten, die eine extreme Phasenanpassung zwischen den Kanälen erfordert. Sie umfasst oft Hunderte von Schichten komplexer Strahlformungsnetzwerke und erfordert engste Ätztoleranzen, um sicherzustellen, dass alle Antennenelemente in perfekter Phase strahlen.

F: Was ist der häufigste Defekt bei störungsresistenten Leiterplatten? A: Der häufigste Defekt ist die "Impedanzdiskontinuität". Diese tritt auf, wenn die Leiterbahnbreiten während des Ätzens variieren oder wenn Referenzebenen unterbrochen werden, was Signalreflexionen verursacht, die die Fähigkeit des Systems, Störrauschen herauszufiltern, verringern.

F: Bietet APTPCB Tests für die Anti-Jamming-Leistung an? A: Wir führen elektrische Tests auf Platinenebene (Unterbrechung/Kurzschluss) und Impedanztests (TDR) durch. Funktionale Anti-Jamming-Tests (Simulation von Störungen) werden typischerweise vom Kunden auf Systemmontageebene durchgeführt, da sie proprietäre Software und Hardware erfordern.

F: Wie helfen vergrabene Kondensatoren bei Anti-Jamming-Designs? A: Vergrabene Kapazitätsschichten (unter Verwendung sehr dünner Dielektrika zwischen Strom und Masse) bieten eine hervorragende Hochfrequenzentkopplung. Dies senkt die Impedanz des Stromverteilungsnetzes (PDN) und reduziert Rauschen, das andernfalls den Empfänger desensibilisieren könnte.

F: Welchen Einfluss hat die Oberflächenrauheit auf diese PCBs? A: Bei Frequenzen über 10 GHz fließt der Strom hauptsächlich entlang der „Haut“ des Leiters. Raues Kupfer erhöht die Pfadlänge, was zu höheren Einfügedämpfungen führt. Wir empfehlen VLP (Very Low Profile) Kupfer für alle Hochfrequenz-Anti-Jamming-Designs.

Ressourcen für Anti-Jamming-PCBs (verwandte Seiten und Tools)

Um Ihr Design weiter zu optimieren, konsultieren Sie diese spezifischen Ressourcen:

- Industrieanwendung: Leiterplatten für Luft- und Raumfahrt & Verteidigung – Standards und Anforderungen für militärische Platinen.

- Materialdaten: Rogers PCB-Materialien – Spezifikationen für die gängigsten Anti-Jamming-Substrate.

- Design-Leitfaden: Hochfrequenz-Leiterplatten – Allgemeine Regeln für HF- und Mikrowellenschaltungen.

- Lagenaufbauplanung: Leiterplatten-Lagenaufbau – So ordnen Sie Schichten für optimale Signalintegrität an.

Anti-Jamming-PCB-Glossar (Schlüsselbegriffe)

| Begriff | Definition | Relevanz für Anti-Jamming |

|---|---|---|

| EMI (Elektromagnetische Interferenz) | Störung, die von einer externen Quelle erzeugt wird und einen elektrischen Schaltkreis beeinflusst. | Die primäre Bedrohung, der eine Anti-Jamming-Leiterplatte widerstehen soll. |

| Impedanzkontrolle | Aufrechterhaltung eines spezifischen Widerstands gegenüber Wechselstromsignalen (z.B. 50Ω) entlang einer Leiterbahn. | Verhindert Signalreflexionen, die Störsender ausnutzen können, um die Leistung zu beeinträchtigen. |

| Faradayscher Käfig | Eine Umhüllung aus leitfähigem Material (oder Vias), um elektromagnetische Felder zu blockieren. | Wird auf Leiterplatten mittels Stitching-Vias verwendet, um empfindliche HF-Abschnitte zu isolieren. |

| Dk (Dielektrizitätskonstante) | Ein Maß für die Fähigkeit eines Materials, elektrische Energie in einem elektrischen Feld zu speichern. | Die Stabilität von Dk ist entscheidend für die Aufrechterhaltung der Phasenrichtigkeit in Radarsystemen. |

| Df (Verlustfaktor) | Ein Maß für die Verlustrate der Leistung in einem dielektrischen Material. | Materialien mit niedrigem Df sind erforderlich, um schwache Signale in Störumgebungen zu erhalten. |

| Übersprechen | Unerwünschte Signalübertragung zwischen Kommunikationskanälen. | Muss minimiert werden, um zu verhindern, dass internes Rauschen die Störschwelle senkt. |

| Back-drilling (Rückbohren) | Entfernen des ungenutzten Teils eines durchkontaktierten Lochs (Stumpf). | Eliminiert Signalreflexionen in Hochgeschwindigkeits-/Hochfrequenzverbindungen. |

| Hybrid-Lagenaufbau | Ein Leiterplatten-Lagenaufbau, der verschiedene Materialien (z.B. Rogers + FR4) verwendet. | Gleicht Kosten und Leistung für komplexe Anti-Jamming-Systeme aus. |

| Skin-Effekt | Die Tendenz von Hochfrequenzstrom, nahe der Oberfläche eines Leiters zu fließen. | Erfordert glatte Kupferprofile, um Verluste zu minimieren. |

| TDR (Zeitbereichsreflektometrie) | Eine Messtechnik zur Bestimmung der Impedanz von Leiterbahnspuren. | Die Standardmethode zur Überprüfung der Fertigungsqualität von HF-Leiterplatten. |

Angebot für Anti-Jamming-Leiterplatten anfordern (DFM-Überprüfung + Preisgestaltung)

Bereit, vom Design zum Prototyp überzugehen? APTPCB bietet umfassende DFM-Überprüfungen, um sicherzustellen, dass Ihre Anti-Jamming-Leiterplatte alle Impedanz- und Materialspezifikationen erfüllt, bevor die Produktion beginnt.

Für das genaueste Angebot geben Sie bitte an:

- Gerber-Dateien: RS-274X- oder ODB++-Format.

- Fertigungszeichnung: Fügen Sie Stapeldetails, Materialanforderungen (z. B. Rogers 4350B) und Impedanztabellen bei.

- Menge & Lieferzeit: Prototypen- oder Massenproduktionsvolumen.

- Sonderanforderungen: Rückbohren, Klasse-3-Inspektion oder spezifische Oberflächenveredelungen.

Fazit: Nächste Schritte für Anti-Jamming-Leiterplatten

Die erfolgreiche Implementierung einer Anti-Jamming-Leiterplatte erfordert eine Synergie zwischen fortschrittlichen Designtechniken und Präzisionsfertigung. Durch die strikte Kontrolle von Materialeigenschaften, Impedanz und Abschirmung können Ingenieure Systeme bauen, die ihre Integrität selbst in den feindlichsten elektromagnetischen Umgebungen bewahren. Ob für AESA-Radar oder sichere Kommunikation, die Wahl des Herstellers ist ebenso entscheidend wie das Design selbst. Stellen Sie sicher, dass Ihr Partner die Fähigkeit besitzt, hybride Lagenaufbauten und HF-Anforderungen mit engen Toleranzen zu handhaben, um den Missionserfolg zu gewährleisten.