Automotive Ethernet PCB-Layout: Definition, Umfang und an wen sich dieser Leitfaden richtet

Automotive Ethernet hat sich schnell zum Rückgrat moderner Fahrzeugarchitekturen entwickelt und ersetzt ältere Protokolle wie CAN und LIN für Anwendungen mit hoher Bandbreite wie ADAS, Infotainment und autonome Fahrsysteme. Im Gegensatz zu Standard-Office-Ethernet konzentriert sich das Automotive Ethernet PCB-Layout auf Single-Pair Ethernet (SPE)-Standards wie 100BASE-T1 und 1000BASE-T1, die Daten über ungeschirmte verdrillte Paare (UTP) übertragen, um Gewicht und Verkabelungskosten zu reduzieren. Diese Umstellung stellt eine enorme Belastung für das Design der Leiterplatte (PCB) dar, um die Signalintegrität in einer lauten, rauen Automobilumgebung aufrechtzuerhalten.

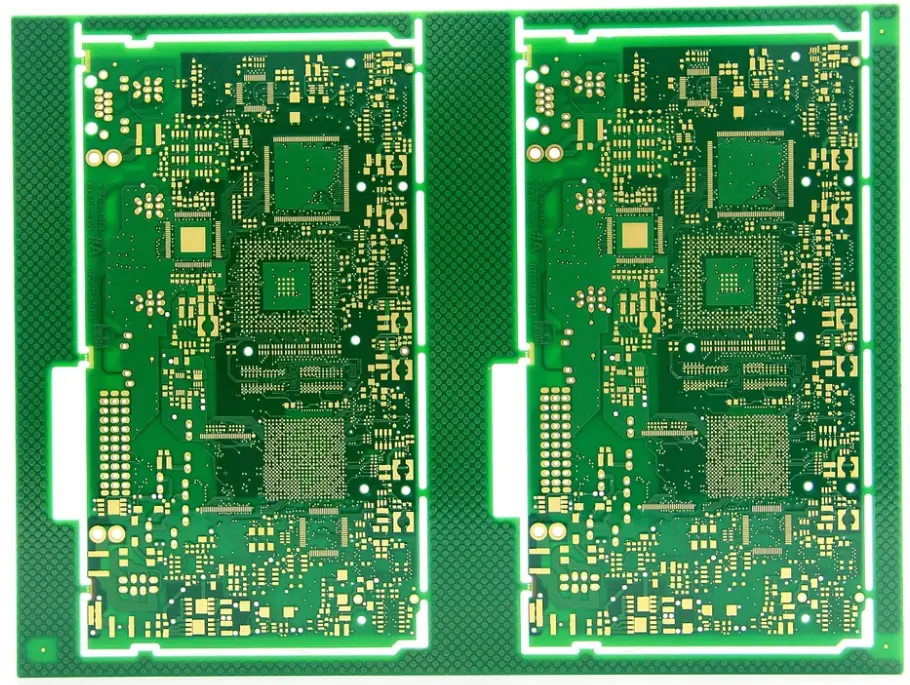

Dieser Leitfaden richtet sich an technische Leiter, PCB-Designer und Einkaufsmanager, die den Übergang vom Konzept zur Massenproduktion ohne Kompromisse bei der Zuverlässigkeit bewältigen müssen. Er geht über die grundlegende Theorie hinaus und bietet umsetzbare Spezifikationen, Strategien zur Risikominderung und Validierungsprotokolle. Ob Sie einen Zonen-Controller oder ein Hochgeschwindigkeits-Kameramodul entwerfen, die Layout-Entscheidungen, die Sie heute treffen, bestimmen die elektromagnetische Verträglichkeit (EMV) und die funktionale Sicherheit des Endprodukts. Bei APTPCB (APTPCB Leiterplattenfabrik) stellen wir fest, dass viele Designs nicht wegen des Chipsatzes scheitern, sondern weil das physische Layout die strengen Anforderungen an Impedanz und Störfestigkeit von Automobilstandards nicht berücksichtigt hat. Dieses Playbook dient Ihnen als Fahrplan, um diese Herausforderungen zu meistern und sicherzustellen, dass Ihre Dokumentation robust genug für die Fertigung ist und Ihre Lieferanten qualifiziert sind, Ihre Vision umzusetzen.

Wann Automotive Ethernet PCB-Layout verwendet werden sollte (und wann ein Standardansatz besser ist)

Das Verständnis des oben definierten Umfangs hilft zu klären, wann genau spezialisierte Layout-Techniken gegenüber Standard-Routing-Methoden eingesetzt werden sollten.

Während traditionelle Protokolle wie CAN, LIN oder FlexRay für langsame Steuersignale (Fenster, Sitze, Basissensoren) ausreichen, können sie die Gigabit-Datenraten, die von LIDAR, 4K-Kameras oder Domänencontrollern benötigt werden, nicht verarbeiten. Automotive Ethernet PCB-Layout ist zwingend erforderlich, wenn Ihr System eine Bandbreite von mehr als 10 Mbit/s benötigt und gleichzeitig eine leichtere Verkabelung als geschirmte LVDS- oder Koaxiallösungen erfordert. Es ist die spezifische Wahl für die Vollduplex-Kommunikation über ein einziges Adernpaar, bei der die Gewichtsreduzierung Priorität hat. Ein Standard-Leiterplattenlayout-Ansatz ist jedoch besser, wenn Ihre Anwendung rein niederfrequent ist oder wenn Sie Standard-RJ45-Ethernet für Diagnoseanschlüsse (OBD) verwenden, die nicht denselben Gewichtsbeschränkungen oder kontinuierlichen Vibrationsproblemen ausgesetzt sind wie interne Fahrzeugnetzwerke. Wenn die Schnittstelle lediglich für die End-of-Line-Programmierung in einer kontrollierten Fabrikumgebung dient, könnten die strengen Anforderungen des 1000BASE-T1-Layouts – wie strikte Moduskonvertierungsgrenzen und spezielle Materialauswahl – überdimensioniert sein.

Verwenden Sie spezielle Automotive-Ethernet-Layoutregeln, wenn:

- Bandbreite kritisch ist: Sie Daten von 100 Mbit/s bis 10 Gbit/s übertragen.

- Gewicht eine Einschränkung ist: Sie ungeschirmte Twisted-Pair-Kabel (UTP) verwenden.

- EMI ein Problem darstellt: Das System in der Nähe von Hochleistungsumrichtern oder Motoren betrieben wird.

- Zuverlässigkeit nicht verhandelbar ist: Die Verbindung sicherheitskritische ADAS-Funktionen unterstützt.

Automotive-Ethernet-Leiterplattenlayout-Spezifikationen (Materialien, Lagenaufbau, Toleranzen)

Sobald Sie festgestellt haben, dass Ihr Design Hochgeschwindigkeits-Automotive-Protokolle erfordert, besteht der nächste Schritt darin, die strengen Spezifikationen festzulegen, die den Herstellungsprozess steuern werden.

Um die Signalintegrität und Herstellbarkeit zu gewährleisten, müssen Sie die folgenden Parameter explizit in Ihren Fertigungsnotizen definieren. Vage Anfragen wie „Impedanzkontrolle erforderlich“ sind für das Automotive-Ethernet-Leiterplattenlayout unzureichend.

- Differenzielle Impedanz:

- Ziel: 100 Ohm ± 10 % (oder ± 5 % für Anwendungen mit 10 Gbit/s und mehr).

- Kontext: Dies gleicht die charakteristische Impedanz der UTP-Verkabelung an, um Reflexionen zu minimieren.

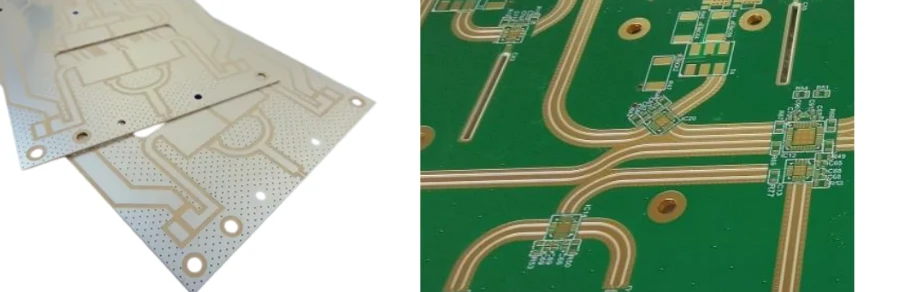

- Dielektrische Materialien (Dk/Df):

- Anforderung: Verwenden Sie Materialien mit stabiler Dielektrizitätskonstante (Dk) und niedrigem Verlustfaktor (Df) über weite Frequenzbereiche.

- Bereich: Df < 0,010 bei 1 GHz für 1000BASE-T1; Df < 0,005 für Multi-Gig.

- Beispiele: Hoch-Tg FR4 (Isola 370HR) für niedrigere Geschwindigkeiten; Megtron 6 oder Rogers RO4000-Serie für Hochgeschwindigkeitsbereiche.

- Symmetrie des Leiterplattenaufbaus:

- Anforderung: Vollständig symmetrischer Aufbau, um Verzug während des Reflow-Lötens zu verhindern und eine konsistente Impedanz aufrechtzuerhalten.

- Detail: Signalschichten sollten angrenzend an durchgehende Massebezugsebenen liegen.

- Kupferrauheit:

- Spezifikation: Sehr niedrigprofilige (VLP) oder HVLP-Kupferfolie.

- Grund: Reduziert Skin-Effekt-Verluste bei hohen Frequenzen (>1 GHz).

- Leiterbahnbreite und -abstand:

- Ziel: Basierend auf dem Aufbau berechnet, um 100 Ohm zu erreichen.

- Toleranz: Die Ätztoleranz muss auf ± 0,5 mil oder ± 10 % kontrolliert werden, je nachdem, welcher Wert enger ist.

- Intra-Paar-Schiefe:

- Grenze: < 5 mil (0,127 mm) Fehlanpassung innerhalb des Differenzpaares.

- Auswirkung: Hohe Schiefe wandelt Differenzmodussignale in Gleichtaktrauschen um, was zu einem Versagen bei EMV-Tests führt.

- Einfügedämpfung:

- Budget: Definieren Sie den maximalen Verlust pro Zoll (z. B. -0,5 dB/Zoll bei Nyquist-Frequenz).

- Validierung: Muss durch Simulation oder Testcoupons überprüft werden.

- Rückflussdämpfung:

- Grenze: Typischerweise < -20 dB bis zur Nyquist-Frequenz.

- Bedeutung: Misst, wie viel Signal zur Quelle zurückreflektiert wird.

- Glasgewebe-Stil:

- Spezifikation: Spreizglas (z.B. 1067, 1078) oder mechanisch rotierte Verlegung (10-15 Grad).

- Vorbeugung: Mildert den Fasergeflechteffekt (FWE), der periodische Impedanzschwankungen verursacht.

- Via-Design:

- Anforderung: Minimierte Via-Stummel.

- Maßnahme: Verwenden Sie Rückbohren oder Blind-/Buried-Vias für Signale > 1 Gbit/s, um resonante Stummel zu entfernen.

- Lötstopplack:

- Detail: Berücksichtigen Sie den Dk des Lötstopplacks bei Impedanzberechnungen (senkt die Impedanz normalerweise um 2-3 Ohm).

- Farbe: Typischerweise Grün oder Schwarz, aber stellen Sie die Konsistenz der Dicke sicher.

- Umweltzuverlässigkeit:

- Standard: AEC-Q100-Äquivalent für Platinenbelastung; Thermische Zyklen -40°C bis +125°C (oder +150°C für Motorräume).

Fertigungsrisiken des Automotive-Ethernet-Leiterplattenlayouts (Grundursachen und Vorbeugung)

Selbst bei perfekten Spezifikationen birgt der Übergang vom digitalen Design zur physischen Platine Risiken, die das Automotive-Ethernet-Leiterplattenlayout beeinträchtigen können.

Das Verständnis dieser Fehlermodi ermöglicht es Ihnen, Erkennungsmethoden frühzeitig in der NPI-Phase (Neue Produkteinführung) zu implementieren.

- Impedanzdiskontinuität an Steckverbindern

- Grundursache: Der Footprint des MDI-Steckers (Medium Dependent Interface) durchbricht oft die Referenzebene oder erfordert Pad-Größen, die von der 100-Ohm-Geometrie abweichen.

- Erkennung: TDR-Simulation (Time Domain Reflectometry) zeigt einen Peak an der Steckerschnittstelle.

- Prävention: Verwenden Sie sorgfältig Ground-Aussparungen unter den Pads, um die Induktivität zu erhöhen, oder fügen Sie Ground-Vias hinzu, um sie zu reduzieren; simulieren Sie den Stecker-Breakout-Bereich.

- Referenzebenenlücken (Rückwegunterbrechungen)

- Grundursache: Verlegen von Differentialpaaren über geteilte Leistungsebenen oder Hohlräume in der Masseebene.

- Erkennung: Visuelle Inspektion der inneren Lagen; EMI-Nahfeld-Scanning.

- Prävention: Sorgen Sie für eine durchgehende, solide Masseverbindung entlang des gesamten Pfades des Differentialpaares. Stitching-Vias müssen verwendet werden, wenn die Lagen gewechselt werden.

- Modenkonversion (Differenziell zu Gleichtakt)

- Grundursache: Asymmetrie im physikalischen Layout (z.B. eine Leiterbahn ist länger, oder eine Leiterbahn ist näher an einem Metallstück/Massefläche als die andere).

- Erkennung: Mixed-Mode S-Parameter-Messungen (SDC11/SDC21).

- Prävention: Strikte Symmetrie beibehalten; vermeiden Sie die Verlegung in der Nähe von Platinenkanten oder hohen Bauteilen; entfernen Sie "gegossene" Masse zwischen den Schenkeln des Differentialpaares.

- Übersprechen von Aggressor-Signalen

- Grundursache: Hochspannungs-Schaltleitungen (z.B. von DC-DC-Wandlern) zu nahe an den Ethernet-Paaren verlegt.

- Erkennung: Nahnebensprechen (NEXT) und Fernnebensprechen (FEXT) Tests.

- Vermeidung: "3W"- oder "5W"-Abstandsregeln (3x oder 5x Leiterbahnbreite) zwischen Ethernet-Paaren und anderen Signalen einhalten. Schutzleiterbahnen oder Masse-Via-Zäune verwenden, wenn der Platz es zulässt.

- Fasergeflecht-Effekt (FWE)

- Ursache: Eine Leitung des Differenzialpaares verläuft über einem Glasbündel, während die andere über Harz verläuft, was zu unterschiedlichen Ausbreitungsgeschwindigkeiten führt.

- Erkennung: Phasenverschiebung bei Hochfrequenzmessungen; schwer mit Standard-TDR zu erkennen.

- Vermeidung: "Spread Glass"-Dielektrika verwenden oder Leiterbahnen in einem leichten Winkel (10°) zum Geflecht verlegen.

- Via-Stumpf-Resonanz

- Ursache: Unbenutzte Teile von durchkontaktierten Vias wirken bei bestimmten Frequenzen als Antennen (Viertelwellenresonanz).

- Erkennung: Scharfer Einbruch in der Einfügedämpfungskurve bei hohen Frequenzen.

- Vermeidung: Rückbohren für Durchkontaktierungen spezifizieren oder Blind-/Vergrabene Vias für kritische Hochgeschwindigkeitsnetze verwenden.

- Kupferätzvariationen

- Ursache: Fertigungsprozessschwankungen führen zu trapezförmigen statt rechteckigen Leiterbahnformen, was die Impedanz verändert.

- Erkennung: Querschnittsanalyse (Mikroschliff) von Coupons.

- Vermeidung: Ätzfaktor in die Impedanzmodellierung einbeziehen; einen Lieferanten mit automatischer optischer Inspektion (AOI) für feine Leiterbahnen wählen.

- CAF (Conductive Anodic Filament) Wachstum

- Ursache: Elektrochemische Migration entlang der Glasfasern zwischen vorgespannten Vias in rauen Automobilumgebungen.

- Erkennung: Hochspannungs-Isolationswiderstandsprüfung; Langzeit-Zuverlässigkeits-Stresstests.

- Prävention: Verwendung von CAF-beständigen Materialien; Vergrößerung des Abstands zwischen Vias, die mit unterschiedlichen Potenzialen verbunden sind.

- Ungleichheit der Wärmeausdehnung

- Ursache: Unterschiedliche WAK (Wärmeausdehnungskoeffizient) zwischen dem Leiterplattensubstrat und großen Automobilsteckverbindern oder BGAs.

- Erkennung: Rissbildung an Lötstellen nach Temperaturwechseltests.

- Prävention: Anpassung des WAK des Leiterplattenmaterials an die Komponenten; Verwendung von Underfill für große BGAs.

- Rückstände und Sauberkeit

- Ursache: Unter Bauteilen eingeschlossene Flussmittelrückstände beeinflussen die Oberflächenimpedanz und verursachen Kriechströme.

- Erkennung: Ionische Kontaminationsprüfung (ROSE-Test).

- Prävention: Festlegung strenger Waschprotokolle und Sauberkeitsstandards (IPC-5704).

Validierung und Abnahme des Automotive Ethernet PCB-Layouts (Tests und Bestehenskriterien)

Die Minderung von Risiken erfordert einen robusten Validierungsplan. Sie können sich nicht ausschließlich auf das standardmäßige "Bestanden"-Zertifikat des Herstellers für das Automotive Ethernet PCB-Layout verlassen.

Die folgenden Tests überprüfen, ob die physische Platine die elektrischen und umweltbezogenen Anforderungen der Automobilindustrie erfüllt.

- Impedanzprüfung (TDR)

- Ziel: Bestätigen, dass die Leiterbahnimpedanz 100 Ohm beträgt.

- Methode: Zeitbereichsreflektometrie an Testcoupons und tatsächlichen Leiterplatten.

- Akzeptanzkriterien: Mittlere Impedanz 100 Ohm ± 10 %; keine Einzelpunktabweichung > ± 15 % (außer an Stecker-Footprints).

- Einfügedämpfungsmessung

- Ziel: Sicherstellen, dass die Signalstärke über die Distanz erhalten bleibt.

- Methode: VNA (Vektor-Netzwerkanalysator)-Messung des S21-Parameters.

- Akzeptanzkriterien: Dämpfung < Spezifizierter Grenzwert (z. B. -0,5 dB/Zoll) bis zur erforderlichen Bandbreitengrenze.

- Rückflussdämpfungsmessung

- Ziel: Minimale Signalreflexion überprüfen.

- Methode: VNA-Messung des S11-Parameters.

- Akzeptanzkriterien: < -20 dB bei niedrigen Frequenzen; < -10 dB bei Nyquist-Frequenz.

- Modenkonversion (LCL/LCTL)

- Ziel: Symmetrie und Immunität gegenüber Rauschkonversion prüfen.

- Methode: VNA-Messung des Longitudinal Conversion Loss.

- Akzeptanzkriterien: Muss die Grenzwerte von IEEE 802.3bw (100BASE-T1) oder 802.3bp (1000BASE-T1) erfüllen.

- Thermoschock / Temperaturwechselprüfung

- Ziel: Zuverlässigkeit der Durchkontaktierungen und Materialstabilität überprüfen.

- Methode: 1000 Zyklen von -40°C bis +125°C.

- Akzeptanzkriterien: < 5 % Widerstandsänderung; keine Delamination oder Risse.

- Interconnect Stress Test (IST)

- Ziel: Beschleunigte Prüfung der Zuverlässigkeit von Vias.

- Methode: Schnelle Temperaturwechselprüfung spezifischer Coupons.

- Akzeptanzkriterien: Bestehen von 500 Zyklen ohne offene Stromkreise.

- Oberflächenisolationswiderstand (SIR)

- Ziel: Erkennung von Risiken der elektrochemischen Migration.

- Methode: Vorspannung bei hoher Luftfeuchtigkeit (85°C/85% RH) angelegt.

- Akzeptanzkriterien: Widerstand > 100 MΩ nach 168 Stunden.

- Lötbarkeitsprüfung

- Ziel: Sicherstellen, dass die Pads Lötmittel zuverlässig annehmen.

- Methode: Tauch- und Sichtprüfung / Benetzungsbalance-Test.

- Akzeptanzkriterien: > 95% Abdeckung; glatte Beschichtung.

- Dimensionsstabilität

- Ziel: Sicherstellen, dass die Platine sich nicht über die Toleranz hinaus verzieht oder schrumpft/dehnt.

- Methode: Koordinatenmessmaschine (KMM).

- Akzeptanzkriterien: Verzug und Verdrehung < 0,75%; Registrierung innerhalb von ± 3 mil.

- Mikroschnittanalyse

- Ziel: Überprüfung von Lagenaufbau, Beschichtungsdicke und dielektrischer Integrität.

- Methode: Zerstörende Querschnittsanalyse.

- Akzeptanzkriterien: Kupferdicke entspricht IPC Klasse 3; keine Hohlräume im Laminat.

Qualifizierungs-Checkliste für Lieferanten von Automotive Ethernet PCB-Layouts (Angebotsanfrage, Audit, Rückverfolgbarkeit)

Um ein erfolgreiches Automotive Ethernet PCB-Layout zu realisieren, benötigen Sie einen Lieferanten, der den Unterschied zwischen einer Standard-Leiterplatte und einer hochgeschwindigkeitsfähigen Leiterplatte in Automobilqualität versteht.

Verwenden Sie diese Checkliste, um potenzielle Partner zu prüfen oder Ihre aktuelle Lieferkette zu auditieren.

RFQ-Eingaben (Was Sie bereitstellen müssen)

- Gerber-Dateien (RS-274X): Vollständiger Satz einschließlich Bohrerdateien.

- IPC-Netzliste: Zum Vergleich des elektrischen Tests.

- Lagenaufbauzeichnung: Explizite Definition der Lagenreihenfolge, des Materialtyps (Marke/Serie) und der Dicke.

- Impedanztabelle: Auflistung von Lage, Leiterbahnbreite, Abstand und Zielimpedanz für jedes kontrollierte Netz.

- Bohrbild: Identifizierung von metallisierten vs. nicht-metallisierten Löchern und Backdrill-Positionen.

- Fertigungsnotizen: Angabe von IPC Klasse 3, Automobilstandards und Sauberkeitsanforderungen.

- Nutzenzeichnung: Falls ein spezifisches Array-Layout für die Bestückung benötigt wird.

- Anforderung für Testcoupons: Angabe, ob IPC-Standardcoupons oder kundenspezifische In-Circuit-Coupons erforderlich sind.

- Volumenprognosen: EAU (geschätzter Jahresverbrauch) zur Bestimmung der Werkzeugstrategie.

Fähigkeitsnachweis (Was sie demonstrieren müssen)

- Automobilzertifizierung: Gültiges IATF 16949 Zertifikat.

- Impedanzkontrolle: Nachgewiesene Fähigkeit, eine Toleranz von ± 5% einzuhalten.

- Backdrilling: Bewährter Prozess für Tiefenbohrungen mit Röntgenverifikation.

- Materialbestand: Zugang zu Laminaten in Automobilqualität (Isola, Rogers, Panasonic) ohne übermäßige Lieferzeiten.

- VNA-Tests: Hauseigene Fähigkeit zur Messung von S-Parametern (nicht nur TDR).

- Sauberkeitslabor: Hauseigene Ionenchromatographie oder gleichwertige Tests.

- AOI-Fähigkeit: Hochauflösende Inspektion für feine Leiterbahnen (< 4 mil).

- Registrierungsgenauigkeit: Laser-Direktbelichtungs (LDI)-Fähigkeit für enge Lötstopplackstege.

Qualitätssystem & Rückverfolgbarkeit

- Rückverfolgbarkeit: Fähigkeit, jede Leiterplatte bis zum Rohmateriallos und Produktionsdatumscode zurückzuverfolgen.

- PFMEA: Prozess-FMEA (Fehler-Möglichkeits- und Einfluss-Analyse) speziell für Hochgeschwindigkeitsplatinen.

- Kontrollplan: Detaillierte Prüfpunkte für kritische Merkmale (Impedanz, Lochwandqualität).

- MSA: Messsystemanalyse für ihre Prüfgeräte (Gage R&R).

- Nichtkonformes Material: Klares Quarantäne- und Ausschussverfahren.

- Aufbewahrung von Aufzeichnungen: Aufbewahrung von Qualitätsaufzeichnungen für über 15 Jahre (typische Anforderung der Automobilindustrie).

Änderungskontrolle & Lieferung

- PCN-Verfahren: Strikte Einhaltung der Produktänderungsmitteilung (keine Änderungen ohne Genehmigung).

- Pufferbestand: Bereitschaft, Sicherheitsbestand für Rohmaterialien zu halten.

- Kapazitätsplanung: Nachgewiesene Kapazität zur Bewältigung von Spitzenbedarfen.

- Logistik: Erfahrung mit Lieferplänen der Automobilindustrie (JIT/Kanban).

- Verpackung: ESD- und Feuchtigkeitsschutzverpackung (MBB) konform mit J-STD-033.

- Notfallwiederherstellung: Plan für Produktionskontinuität bei Problemen mit der Anlage.

So wählen Sie das Automotive Ethernet PCB-Layout (Kompromisse und Entscheidungsregeln)

Entscheidungen beim Automotive Ethernet PCB-Layout beinhalten oft das Abwägen von Leistung, Kosten und Herstellbarkeit. Es gibt selten eine „perfekte“ Lösung, sondern nur den richtigen Kompromiss für Ihre spezifische Anwendung.

Hier sind die wichtigsten Entscheidungsregeln, die Ihre Architektur leiten sollen:

- Materialauswahl: FR4 vs. verlustarme Materialien

- Wenn Sie Kosten priorisieren und Ihre Geschwindigkeit 100BASE-T1 (100 Mbit/s) beträgt, wählen Sie hoch-Tg FR4. Es ist für kurze Strecken ausreichend.

- Wenn Sie die Signalintegrität priorisieren für 1000BASE-T1 oder Multi-Gig über lange Distanzen (> 5 Meter), wählen Sie Megtron 6 oder Rogers. Der reduzierte Verlust ist notwendig, um die Kanalbudgets einzuhalten.

- Lagenaufbau: 4-Lagen vs. 6-Lagen+

- Wenn Sie Kosten priorisieren und eine geringe Bauteildichte haben, wählen Sie einen 4-Lagen-Aufbau.

- Wenn Sie die EMV-Leistung priorisieren, wählen Sie einen 6-Lagen-Aufbau. Dies ermöglicht dedizierte Masseebenen, die die Signalschichten abschirmen und die abgestrahlten Emissionen erheblich reduzieren.

- Vias: Durchkontaktierungen vs. HDI (Blind/Buried)

- Wenn Sie die Fertigungsvereinfachung priorisieren, verwenden Sie Standard-Durchkontaktierungen mit Rückbohren für kritische Netze.

- Wenn Sie Dichte und Leistung priorisieren, verwenden Sie HDI (High Density Interconnect) mit Microvias. Dies eliminiert Stubs auf natürliche Weise, erhöht aber die Leiterplattenkosten um 20-40%.

- Steckerstrategie: Integrierte Magnetics vs. Diskret

- Wenn Sie den Platz auf der Platine priorisieren, wählen Sie Steckverbinder mit integrierten Magnetics.

- Wenn Sie Layout-Flexibilität und Wärmemanagement priorisieren, wählen Sie diskrete Magnetik. Dies ermöglicht es Ihnen, die Platzierung des Transformators relativ zum PHY zu optimieren.

- Abschirmung: Ungeschirmt (UTP) vs. Geschirmt (STP)

- Wenn Sie Gewicht und Kabelbaumkosten priorisieren, wählen Sie UTP. Dies erfordert eine strengere PCB-Layout-Symmetrie, um Rauschen zu unterdrücken.

- Wenn Sie Störfestigkeit priorisieren in extrem rauen Umgebungen (z.B. in der Nähe von EV-Wechselrichtern), wählen Sie STP. Dies lockert einige PCB-Layout-Einschränkungen, erhöht aber das Systemgewicht.

- Testpunkte: Auf der Leiterbahn vs. Testpads

- Wenn Sie Signalqualität priorisieren, vermeiden Sie es, Testpunkte direkt auf Hochgeschwindigkeits-Differenzpaaren zu platzieren.

- Wenn Sie Debug-Fähigkeit priorisieren, verwenden Sie kleine Testpads, aber simulieren Sie den Stub-Effekt, den sie erzeugen.

Häufig gestellte Fragen (FAQ) zum Automotive Ethernet PCB-Layout (Kosten, Lieferzeit, DFM-Dateien, Materialien, Tests)

F: Wie wirkt sich die Komplexität des Automotive Ethernet PCB-Layouts auf die Stückkosten aus? A: Komplexität treibt die Kosten durch Materialwahl und Lagenanzahl in die Höhe. Der Wechsel von Standard-FR4 zu Megtron 6 kann die Laminatkosten um das 2-3-fache erhöhen, und das Hinzufügen von Backdrilling- oder HDI-Lagen erhöht die Herstellungskosten um 15-30% aufgrund zusätzlicher Prozessschritte.

F: Was ist die typische Lieferzeit für hochgeschwindigkeitsfähige Materialien in Automobilqualität? A: Standard-High-Tg-FR4 ist normalerweise auf Lager. Spezialisierte verlustarme Materialien wie Isola Tachyon oder Panasonic Megtron haben jedoch oft Lieferzeiten von 4-6 Wochen, wenn sie nicht prognostiziert wurden, daher ist eine frühzeitige Einbindung Ihres Lieferanten entscheidend.

F: Welche spezifischen DFM-Dateien werden für eine genaue Impedanzmodellierung benötigt? A: Über standardmäßige Gerbers hinaus müssen Sie einen Stackup-Vorschlag bereitstellen, der die spezifische Dielektrikum-Marke und den Harzgehalt (z. B. "Isola 370HR 1080 Prepreg") enthält. Dies ermöglicht es der Fabrik, die genaue Press-out-Dicke zu berechnen und die Leiterbahnbreiten für die 100-Ohm-Konformität anzupassen.

F: Können wir Standard-FR4 für das 1000BASE-T1 Automotive Ethernet PCB-Layout verwenden? A: Es ist für sehr kurze Leiterbahnen (< 2-3 Zoll) möglich, aber riskant. Standard-FR4 hat bei hohen Frequenzen höhere Verluste und weniger konsistente dielektrische Eigenschaften, was in längeren Kanälen zu Signalverschlechterung und EMV-Fehlern führen kann.

F: Was sind die Akzeptanzkriterien für die Rückbohrtiefe? A: Die verbleibende Stummelänge sollte idealerweise weniger als 10 mil (0,25 mm) betragen. Hersteller spezifizieren typischerweise eine "darf nicht geschnitten werden"-Schicht (die interne Signalschicht) und eine "muss geschnitten werden"-Tiefe, mit einer Toleranz von ± 2-4 mil.

F: Wie testen Sie den "Fasergeflechteffekt" in der Produktion? A: Sie können in der Massenproduktion im Allgemeinen nicht jede Platine auf FWE testen. Stattdessen validieren Sie das Design während der Prototypenphase mit "Spread-Glass"-Materialien oder abgewinkelter Leiterbahnführung und stellen sicher, dass der Lieferant die Materialkonstruktion im Kontrollplan festlegt. F: Was ist der Unterschied zwischen IPC Klasse 2 und Klasse 3 für Automotive Ethernet? A: Klasse 3 erfordert strengere Ringe, Beschichtungsdicken und visuelle Standards, was eine höhere Zuverlässigkeit unter Vibrationen und thermischer Belastung gewährleistet. Automotive-Ethernet-Leiterplatten sollten fast immer nach IPC Klasse 3 Standards gebaut werden.

F: Warum ist "Modenkonversion" für das Layout von Automotive-Ethernet-Leiterplatten entscheidend? A: Modenkonversion misst, wie viel des differentiellen Signals (Daten) in Gleichtaktrauschen (EMI) umgewandelt wird. Da Automotive Ethernet ungeschirmte Kabel verwendet, führt eine hohe Modenkonversion zu sofortigen EMV-Testfehlern und Problemen mit abgestrahlten Emissionen.

Ressourcen für das Layout von Automotive-Ethernet-Leiterplatten (verwandte Seiten und Tools)

- Automotive-Elektronik-Leiterplatten: Erfahren Sie mehr über den breiteren Kontext von Automobilstandards, einschließlich IATF 16949 Anforderungen und sicherheitskritischen Anwendungen.

- Hochgeschwindigkeits-Leiterplatten: Tauchen Sie tief in die technischen Aspekte der Signalintegrität, Materialauswahl und Routing-Techniken für Gigabit-Datenraten ein.

- Leiterplatten-Lagenaufbau: Erfahren Sie, wie Sie einen symmetrischen Lagenaufbau entwerfen, der eine kontrollierte Impedanz unterstützt und EMV-Risiken reduziert.

- Impedanzrechner: Verwenden Sie dieses Tool, um Leiterbahnbreite und -abstand für Ihre 100-Ohm-Differentialpaare abzuschätzen, bevor Sie Ihr Design finalisieren.

- Leiterplattenqualität: Verstehen Sie die Inspektionsprozesse, einschließlich Mikroschnitte und elektrische Tests, die garantieren, dass Ihre Leiterplatten den Automobilspezifikationen entsprechen.

Angebot für Automotive Ethernet Leiterplattenlayout anfordern (DFM-Überprüfung + Preisgestaltung)

Bereit, Ihr Design zu validieren? Bei APTPCB bieten wir eine umfassende DFM-Überprüfung an, um Impedanzfehlanpassungen und Fertigungsprobleme zu erkennen, bevor Sie sich für die Werkzeugbestückung entscheiden.

Um ein genaues Angebot und einen DFM-Bericht zu erhalten, senden Sie bitte:

- Gerber-Dateien: RS-274X- oder ODB++-Format.

- Lagenaufbau & Impedanz: Ihre gewünschte Lagenanzahl und 100-Ohm-Zielspezifikationen.

- Materialanforderungen: Spezifische Laminatpräferenz (z.B. Megtron, Rogers oder High-Tg FR4).

- Volumen & Zeitplan: Prototypenmenge und geschätzter Hochlauf der Massenproduktion.

Klicken Sie hier, um ein Angebot & eine DFM-Überprüfung anzufordern – Unser Ingenieurteam wird Ihre Dateien prüfen und innerhalb von 24 Stunden eine detaillierte Kostenanalyse und Risikobewertung bereitstellen.

Fazit: Nächste Schritte für das Automotive Ethernet Leiterplattenlayout

Die Beherrschung des Automotive Ethernet PCB-Layouts geht über das bloße Verlegen von Leiterbahnen hinaus; es geht darum, den gesamten physikalischen Kanal zu verwalten, um die Datenintegrität in einer feindlichen Umgebung zu gewährleisten. Durch die Definition klarer Spezifikationen für Impedanz und Materialien, das Verständnis der Ursachen für Signalverluste und die Durchsetzung eines strengen Validierungsplans können Sie die häufigsten Risiken im Zusammenhang mit Hochgeschwindigkeits-Automobilnetzwerken eliminieren. Verwenden Sie die bereitgestellte Checkliste, um Ihre Lieferanten zu überprüfen und sicherzustellen, dass sie in der Lage sind, konsistente, zuverlässige Platinen zu liefern, die Ihre Fahrzeuge verbunden und sicher halten.