Kurze Antwort (30 Sekunden)

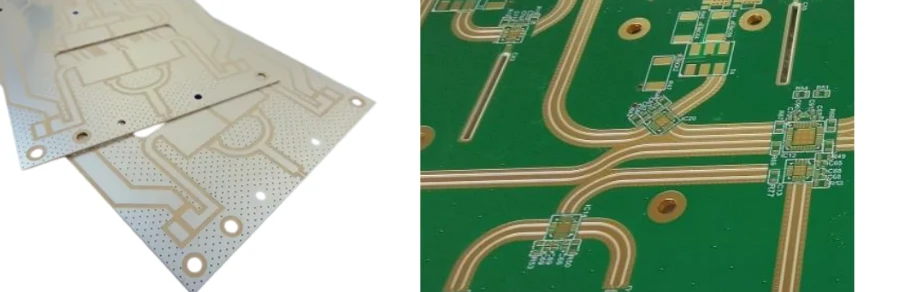

Eine Kalibrierungs-Leiterplatte dient als Präzisionsreferenzstandard für Testgeräte, wie Vektor-Netzwerkanalysatoren (VNAs) oder einen AC-Leistungsanalysator. Im Gegensatz zu Standard-Leiterplatten erfordern diese extreme Stabilität, eine enge Impedanzkontrolle und minimale Signalverluste.

- Materialstabilität: Verwenden Sie Hochfrequenzlaminate (z.B. Rogers, Taconic) mit einer stabilen Dielektrizitätskonstante (Dk) über Temperatur und Frequenz.

- Impedanztoleranz: Geben Sie eine kontrollierte Impedanz innerhalb von ±5% oder ±3% anstelle der Standard-±10% an.

- Oberflächenveredelung: Chemisch Nickel/Immersionsgold (ENIG) oder Hartgold ist zwingend erforderlich für flache Kontaktflächen und Oxidationsbeständigkeit.

- Leiterbahngeometrie: Minimieren Sie Via-Stubs und verwenden Sie Rückbohrungen, um Signalreflexionen bei hohen Frequenzen zu reduzieren.

- Steckerpräzision: Das Footprint-Design muss exakt zum spezifischen Steckermodell passen, um parasitäre Kapazitäten zu vermeiden.

- Validierung: Jede Leiterplatte erfordert eine Zeitbereichsreflektometrie (TDR)-Prüfung vor dem Versand.

Wann Kalibrierungs-Leiterplatten zum Einsatz kommen (und wann nicht)

Zu verstehen, wann in hochpräzise Fertigung investiert werden sollte, ist entscheidend für die Projektbudgetierung und Leistung.

Wann eine Kalibrierungs-Leiterplatte verwendet werden sollte:

- VNA-Kalibrierkits: Sie entwerfen Short-Open-Load-Thru (SOLT) oder Thru-Reflect-Line (TRL) Standards für HF-Messungen.

- Produktionstestvorrichtungen: Die Leiterplatte fungiert als „Goldene Einheit“, um die Bestanden/Nicht bestanden-Grenzwerte eines automatischen Testsystems zu überprüfen.

- Leistungsmessreferenzen: Sie bauen eine Referenzplatine für einen AC-Leistungsanalysator, bei der der Strompfadwiderstand bekannt und stabil sein muss.

- Signalintegritätsprüfung: Sie müssen den Verlust und die Phasenverzögerung spezifischer Übertragungsleitungen oder Materialien charakterisieren.

- Aktive Kalibrierungssysteme: Das Design umfasst eine Kalibrierungsgenerator-Schaltung, die präzise Signale für Selbsttestroutinen einspeist.

Wenn Standard-Leiterplattenprozesse ausreichen:

- Allgemeine Logik-Prototypenentwicklung: Wenn die Platine nur digitale Signale mit niedriger Geschwindigkeit (I2C, UART) für die Firmware-Entwicklung führt.

- Grober Funktionstest: Wenn die genaue Amplitude oder Phase eines Signals weniger wichtig ist als seine bloße Anwesenheit.

- Niederfrequenz-Unterhaltungselektronik: Geräte, die unter 100 MHz arbeiten, benötigen oft nicht die teuren Materialien, die in Kalibrierungsstandards verwendet werden.

- Einweg-Breakout-Boards: Einfache Adapter, bei denen Einfügedämpfungsschwankungen von 0,5 dB akzeptabel sind.

Regeln & Spezifikationen

Um metrologische Leistung zu erzielen, empfiehlt APTPCB (APTPCB PCB Factory) die Einhaltung strenger Design- und Fertigungsregeln. Die folgende Tabelle skizziert die kritischen Parameter für eine Kalibrierungs-Leiterplatte.

| Regel | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Bei Missachtung |

|---|---|---|---|---|

| Toleranz der Dielektrizitätskonstante (Dk) | ±0.05 oder besser | Bestimmt die Impedanzgenauigkeit und Signalgeschwindigkeit. | Materialdatenblatt & TDR-Test. | Impedanzfehlanpassung; Phasenfehler bei Messungen. |

| Verlustfaktor (Df) | < 0.003 bei 10 GHz | Minimiert Signalverluste (Einfügedämpfung) mit steigender Frequenz. | VNA-Transmissionsprüfung (S21). | Hohe Signaldämpfung; ungenaue Verstärkungskalibrierung. |

| Oberflächenrauheit des Kupfers | VLP oder HVLP (Sehr niedriges Profil) | Raues Kupfer erhöht die Skin-Effekt-Verluste bei hohen Frequenzen. | Mikroschnittanalyse. | Höhere als erwartete Einfügedämpfung; Modellierungsfehler. |

| Impedanzkontrolle | ±5% (Standard), ±3% (Premium) | Gewährleistet maximale Leistungsübertragung und minimiert Reflexionen. | Impedanzrechner & TDR. | Signalreflexionen (Rückflussdämpfung) verschlechtern die Kalibriergenauigkeit. |

| Oberflächenveredelung | ENIG oder Hartgold (>30µin) | Bietet eine ebene Oberfläche für den Steckersitz und widersteht Korrosion. | Röntgenfluoreszenz (RFA). | Der Kontaktwiderstand variiert; die Kalibrierung driftet mit der Zeit. |

| Lötstopplack-Registrierung | ±2 mil (0.05 mm) | Verhindert, dass die Maske auf die Pads übergreift und das Löten beeinträchtigt. | Optische Inspektion. | Schlechter Steckersitz; Impedanzdiskontinuitäten an den Pads. |

| Via-Plattierungsdicke | > 25 µm (1 mil) | Gewährleistet thermische Zuverlässigkeit und geringen Widerstand für Masseverbindungen. | Querschnittsanalyse. | Via-Rissbildung während des Thermozyklus; instabile Masseverbindung. |

| Genauigkeit der Leiterbahnbreite | ±10% oder ±0.5 mil | Beeinflusst direkt die charakteristische Impedanz. | AOI (Automatisierte Optische Inspektion). | Impedanz außerhalb der Spezifikation; Schwankungen von Charge zu Charge. |

| Minderung des Gewebeeffekts | Spread Glass (z.B. 1067, 1078) | Verhindert periodische Belastungseffekte durch Glasfaserbündel. | Materialspezifikationsprüfung. | Skew in Differentialpaaren; Resonanz bei bestimmten Frequenzen. |

| Feuchtigkeitsaufnahme | < 0.1% | Wasser ist polar und verändert den Dk des Substrats. | Ausheiz- & Gewichtstest. | Elektrische Eigenschaften driften in feuchten Umgebungen ab. |

| Wärmeausdehnung (Z-Achse) | < 50 ppm/°C | Verhindert Laufbahnrisse und Pad-Abhebungen während des Lötens. | TMA (Thermomechanische Analyse). | Platinenausfall nach dem Reflow oder während des Temperaturzyklus. |

Implementierungsschritte

Die Entwicklung einer Kalibrierungs-Leiterplatte erfordert einen systematischen Ansatz, der die physikalische Genauigkeit gegenüber der Komponentendichte priorisiert.

Frequenzbereich definieren: Bestimmen Sie die obere Frequenzgrenze (z.B. 6 GHz, 20 GHz, 40 GHz). Dies bestimmt die Materialauswahl. Für Frequenzen über 1 GHz ist Standard-FR4 oft unzureichend.

Substratmaterial auswählen: Wählen Sie ein Laminat mit niedrigem Df und stabilem Dk. APTPCB empfiehlt oft die Rogers-Serie für HF-Kalibrierungsplatinen aufgrund ihrer Konsistenz.

Lagenaufbau entwerfen: Berechnen Sie die Leiterbahnbreiten für eine Impedanz von 50 Ohm (oder die erforderliche Impedanz). Stellen Sie sicher, dass die Referenzebenen aus massivem Kupfer bestehen. Vermeiden Sie geteilte Ebenen unter kritischen Signalpfaden, um Diskontinuitäten des Rückwegs zu verhindern.

Steckverbinder-Footprints optimieren: Verlassen Sie sich nicht auf Standard-CAD-Bibliotheks-Footprints. Fordern Sie den vom Hersteller empfohlenen Hochfrequenz-Footprint an. Verwenden Sie "Anti-Pads" (Ausschnitte in Masseebenen), um die Impedanz des Steckverbinder-Pin-Übergangs anzupassen.

Kritische Leiterbahnen routen: Halten Sie Kalibrierungsleiterbahnen so kurz wie möglich. Wenn Sie eine "Thru"-Leitung entwerfen, stellen Sie sicher, dass es sich um eine gerade Linie handelt. Vermeiden Sie Vias auf dem Signalpfad, wenn möglich. Wenn Vias benötigt werden, verwenden Sie Rückbohrungen, um Stubs zu entfernen.

Masse-Vias hinzufügen: Verbinden Sie die Masseebenen mit Vias entlang des Signalpfads (Via-Fencing). Der Abstand sollte weniger als $\lambda/20$ der höchsten Betriebsfrequenz betragen, um Resonanzen zu vermeiden.

Fertigungsdatengenerierung: Exportieren Sie Gerber-Dateien mit hoher Auflösung. Fügen Sie eine Bohrtabelle bei, die die fertigen Lochgrößen angibt. Kennzeichnen Sie die Anforderungen an die "kontrollierte Impedanz" in den Fertigungsnotizen deutlich.

Nachfertigungsprüfung: Überprüfen Sie nach Erhalt der unbestückten Platinen die Leiterbahnkanten visuell. Verwenden Sie ein TDR, um die Impedanz zu überprüfen, bevor Sie teure Steckverbinder montieren.

Montage und Reinigung: Löten Sie Steckverbinder mit einem Präzisionsprofil. Flussmittelrückstände können bei hohen Frequenzen leitfähig oder kapazitiv sein; sorgen Sie für eine gründliche Reinigung.

Endgültige Charakterisierung: Messen Sie die S-Parameter (S11, S21) der fertigen Kalibrierungs-Leiterplatte. Speichern Sie diese Daten als "Korrekturdatei" für den Endbenutzer.

Fehlermodi & Fehlerbehebung

Auch bei einem perfekten Design können während der Fertigung oder Nutzung Probleme auftreten. Die folgende Tabelle hilft bei der Diagnose häufiger Fehler in Kalibrierungs-Leiterplatten.

Symptom: Impedanz ist durchweg niedriger als ausgelegt.

- Ursachen: Leiterbahnbreite ist zu breit (Überätzungsprobleme), oder die Dielektrikumdicke ist dünner als spezifiziert (Laminierungsdruck).

- Prüfungen: Leiterbahnbreite mit einem Mikroskop messen. Stackup-Bericht vom Hersteller prüfen.

- Behebung: Leiterbahnbreite für die nächste Revision anpassen.

- Prävention: Verwenden Sie die DFM-Richtlinien, um realistische Ätztoleranzen festzulegen.

Symptom: Hohe Einfügedämpfung bei hohen Frequenzen.

- Ursachen: Material-Df ist zu hoch, Kupfer ist zu rau, oder Beschichtungsprobleme (z.B. Nickelresonanz).

- Prüfungen: Materialtyp überprüfen. Prüfen, ob die ENIG-Nickelschicht HF-Signale beeinflusst (magnetische Eigenschaften).

- Behebung: Für sehr hohe Frequenzen (>20 GHz) auf Silberimmersion oder OSP umstellen.

- Prävention: "VLP-Kupfer" und eine geeignete Oberflächenveredelung in den Fertigungsnotizen angeben.

Symptom: Messwertdrift über die Zeit.

- Ursachen: Feuchtigkeitsaufnahme, Oxidation der Kontakte oder mechanische Belastung der Steckverbinder.

- Prüfungen: Platine backen, um Feuchtigkeit zu entfernen. Steckverbinder auf Verschleiß prüfen.

- Behebung: Kalibrierplatinen in einem Exsikkator lagern. Abgenutzte Steckverbinder ersetzen.

- Vorbeugung: Materialien mit geringer Hygroskopizität verwenden (z. B. auf PTFE-Basis).

Symptom: Wellen in S-Parameter-Daten (Resonanz).

- Ursachen: Der Abstand der Masseverbindungen ist zu groß, oder Stub-Resonanz von nicht rückgebohrten Vias.

- Überprüfungen: Resonanzfrequenz von Via-Stubs berechnen. Abstand der Masseverbindungen prüfen.

- Behebung: Vias rückbohren oder Blind-/Buried-Vias verwenden.

- Vorbeugung: Den Übergang vom Steckverbinder zur Leiterplatte in 3D-EM-Software simulieren.

Symptom: Schlechte Wiederholbarkeit von Verbindungen.

- Ursachen: Variation des Steckverbinderdrehmoments, Unebenheit der Oberflächengüte oder Pad-Abhebung.

- Überprüfungen: Drehmomentschlüssel verwenden. Pad-Ebenheit prüfen.

- Behebung: Neu verlöten oder die Platine ersetzen, wenn Pads beschädigt sind.

- Vorbeugung: Größere Pads oder Teardrops für mechanische Festigkeit verwenden; ENIG-Oberfläche sicherstellen.

Symptom: Thermische Drift während des Betriebs.

- Ursachen: Hoher Wärmeausdehnungskoeffizient (CTE) des Materials.

- Überprüfungen: Platine erwärmen und Impedanzänderung überwachen.

- Behebung: Keramikgefüllte Laminate mit niedrigem CTE verwenden.

- Vorbeugung: Materialien auswählen, die über den gesamten Betriebstemperaturbereich stabil sind.

Entwurfsentscheidungen

Bei der Finalisierung des Layouts beeinflussen spezifische architektonische Entscheidungen die Nützlichkeit der Kalibrierungs-Leiterplatte.

Steckerplatzierung: Für VNA-Kalibrierkits platzieren Sie die Steckverbinder weit genug auseinander, um dem Benutzer das Anbringen von Kabeln ohne mechanische Interferenz zu ermöglichen. Halten Sie sie jedoch nah genug beieinander, um die Platinengröße und Verformung zu minimieren.

Die Integration des „Kalibriergenerators“: Einige fortschrittliche Kalibrierplatinen enthalten einen aktiven Kalibriergenerator. Diese Schaltung erzeugt einen bekannten Impuls oder Frequenzkamm. Wenn Ihr Design dies beinhaltet:

- Isolieren Sie die Stromversorgung des Generators von den Referenzleiterbahnen.

- Schirmen Sie den Generatorbereich ab, um zu verhindern, dass Strahlung in die Kalibrierstandards einkoppelt.

- Verwenden Sie thermische Entlastungen sorgfältig; der Generator erzeugt Wärme, die den Dk benachbarter Leiterbahnen verändern kann.

AC-Leistungsanalysator-Standards: Für Platinen, die zur Kalibrierung eines AC-Leistungsanalysators verwendet werden:

- Die Leiterbahndicke (Kupfergewicht) ist entscheidend. Verwenden Sie 2oz oder 3oz Kupfer, um Strom ohne Erwärmung zu führen.

- Verwenden Sie Kelvin-Verbindungen (4-Draht-Messung) für Strommesswiderstände.

- Stellen Sie eine hohe Spannungsisolation (Kriechstrecke und Luftstrecke) zwischen den Phasen sicher.

Häufig gestellte Fragen (FAQ)

F: Warum wird ENIG gegenüber HASL für Kalibrier-PCBs bevorzugt? A: HASL (Hot Air Solder Leveling) hinterlässt eine unebene Oberfläche, was zu Steckverbindermissausrichtung und Impedanzschwankungen führt. ENIG bietet eine perfekt flache Oberfläche, die für Hochfrequenzkontakt unerlässlich ist.

F: Kann ich FR4 für eine Kalibrier-PCB verwenden? A: Nur für niedrige Frequenzen (typischerweise < 500 MHz) oder DC-Anwendungen. FR4 hat einen variablen Dk und hohe Verluste, was es für Präzisions-HF- oder Hochgeschwindigkeits-Digitalkalibrierungen ungeeignet macht.

F: Was ist die typische Lieferzeit für diese Platinen? A: Aufgrund spezialisierter Materialien (wie Rogers oder Taconic) und präziser Ätzanforderungen betragen die Lieferzeiten typischerweise 5-10 Tage. APTPCB kann dies beschleunigen, wenn Materialien auf Lager sind.

F: Wie oft sollte eine Kalibrierungs-Leiterplatte ersetzt werden? A: Das hängt von der Nutzung ab. Steckverbinder verschleißen nach einigen hundert Steckzyklen. Wenn die Goldbeschichtung auf den Pads abgenutzt ist, ändert sich die Impedanz, und die Platine sollte ersetzt werden.

F: Benötige ich für alle Vias ein Back-Drilling? A: Nicht für alle. Back-Drilling ist für Hochgeschwindigkeits-Signal-Vias erforderlich, um den ungenutzten "Stub"-Anteil zu entfernen, der als Antenne oder Kondensator wirkt. Masse-Stitching-Vias benötigen kein Back-Drilling.

F: Was ist der Kostenunterschied zwischen Standard- und Kalibrierungs-Leiterplatten? A: Kalibrierungs-Leiterplatten können 2-5x mehr kosten, aufgrund teurer Laminate, strengerer Toleranzkontrollen (±5% Impedanz) und fortgeschrittener Inspektionsanforderungen (TDR, Querschnittsanalyse).

F: Wie beeinflusst die Kupferrauheit die Kalibrierung? A: Bei hohen Frequenzen fließt der Strom auf der Oberfläche des Leiters. Raues Kupfer erhöht die effektive Pfadlänge, was den Widerstand und die Einfügedämpfung erhöht und somit die Kalibrierungsdaten verzerrt.

F: Kann ich einen Kalibrierungsgenerator und passive Standards auf einer Platine kombinieren? A: Ja, aber Isolation ist entscheidend. Stellen Sie sicher, dass die aktive Schaltung keine Störungen in die passiven Referenzleitungen einbringt. Verwenden Sie separate Masseflächen, die an einem einzigen Punkt (Sternmasse) verbunden sind.

F: Was ist der "Open"-Standard in einem Leiterplatten-Kalibrierkit? A: Es ist nicht nur eine unterbrochene Leiterbahn. Es muss ein entworfenes offenes Schaltkreis sein, das die Randkapazität am Ende der Leitung berücksichtigt. Diese Kapazität muss modelliert und dem VNA zur Verfügung gestellt werden.

F: Wie gebe ich das Material dem Hersteller an? A: Sagen Sie nicht einfach "Rogers". Geben Sie die genaue Serie (z.B. RO4350B), Dicke (z.B. 20 mil) und Kupfergewicht (z.B. 0,5 oz) an.

F: Warum ist die Länge der "Thru"-Leitung wichtig? A: Bei der TRL-Kalibrierung bestimmt die Länge der Leitung das Frequenzband, in dem die Kalibrierung gültig ist. Für eine Breitbandkalibrierung benötigen Sie möglicherweise mehrere Leitungen.

F: Beeinflusst die Lötstoppmaske die Impedanz? A: Ja. Die Lötstoppmaske fügt dielektrisches Material auf die Leiterbahn hinzu, wodurch die Impedanz um 2-3 Ohm gesenkt wird. Berechnungen müssen die Anwesenheit der Maske und ihren Dk berücksichtigen.

Verwandte Seiten & Tools

- Materialauswahl: Rogers PCB Materials

- Fertigungskapazitäten: PCB Manufacturing Services

- Design-Verifizierung: Free Gerber Viewer

Glossar (Schlüsselbegriffe)

| Begriff | Definition |

|---|---|

| SOLT | Short-Open-Load-Thru. Eine gängige Kalibrierungsmethode für VNAs, die vier bekannte Standards verwendet. |

| TRL | Thru-Reflect-Line. Eine hochpräzise Kalibrierungsmethode, die oft für On-Wafer- oder PCB-Messungen verwendet wird. |

| De-embedding | Der mathematische Prozess zur Entfernung der Effekte von Vorrichtungen oder Steckverbindern aus den Messdaten. |

| Charakteristische Impedanz | Das Verhältnis von Spannung zu Strom für eine Welle, die sich entlang einer Übertragungsleitung ausbreitet (üblicherweise 50Ω). |

| Rückflussdämpfung (S11) | Die Menge des Signals, das aufgrund von Impedanzfehlanpassung zur Quelle zurückreflektiert wird. |

| Einfügedämpfung (S21) | Die Menge des Signals, die verloren geht, wenn es durch die Übertragungsleitung läuft. |

| Skin-Effekt | Die Tendenz von hochfrequentem Wechselstrom, nahe der Oberfläche des Leiters zu fließen. |

| Dielektrische Absorption | Die Speicherung von Ladung durch das dielektrische Material, die Präzisionsmessungen beeinflussen kann. |

| Passermarke | Eine Kupfermarkierung, die von Bestückungsautomaten zur optischen Ausrichtung der Leiterplatte verwendet wird. |

| CTE | Wärmeausdehnungskoeffizient. Die Rate, mit der sich ein Material bei Erwärmung ausdehnt. |

| Rückbohren | Ein Fertigungsprozess zur Entfernung des ungenutzten Teils eines durchkontaktierten Lochs (Via-Stumpf). |

| Goldenes Muster | Eine als gut bekannte Referenz-Leiterplatte, die zur Validierung von Testsystemen verwendet wird. |

Fazit

Das Design einer Kalibrierungs-Leiterplatte ist eine Übung in Präzision. Jeder Mikrometer Kupfer und jeder Temperaturgrad beeinflusst das Ergebnis. Durch die Auswahl der richtigen Materialien, die Durchsetzung strenger Impedanzkontrollen und die Validierung mit TDR stellen Sie sicher, dass Ihre Testgeräte präzise bleiben.

Ob Sie einen kundenspezifischen Kalibrierungsgenerator oder ein passives Referenzkit bauen, APTPCB bietet die technische Unterstützung und Fertigungspräzision, die für Leiterplatten in Metrologiequalität erforderlich sind. Stellen Sie sicher, dass Ihre Spezifikationen klar sind, und überprüfen Sie Ihre Designdateien vor der Produktion, um kostspielige Iterationen zu minimieren.