Die kontrollierte Impedanz ist eine grundlegende Anforderung fuer Hochfrequenz-Leiterplatten, bei denen die Signallaengen mit den Leiterbahnlaengen vergleichbar werden und Uebertragungsleitungseffekte das Schaltungsverhalten dominieren. Impedanzfehlanpassungen verursachen Reflexionen, die die Signalintegritaet verschlechtern, die Effizienz der Leistungsvertragung verringern und Resonanzen erzeugen, die die Systemleistung beeintraechtigen. Das Erreichen und Aufrechterhalten einer praezisen Impedanzkontrolle erfordert abgestimmte Aufmerksamkeit fuer Materialien, Design und praezise Fertigungsprozesse.

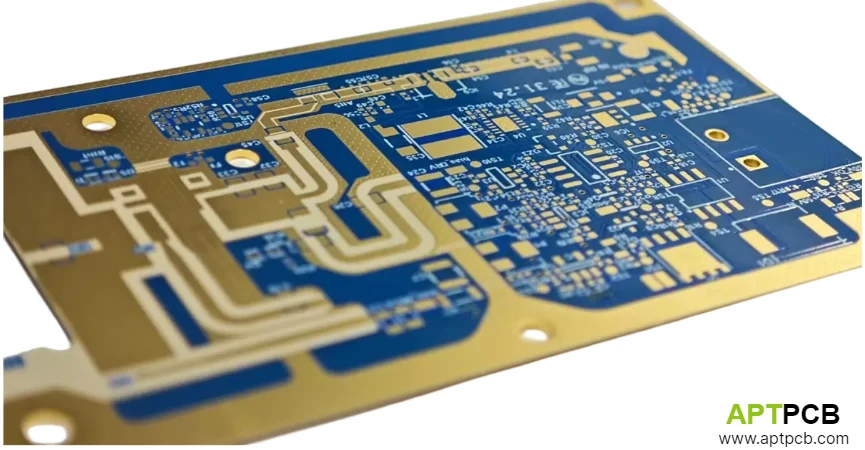

Bei APTPCB fertigen wir impedanzkontrollierte Hochfrequenz-Leiterplatten mit spezialisierter Expertise in praeziser Fertigung, enger Toleranzkontrolle und umfassender Verifikation. Unsere Faehigkeiten unterstuetzen RF-Hochfrequenz-Leiterplatten-Anwendungen, die eine Impedanztoleranz von ±5 % erfordern, mit validierten Fertigungsprozessen, die eine gleichbleibende Leistung sicherstellen.

Grundlagen von Uebertragungsleitungen verstehen

Die charakteristische Impedanz beschreibt die momentane Beziehung zwischen Spannung und Strom auf Uebertragungsleitungen und wird durch die verteilte Induktivitaet und Kapazitaet pro Laengeneinheit bestimmt. Das Verstehen der Impedanzgrundlagen leitet Designentscheidungen und Fertigungsanforderungen. Ein unzureichendes Verstaendnis der Impedanz fuehrt zu Designs, die Spezifikationen nicht erfuellen, zu Fertigungsprozessen, die Toleranzen nicht einhalten, oder zu Fehlanpassungsproblemen, die die Systemleistung beeintraechtigen - was sich direkt auf Produktfunktionalitaet und Zuverlaessigkeit auswirkt.

Bei APTPCB setzt unsere Fertigung die Theorie der Uebertragungsleitungen fuer eine praezise Impedanzkontrolle um.

Wichtige Konzepte zu Uebertragungsleitungen

- Charakteristische Impedanz: Z₀ = √(L/C) verknuepft verteilte Induktivitaet und Kapazitaet pro Laengeneinheit, bestimmt durch Leitergeometrie, Abstand zu Referenzebenen und dielektrische Eigenschaften.

- Reflexion und Anpassung: Impedanzspruenge verursachen Signalreflexionen, wobei der Reflexionskoeffizient die Schwere der Fehlanpassung quantifiziert und die Leistungsvertragung in Hochfrequenz-Mehrlagenleiterplatten-Aufbauten beeinflusst.

- Stehende Wellen und VSWR: Das Stehwellenverhaeltnis zeigt die Schwere der Fehlanpassung an; hoehere Werte erzeugen Belastungspunkte und verringern die Effizienz.

- Standard-Impedanzwerte: 50 Ohm fuer einseitige RF-Uebertragungsleitungen und 100 Ohm differentiell fuer High-Speed-Digitalanwendungen als praktische Industriestandards.

- Frequenzabhaengige Effekte: Skin-Effekt und Dispersion veraendern die effektive Impedanz bei sehr hohen Frequenzen und muessen bei Millimeterwellen-Designs beruecksichtigt werden.

- Temperatureffekte: Materialeigenschaftsaenderungen mit der Temperatur verursachen Impedanzschwankungen und muessen bei Anwendungen mit grossem Temperaturbereich beruecksichtigt werden.

Anwendung der Impedanzgrundlagen

Durch ein umfassendes Verstaendnis des Uebertragungsleitungsverhaltens, geeignete Designregeln und eine praezise Fertigung in Abstimmung mit den Impedanzanforderungen ermoeglicht APTPCB impedanzkontrollierte Leiterplatten, die anspruchsvolle Spezifikationen erfuellen.

Faktoren steuern, die die Impedanz beeinflussen

Mehrere Fertigungsparameter beeinflussen die erreichte Impedanz, darunter Leiterbahnbreite, Dielektrikumsdicke, Kupferdicke und Materialeigenschaften. Das Verstaendnis der Parametersensitivitaet lenkt die Prioritaeten der Prozesskontrolle in der Fertigung. Eine unzureichende Parameterkontrolle verursacht Impedanzschwankungen ausserhalb der Toleranz, inkonsistente Ergebnisse zwischen Produktionslosen oder die Unfaehigkeit, enge Spezifikationen zu erreichen - was sich direkt auf Produktqualitaet und Kundenzufriedenheit auswirkt.

Bei APTPCB kontrolliert unsere Fertigung alle Faktoren, die die Impedanz beeinflussen.

Wichtige Impedanzfaktoren

- Einfluss der Leiterbahnbreite: Primaere Designvariable, wobei breitere Leiterbahnen eine geringere Impedanz besitzen und eine enge Breitenkontrolle durch praezises Aetzen in der Hochfrequenz-Leiterplattenfertigung mit ±0,5 mil Toleranz erfordern.

- Einfluss der Dielektrikumsdicke: Ein duenneres Dielektrikum erhoeht die Kapazitaet und verringert die Impedanz; die Laminationskontrolle sorgt fuer eine gleichbleibende Dicke.

- Einfluss der Dielektrizitaetskonstanten: Eine hoehere Dielektrizitaetskonstante senkt die Impedanz; Materialauswahl und Charakterisierung stellen genaue Designberechnungen sicher.

- Einfluss der Kupferdicke: Sekundaerer Impedanzfaktor durch Veraenderungen der Induktivitaets- und Kapazitaetsverteilung, gesteuert ueber eine gleichmaessige Galvanisierung.

- Charakterisierung des Aetzfaktors: Trapezfoermige Leiterquerschnitte durch den Aetzprozess erfordern eine Kompensation, wobei die Prozesscharakterisierung vorhersehbare Aetzfaktoren festlegt.

- Kopplung benachbarter Leiterbahnen: Nahegelegene Leiterbahnen beeinflussen die effektive Impedanz und erfordern Mindestabstandsregeln, um Kopplungseffekte zu vermeiden.

Exzellenz bei der Parameterkontrolle

Durch die Kontrolle aller Impedanzfaktoren mittels praeziser Prozesse, Materialmanagement und statistischer Ueberwachung erreicht APTPCB eine Impedanzgenauigkeit, die anspruchsvolle Toleranzanforderungen erfuellt.

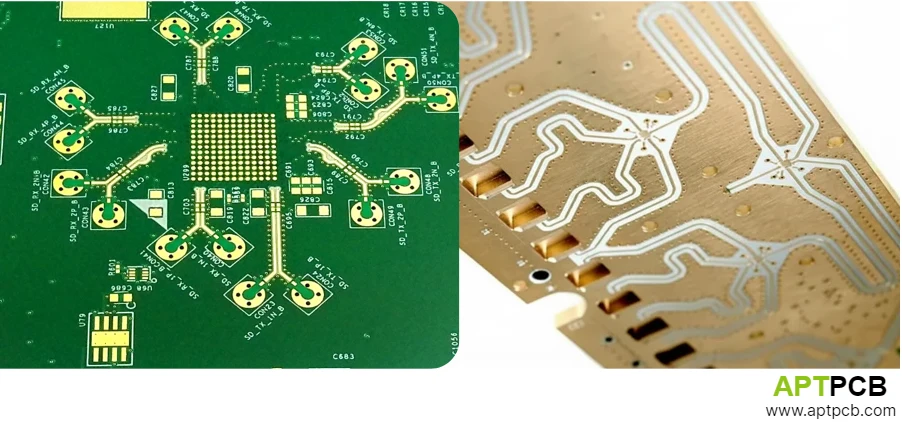

Designmethoden fuer die Impedanzkontrolle umsetzen

Das Design mit kontrollierter Impedanz basiert auf Feldloeseranalyse, Stackup-Planung und der Umsetzung von Designregeln, die Impedanzanforderungen in fertigungsgerechte Geometrien uebersetzen. Designmethoden muessen Fertigungstoleranzen und Materialschwankungen beruecksichtigen. Unzureichende Designmethoden fuehren dazu, dass erreichbare Impedanzen Zielwerte verfehlen, Toleranzketten Spezifikationen ueberschreiten oder Designs mit verfuegbaren Prozessen nicht herstellbar sind - was sich direkt auf den Entwicklungserfolg und die Markteinfuehrungszeit auswirkt.

Bei APTPCB unterstuetzt unser Engineering die Umsetzung impedanzkontrollierter Designs.

Wichtige Designfaehigkeiten

- Feldloeseranalyse: Zweidimensionale elektromagnetische Analyse zur genauen Berechnung der Impedanz aus festgelegten Geometrien mit parametrisierter Untersuchung von Variationen durch die technische Unterstuetzung unseres Hochfrequenz-Leiterplattenherstellers.

- Stackup-Planung: Lagenkonfiguration, die Impedanzanforderungen, Routing-Bedarf und Fertigungsgrenzen ausbalanciert, wobei Zielimpedanzen die zulaessigen Dielektrikumsdicken begrenzen.

- Design differentieller Paare: Edge-coupled oder broadside-coupled differentielle Paare mit kontrollierter Kopplung zur Aufrechterhaltung der Differenzialimpedanz durch gleichbleibenden Abstand.

- Optimierung von Via-Uebergaengen: Anti-Pad-Groessen, Via-Durchmesser und Masse-Via-Platzierung zur Minimierung von Diskontinuitaeten in impedanzkontrollierten Pfaden.

- Toleranzanalyse: Statistische Analyse zur Vorhersage von Impedanzschwankungen aus Fertigungstoleranzen, die Designmargen steuert.

- Dokumentation von Designregeln: Klare Spezifikation von Impedanzzielen, Toleranzen und Coupon-Anforderungen, damit die Fertigung die Anforderungen eindeutig versteht.

Exzellenz in der Designunterstuetzung

Durch Feldloeser-Faehigkeiten, Stackup-Expertise und eine mit den Fertigungsmoeglichkeiten abgestimmte Designunterstuetzung ermoeglicht APTPCB impedanzkontrollierte Designs, die ihre Zielwerte innerhalb der Toleranz erreichen.

Fertigungspraezision fuer die Impedanz erreichen

Die Fertigung mit kontrollierter Impedanz erfordert eine enge Kontrolle der Leiterbahnbreite, eine gleichbleibende Dielektrikumsdicke und eine gleichmaessige Galvanisierung, um die spezifizierten Toleranzen zu erreichen. Unterschiedliche Toleranzniveaus erfordern unterschiedliche Prozessfaehigkeiten. Unzureichende Fertigungspraezision verursacht Impedanzen ausserhalb der Spezifikation, uebermaessige Schwankungen zwischen Leiterplatten oder die Unfaehigkeit, engere Toleranzen zu erreichen - was sich direkt auf Ausbeute und Kundenanforderungen auswirkt.

Bei APTPCB setzt unsere Fertigung praezise Kontrollen fuer die Impedanzgenauigkeit um.

Wichtige Fertigungskontrollen

- Praezise Leiterbahnbreite: Direktbelichtung und kontrolliertes Aetzen erreichen Breitentoleranzen bis ±0,5 mil mit statistischer Ueberwachung der Dimensionsergebnisse in RF-Leiterplattenfertigungsprozessen.

- Kontrolle der Dielektrikumsdicke: Laminationsprozesse erzielen eine gleichbleibende Dicke, wobei Kupferausgleich Schwankungen durch unterschiedlichen Prepreg-Fluss verringert.

- Aetzkompensation: Anpassung der Artwork-Abmessungen an den erwarteten Aetzfaktor, zugeschnitten auf Material- und Kupfergewichtskombinationen.

- Gleichmaessige Galvanisierung: Kontrolle der Kupferdicke innerhalb von ±10 %, was sowohl die Impedanz als auch die Via-Zuverlaessigkeit beeinflusst; Pulsplattierung verbessert die Verteilung.

- Prozesscharakterisierung: Statistische Daten legen erreichbare Toleranzen fuer jede Material- und Prozesskombination fest und ermoeglichen eine genaue Kalkulation.

- Erreichbare Toleranzen: Standard ±10 %, verbessert ±7 % und Premium ±5 % Impedanztoleranzfaehigkeiten mit darauf abgestimmten Prozesskontrollen.

Exzellenz in der Fertigungspraezision

Durch die Umsetzung praeziser Prozesse, statistischer Kontrolle und kontinuierlicher Verbesserung auf Basis der Prozesscharakterisierung erreicht APTPCB eine Fertigungsgenauigkeit, die impedanzkontrollierte Leiterplatten fuer anspruchsvolle Toleranzspezifikationen ermoeglicht.

Impedanz durch umfassende Tests verifizieren

Die Produktionsverifikation der Impedanz mit Testcoupons bestaetigt die erreichten Werte, waehrend statistische Analysen die Prozesskontrolle unterstuetzen. Coupon-Design, Messverfahren und Datenauswertung bestimmen die Wirksamkeit der Verifikation. Unzureichende Verifikation uebersieht Impedanzprobleme, liefert ungenaue Daten fuer die Prozesssteuerung oder bietet keine Dokumentation zur Unterstuetzung von Kundenanforderungen - was sich auf Produktqualitaet und Kundenvertrauen auswirkt.

Bei APTPCB bietet unsere Pruefung eine umfassende Impedanzverifikation.

Wichtige Verifikationsfaehigkeiten

- TDR-Messung: Zeitbereichsreflektometrie misst die charakteristische Impedanz entlang von Uebertragungsleitungs-Teststrukturen mit kalibrierten Geraeten und stellt die Genauigkeit ueber Testing und Qualitaet-Protokolle sicher.

- Coupon-Design: Teststrukturen repraesentieren die tatsaechlichen Produktgeometrien, wobei Linienbreiten, Abstaende und Stackup-Positionen den impedanzkontrollierten Leiterbahnen im Design entsprechen.

- Mehrere Coupon-Positionen: Coupons werden ueber die Panelflaeche verteilt platziert, um die Gleichmaessigkeit offenzulegen; statistische Analyse der Coupon-Daten unterstuetzt die Prozesskontrolle.

- Testen differentieller Paare: Messung der ungeraden und geraden Modenimpedanz fuer differentielle Paare bestaetigt sowohl einseitige als auch differentielle Werte.

- Statistische Berichterstattung: Mittelwert-, Standardabweichungs- und Cpk-Daten dokumentieren die Prozessfaehigkeit; Trendanalysen identifizieren Drift, die Aufmerksamkeit erfordert.

- Korrelationsvalidierung: Vergleich zwischen Coupon-Messungen und Produktleistung validiert den Testansatz bei laufender Ueberwachung.

Exzellenz in der Verifikation

Durch umfassende Impedanztests, kalibrierte Ausruestung und systematische Datenauswertung in Abstimmung mit den Qualitaetsanforderungen validiert APTPCB die Leistung impedanzkontrollierter Leiterplatten gemaess den Kundenspezifikationen.

Anwendungsbezogene Anforderungen unterstuetzen

Unterschiedliche Anwendungen stellen unterschiedliche Anforderungen an die kontrollierte Impedanz - von digitalen Protokollen mit festgelegten Werten bis zu RF-Systemen, die eine praezise Anpassung erfordern. Das Verstehen des Anwendungskontexts leitet geeignete Toleranzspezifikationen und Verifikationsansaetze. Ein unzureichendes Anwendungsverstaendnis fuehrt zu Ueberspezifikation mit hoeheren Kosten, Unterspezifikation mit Leistungsrisiken oder ungeeigneten Verifikationsmethoden - was sich auf Produkteignung und Wirtschaftlichkeit auswirkt.

Bei APTPCB unterstuetzt unsere Fertigung vielfaeltige impedanzkontrollierte Anwendungen.

Wichtige Anwendungsbereiche

High-Speed-Digitalschnittstellen

- PCIe, USB, HDMI und andere Protokolle mit festgelegten Impedanzwerten und Toleranzen fuer eine zuverlaessige Signaluebertragung.

- DDR-Speicherschnittstellen, die fuer die Signalintegritaet bei hohen Datenraten eine kontrollierte Impedanz erfordern.

- Ethernet- und Netzwerkschnittstellen mit spezifizierter Impedanz fuer korrekte Abschlussanpassung.

- LVDS und andere differentielle Signalverfahren, die eine praezise Differenzialimpedanz fuer digitale Hochfrequenz-Mehrlagenleiterplatten-Anwendungen erfordern.

RF- und Mikrowellensysteme

- 50-Ohm-Uebertragungsleitungen als Standard fuer RF-Systeme mit enger Toleranz fuer die Leistung von Anpassungsnetzwerken durch die Faehigkeiten von Mikrowellen-RF-Leiterplatten.

- Phased-Array-Systeme, die ueber Produktionsvolumina hinweg eine gleichbleibende Impedanz fuer die Array-Kalibrierung erfordern.

- Filter- und Anpassungsnetzwerke, deren Funktion kritisch von Abschlussimpedanzen abhaengt.

- Testgeraete, die fuer genaue Messungen eine praezise Impedanz benoetigen.

Mixed-Signal-Anwendungen

- Kombination digitaler Schnittstellen mit RF-Schaltungen auf einer Leiterplatte mit angemessener Impedanzkontrolle fuer jeden Bereich.

- Medizinische Geraete, die eine zuverlaessige Signaluebertragung ueber impedanzkontrollierte Pfade erfordern.

- Industrieanlagen mit High-Speed-Digital- und Analogschaltungen, die Isolation und Impedanzkontrolle erfordern.

Exzellenz in der Anwendungsunterstuetzung

Durch Anwendungsverstaendnis, geeignete Toleranzfestlegung und eine an den Anforderungen ausgerichtete Verifikation liefert APTPCB impedanzkontrollierte Leiterplatten, die vielfaeltige Anwendungsbeduerfnisse erfuellen.

Impedanzdiskontinuitaeten beherrschen

Reale Leiterplatten-Designs enthalten trotz bester Kontrollbemuehungen Impedanzdiskontinuitaeten durch Via-Uebergaenge, Steckverbinderschnittstellen und Bauteilanschluesse. Kumulative Diskontinuitaetseffekte beeintraechtigen die Systemleistung und erfordern Designstrategien sowie Fertigungspraezision, um diese Auswirkungen zu minimieren. Eine unzureichende Beherrschung von Diskontinuitaeten verursacht Reflexionen, die die Signalintegritaet verschlechtern, Resonanzen, die den Frequenzgang beeintraechtigen, oder uebermaessigen Rueckflussverlust - was sich direkt auf die Schaltungsleistung auswirkt.

Bei APTPCB unterstuetzt unsere Fertigung Strategien zur Minimierung von Diskontinuitaeten.

Wichtige Faehigkeiten zum Umgang mit Diskontinuitaeten

- Optimierung von Via-Uebergaengen: Anti-Pad-Groessen, Via-Durchmesser und Masse-Via-Platzierung minimieren Uebergangsdiskontinuitaeten durch Designpraktiken fuer verlustarme Hochfrequenz-Leiterplatten.

- Backdrilling: Tiefenkontrolliertes Bohren entfernt Via-Stubs und verhindert Resonanzen durch ungenutzte Teile des Via-Zylinders.

- Steckverbinder-Launch-Design: Praezise Fertigung der Geometrien an der Steckverbinderschnittstelle zur Aufrechterhaltung der Impedanzkontinuitaet.

- Taper-Uebergaenge: Allmaehliche Impedanzuebergaenge zwischen Abschnitten mit unterschiedlicher charakteristischer Impedanz, wenn erforderlich.

- Kompensationsstrukturen: Fertigung von Kompensationsgeometrien zum Ausgleich der Reaktanz von Diskontinuitaeten.

- Zeitbereichsanalyse: TDR-Messung zeigt Positionen und Groessen von Diskontinuitaeten zur Validierung der Optimierung.

Exzellenz im Umgang mit Diskontinuitaeten

Durch die Unterstuetzung optimierter Uebergangsdesigns, praeziser Fertigung und Verifikation mittels TDR-Analyse ermoeglicht APTPCB impedanzkontrollierte Leiterplatten, die die Auswirkungen von Diskontinuitaeten auf die Systemleistung minimieren.