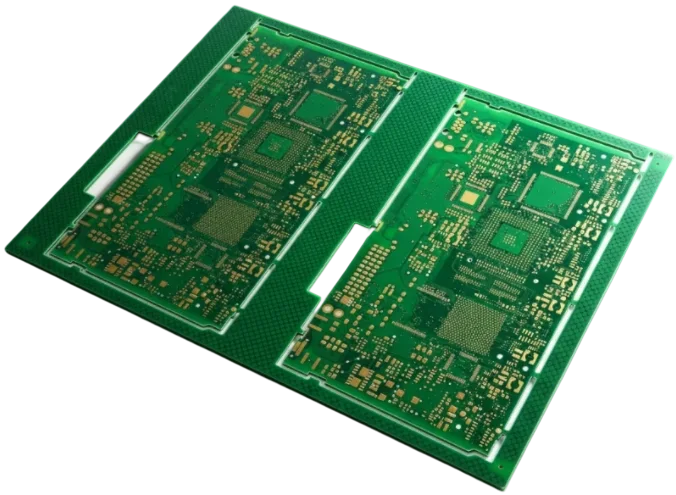

Die elektronische Kriegsführung hat sich von einfachem Rauschstören zu ausgeklügelter, adaptiver Signalmanipulation entwickelt. In diesem risikoreichen Umfeld muss die Hardware so widerstandsfähig sein wie die Software. Die ECCM-Leiterplatte (Electronic Counter-Countermeasures Printed Circuit Board) ist die physische Grundlage von Systemen, die darauf ausgelegt sind, Störungen zu widerstehen und die Kommunikationsintegrität unter Beschuss aufrechtzuerhalten.

Für Ingenieure und Beschaffungsteams erfordert die Herstellung dieser Platinen mehr als Standard-FR4-Prozesse. Sie erfordert eine strikte Einhaltung von Signalintegrität, Wärmemanagement und Materialstabilität. APTPCB (APTPCB PCB Factory) ist auf diese hochzuverlässigen Verbindungen spezialisiert und stellt sicher, dass die Designabsicht perfekt auf dem Schlachtfeld umgesetzt wird.

Wichtige Erkenntnisse für ECCM-Leiterplatten

- Definition: ECCM-Leiterplatten sind spezialisierte Leiterplatten, die entwickelt wurden, um Rauschen zu filtern, Störungen zu widerstehen und die Signalintegrität in feindlichen elektromagnetischen Umgebungen aufrechtzuerhalten.

- Materialkritikalität: Standard-FR4 ist selten ausreichend; verlustarme Materialien (PTFE, Keramik) sind unerlässlich, um Signalphase und -amplitude zu erhalten.

- Signalintegrität: Kontrollierte Impedanz und enge Toleranzen bei der Leiterbahnbreite sind nicht verhandelbar, um Signalreflexionen zu verhindern.

- Wärmemanagement: Hochleistungs-Anti-Jamming-Übertragung erfordert fortschrittliche Wärmeableitungstechniken wie Metallkerne oder Coin-Insertion.

- Validierung: Die Prüfung geht über die elektrische Konnektivität hinaus und umfasst TDR (Zeitbereichsreflektometrie) und Umgebungsbelastungstests.

- Partnerschaft: Der Erfolg hängt von einem frühen DFM-Engagement mit einem Hersteller ab, der Erfahrung mit IPC Klasse 3 Standards hat.

Was ECCM-Leiterplatten wirklich bedeuten (Umfang & Grenzen)

Während die wichtigsten Erkenntnisse die Bedeutung von Materialien und Tests hervorheben, ist das Verständnis des operativen Umfangs einer ECCM-Leiterplatte der erste Schritt zu einer erfolgreichen Fertigung.

ECCM bezieht sich auf die Techniken, die verwendet werden, um die effektive Nutzung des elektromagnetischen Spektrums trotz des Einsatzes elektronischer Gegenmaßnahmen (ECM) durch den Gegner sicherzustellen. Daher ist eine ECCM-Leiterplatte kein spezifischer "Typ" von Leiterplatte wie eine starre oder flexible Leiterplatte, sondern vielmehr eine Leistungsklasse von Leiterplatten. Diese Leiterplatten sind das Rückgrat von Gefechtsführungs-Leiterplattensystemen und Kommando- und Kontroll-Leiterplatteneinheiten, bei denen ein verlorenes Signal Missionsversagen bedeuten kann.

Der Umfang der ECCM-Leiterplattenfertigung umfasst:

- Frequenzagilität: Die Leiterplatte muss schnelles Frequenzspringen ohne Signalverschlechterung unterstützen.

- Niedriger Rauschpegel: Das Laminat und das Layout müssen internes Übersprechen minimieren, damit schwache eingehende Signale von Störrauschen unterschieden werden können.

- Physische Haltbarkeit: Diese Leiterplatten befinden sich oft in Raketen, Kampfflugzeugen oder mobilen Bodeneinheiten und erfordern Beständigkeit gegen hohe G-Kräfte und extreme Temperaturen. Im Gegensatz zur Unterhaltungselektronik, wo die Kosten der Haupttreiber sind, ist hier der Haupttreiber die Überlebensfähigkeit.

ECCM-Leiterplatten-Metriken, die wichtig sind (wie man Qualität bewertet)

Sobald der operative Umfang definiert ist, müssen wir die Leistung anhand spezifischer Fertigungs- und Materialmetriken quantifizieren.

Die folgende Tabelle skizziert die kritischen Parameter, die APTPCB während der Herstellung von ECCM-tauglichen Leiterplatten überwacht.

| Metrik | Warum es wichtig ist | Typischer Bereich / Faktor | Wie man misst |

|---|---|---|---|

| Dielektrizitätskonstante (Dk) | Bestimmt die Signalpropagationsgeschwindigkeit. Variationen verursachen Timing-Fehler in Phased-Array-Antennen. | 2,2 bis 3,5 (Stabil über Frequenz) | IPC-TM-650 2.5.5.5 |

| Verlustfaktor (Df) | Misst, wie viel Signal als Wärme verloren geht. Niedriger ist besser für die Erkennung schwacher Signale. | < 0,002 (Geringer Verlust) | Hohlraumresonator-Methode |

| WAK (Z-Achse) | Wärmeausdehnungskoeffizient. Hoher WAK führt zu Durchkontaktierungsversagen während des thermischen Zyklierens. | < 50 ppm/°C (unter Tg) | TMA (Thermomechanische Analyse) |

| Impedanztoleranz | Fehlanpassungen verursachen Reflexionen, was die Wirksamkeit von Anti-Jamming-Filtern reduziert. | ±5% oder ±7% | TDR (Zeitbereichsreflektometrie) |

| Schälfestigkeit | Stellt sicher, dass Leiterbahnen unter hoher thermischer Belastung oder Vibration nicht abheben. | > 1,05 N/mm | IPC-TM-650 2.4.8 |

| Feuchtigkeitsaufnahme | Wasser verändert Dk/Df. Hohe Absorption beeinträchtigt die Hochfrequenzleistung. | < 0,02% | Immersion / Gewichtstest |

Auswahlhilfe nach Szenario (Kompromisse)

Metriken liefern die Rohdaten, aber die spezifische Anwendungsumgebung bestimmt, welche Kompromisse während des Auswahlprozesses akzeptabel sind.

Verschiedene Verteidigungsszenarien erfordern die Priorisierung unterschiedlicher Attribute. Im Folgenden finden Sie gängige Szenarien und wie Sie die richtige Leiterplattenkonfiguration auswählen.

1. Airborne-Radar- und Störsender-Pods

- Priorität: Gewichtsreduzierung und Hochfrequenzleistung.

- Kompromiss: Höhere Kosten für Spezialmaterialien.

- Empfehlung: Verwenden Sie Hochfrequenz-Leiterplattenmaterialien wie Rogers oder Taconic. Implementieren Sie ein Starrflex-Design, um schwere Verkabelungen und Steckverbinder zu eliminieren.

2. Marine-Kommando- und Kontrollsysteme

- Priorität: Korrosionsbeständigkeit und Langzeitverlässigkeit.

- Kompromiss: Langsamere Signalgeschwindigkeit (wenn die Schutzschicht zu dick ist) vs. Schutz.

- Empfehlung: Priorisieren Sie Oberflächenveredelungen wie ENIG oder ENEPIG. Verwenden Sie eine robuste Schutzschicht oder Vergussmasse. Stellen Sie sicher, dass der Lagenaufbau hohe Luftfeuchtigkeit ohne Delamination bewältigt.

3. Tragbare taktische Funkgeräte

- Priorität: Miniaturisierung und Batterieeffizienz.

- Kompromiss: Fertigungskomplexität vs. Größe.

- Empfehlung: Nutzen Sie die HDI-Leiterplattentechnologie mit Blind- und Buried-Vias, um das Layout zu verdichten. Dies reduziert den physischen Platzbedarf und erhält gleichzeitig die Signalintegrität für sichere Kommunikation.

4. Hochleistungs-Bodenstörsender

- Priorität: Wärmeableitung.

- Kompromiss: Platinendicke und -gewicht vs. Kühlung.

- Empfehlung: Verwenden Sie Metallkern-Leiterplatten (MCPCB) oder schwere Kupferleiterbahnen. Betten Sie Kupfermünzen direkt unter Hochleistungs-HF-Verstärker ein, um die Wärme sofort abzuleiten.

5. Raketenleitsysteme (Einweg)

- Priorität: Extreme Stoßfestigkeit und Kurzzeit-Zuverlässigkeit.

- Kompromiss: Langlebigkeit (nicht erforderlich) vs. mechanische Robustheit.

- Empfehlung: Konzentrieren Sie sich auf die Durchkontaktierungszuverlässigkeit (Beschichtungsdicke der Klasse 3). Verwenden Sie Materialien mit einer hohen Glasübergangstemperatur (Tg), um die intensive Startwärme zu überstehen.

6. Satelliten- / Weltraumgestütztes ECCM

- Priorität: Geringe Ausgasung und Strahlungshärte.

- Kompromiss: Extrem begrenzte Materialauswahl.

- Empfehlung: Wählen Sie Materialien, die speziell für den Weltraum zugelassen sind (geringe Ausgasung). Vermeiden Sie Standard-Lötstopplacke, die im Vakuum verdampfen können.

ECCM-Leiterplatten-Implementierungs-Checkpoints (Design bis Fertigung)

Die Wahl des richtigen Ansatzes ist nur der erste Schritt; eine rigorose Ausführung durch spezifische Checkpoints stellt sicher, dass die endgültige ECCM-Leiterplatte wie simuliert funktioniert.

APTPCB empfiehlt die folgende Checkpoint-Liste für Designer, die von CAD zu CAM wechseln.

1. Materialverfügbarkeitsprüfung

- Empfehlung: Bestätigen Sie die Lieferzeiten für spezialisierte HF-Laminate (z.B. Rogers 4000-Serie), bevor Sie das Layout finalisieren.

- Risiko: Die Entwicklung um ein Material mit einer Lieferzeit von 20 Wochen kann das Projekt verzögern.

- Akzeptanz: Bestätigungs-E-Mail des Lieferanten oder Lagerbestandsprüfung.

2. Stapelverifizierung

- Empfehlung: Kupferverteilung ausgleichen, um Verzug zu vermeiden. Sicherstellen, dass Prepreg-Schichten eine ausreichende Harzfüllung für Designs mit hohem Kupferanteil bieten.

- Risiko: Probleme mit Verbiegung und Verdrehung während der Montage; Impedanzfehlanpassungen.

- Akzeptanz: Simulationsbericht, der den Stapelfähigkeiten des Herstellers entspricht.

3. Leiterbahnbreite & -abstand (Ätzkompensation)

- Empfehlung: Ätzfaktoren berücksichtigen. HF-Leitungen sind empfindlich; der Hersteller muss eine Kompensation auf die Gerber-Dateien anwenden.

- Risiko: Die endgültige Leiterbahnbreite ist zu schmal, was die Impedanz und den Einfügungsverlust erhöht.

- Akzeptanz: Genehmigung der CAM-Engineering-Anfrage (EQ).

4. Via-Struktur & Rückbohren

- Empfehlung: Rückbohren für Hochgeschwindigkeitssignale (>10 Gbit/s) verwenden, um Stubs zu entfernen, die als Antennen wirken.

- Risiko: Signalreflexions- und Resonanzprobleme.

- Akzeptanz: Querschnittsanalyse (Mikroschliff), die die Entfernung des Stubs zeigt.

5. Auswahl der Oberflächenveredelung

- Empfehlung: ENIG (Chemisch Nickel/Immersionsgold) oder Immersionssilber für flache Oberflächen und gute Leitfähigkeit verwenden. HASL für Fine-Pitch- oder Hochfrequenzplatinen vermeiden.

- Risiko: Ungleichmäßige Pads, die die BGA-Montage beeinträchtigen; Signalverlust bei Skin-Effekt-Frequenzen.

- Akzeptanz: Sichtprüfung und Dickenmessung (Röntgen).

6. Abschirmung & Erdung

- Empfehlung: Implementierung durch Via-Stitching (Einzäunung) um HF-Leitungen herum, um elektromagnetische Felder einzudämmen.

- Risiko: Übersprechen zwischen Kanälen, wodurch die ECCM-Fähigkeiten beeinträchtigt werden.

- Akzeptanz: Design Rule Check (DRC) für Via-Abstand < 1/20 der Wellenlänge.

7. Thermischer Stresstest

- Empfehlung: Durchführung mehrerer Reflow-Simulationen.

- Risiko: Delamination von Hybrid-Lagenaufbauten (z.B. FR4 verbunden mit PTFE).

- Akzeptanz: IPC-TM-650 2.6.6 (Thermoschock).

8. Elektrische Endprüfung

- Empfehlung: 100% Netlist-Test plus TDR zur Impedanzkontrolle.

- Risiko: Offene/kurze Schaltkreise oder Impedanzen außerhalb der Spezifikation, die in die Montage gelangen.

- Akzeptanz: Konformitätszertifikat (CoC) mit TDR-Protokollen.

Häufige Fehler bei ECCM-Leiterplatten (und der richtige Ansatz)

Selbst mit einem soliden Plan und einer Checkliste können spezifische Fallstricke ECCM-Leiterplattenprojekte während der NPI-Phase (New Product Introduction) oft zum Scheitern bringen.

1. Ignorieren der CTE-Fehlanpassung von Hybrid-Lagenaufbauten

- Fehler: Mischen von FR4- und PTFE-Materialien, ohne deren unterschiedliche Ausdehnungsraten (CTE) zu berücksichtigen.

- Ergebnis: Delamination oder Brüche von durchkontaktierten Löchern (PTH) während des Reflow-Prozesses.

- Korrektur: Verwenden Sie "Spread Glass" oder spezielle Haftfolien, die von Aerospace Defense PCB-Experten empfohlen werden, um den Stress abzufedern.

2. Übermäßige Spezifikation von Toleranzen

- Fehler: Anforderung einer Impedanztoleranz von ±1 %, obwohl ±5 % ausreichend und herstellbar wären.

- Ergebnis: Explodierende Kosten und geringe Ausbeute.

- Korrektur: Konsultieren Sie den Hersteller bezüglich der Standardfähigkeiten (typischerweise ±5 % bis ±10 %) und entwerfen Sie die Schaltung so, dass sie geringfügige Abweichungen handhaben kann.

3. Vernachlässigung des „Skin-Effekts“

- Fehler: Verwendung von Standard-Kupferrauheit für sehr hochfrequente Leitungen.

- Ergebnis: Erhöhte Einfügedämpfung, da das Signal entlang der rauen Oberfläche des Kupfers wandert.

- Korrektur: Spezifizieren Sie „Low Profile“ oder „Very Low Profile“ (VLP) Kupferfolie für HF-Schichten.

4. Schlechte thermische Pfade für Abschirmungen

- Fehler: Platzierung von HF-Metallabschirmungen ohne ausreichende Massevias darunter.

- Ergebnis: Die Abschirmung heizt sich auf und strahlt Energie ab, anstatt sie zu erden.

- Korrektur: Entwerfen Sie einen robusten Massering mit dichter Via-Vernähung an der Stelle, wo die Abschirmung gelötet wird.

5. Sich nur auf Dk-Werte aus dem Datenblatt verlassen

- Fehler: Verwendung des „Design Dk“ aus einem Datenblatt ohne Berücksichtigung der Frequenz.

- Ergebnis: Der tatsächliche Dk bei 10 GHz unterscheidet sich vom Dk bei 1 MHz, was zu Phasenverschiebungen führt.

- Korrektur: Fordern Sie Dk-Werte speziell für Ihre Betriebsfrequenz vom Laminatlieferanten an (z. B. Rogers PCB-Materialien).

6. Unzureichende Fiducials für die Bestückung

- Fehler: Weglassen von Fiducials auf hochdichten Leiterplatten.

- Ergebnis: Bestückungsautomaten können Fine-Pitch-Bauteile nicht präzise ausrichten.

- Korrektur: Globale und lokale Fiducials einbeziehen, insbesondere in der Nähe von BGA- und QFN-Komponenten.

ECCM-Leiterplatten-FAQ (Kosten, Lieferzeit, DFM-Dateien, Lagenaufbau, Impedanz, Dielektrizitätskonstante (DK)/Verlustfaktor (DF))

F: Was ist der Unterschied zwischen einer Standard-Leiterplatte und einer ECCM-Leiterplatte? A: ECCM-Leiterplatten priorisieren Signalintegrität, geringe Verluste und Anti-Jamming-Fähigkeiten durch den Einsatz fortschrittlicher Materialien (PTFE/Keramik) und engere Fertigungstoleranzen, während Standard-Leiterplatten sich auf Konnektivität und Kosten konzentrieren.

F: Kann ich FR4 für ECCM-Anwendungen verwenden? A: Im Allgemeinen nein. Standard-FR4 hat einen hohen Verlustfaktor (Df), der bei hohen Frequenzen zu Signalverlusten führt. Hochleistungs-FR4 (High-Tg, Low-Loss) könnte jedoch für Nicht-HF-Lagen in einem Hybrid-Lagenaufbau verwendet werden.

F: Welche Oberflächenveredelung ist am besten für Hochfrequenz-ECCM-Leiterplatten geeignet? A: Tauchsilber (Immersion Silver) oder ENIG werden bevorzugt. Tauchsilber bietet die beste Leitfähigkeit für Hochfrequenzsignale (reduziert Skin-Effekt-Verluste), während ENIG eine ausgezeichnete Planarität und Oxidationsbeständigkeit bietet.

F: Wie geht APTPCB mit Hybrid-Lagenaufbauten um? A: Wir verwenden spezialisierte Laminierungszyklen, die den unterschiedlichen Aushärtungstemperaturen und -drücken Rechnung tragen, die für ungleiche Materialien (z. B. das Verkleben von Teflon mit FR4) erforderlich sind.

F: Was ist die typische Lieferzeit für eine ECCM-Leiterplatte? A: Dies hängt von der Materialverfügbarkeit ab. Werden Lagerlaminate verwendet, beträgt die Lieferzeit 5-10 Tage. Müssen spezialisierte Rogers- oder Taconic-Materialien bestellt werden, kann es 3-4 Wochen dauern.

F: Unterstützen Sie IPC Klasse 3 Standards? A: Ja, die meisten Verteidigungs- und Luft- und Raumfahrtanwendungen, einschließlich Leiterplatten für Gefechtsführung, erfordern IPC Klasse 3, die strengere Kriterien für Schichtdicke, Ringflächen und visuelle Mängel vorschreibt.

Q: Welche Daten werden für ein Angebot mit kontrollierter Impedanz benötigt? A: Wir benötigen die Zielimpedanz (z.B. 50Ω), die beteiligten spezifischen Lagen, die Beschränkungen für Leiterbahnbreite/-abstand und den bevorzugten Materialsatz.

Q: Wie testen Sie die Signalintegrität? A: Wir verwenden TDR (Zeitbereichsreflektometrie)-Coupons, die auf dem Produktionspanel enthalten sind, um die tatsächliche Impedanz der Leiterbahnen zu messen und sicherzustellen, dass sie den Designspezifikationen entsprechen.

ECCM Leiterplatten-Glossar (Schlüsselbegriffe)

| Begriff | Definition |

|---|---|

| ECCM | Elektronische Gegen-Gegenmaßnahmen. Techniken zur Sicherstellung der effektiven Nutzung des elektromagnetischen Spektrums trotz feindlicher Störung. |

| ECM | Elektronische Gegenmaßnahmen. Maßnahmen, die ergriffen werden, um die effektive Nutzung des elektromagnetischen Spektrums durch einen Feind zu verhindern oder zu reduzieren (Störung). |

| Dk (Dielektrizitätskonstante) | Ein Maß für die Fähigkeit eines Materials, elektrische Energie in einem elektrischen Feld zu speichern. Beeinflusst die Signalgeschwindigkeit. |

| Df (Verlustfaktor) | Ein Maß für die Verlustrate der Leistung eines elektrischen Modus in einem dissipativen System. Niedriger ist besser für HF. |

| Hybrid-Lagenaufbau | Ein Leiterplatten-Lagenaufbau, der zwei oder mehr verschiedene Arten von Laminatmaterialien verwendet (z.B. FR4 + Rogers). |

| Rückbohren | Der Prozess des Ausbohrens des ungenutzten Teils eines durchkontaktierten Lochs (Stummel), um Signalreflexionen zu reduzieren. |

| Skin-Effekt | Die Tendenz von hochfrequentem Wechselstrom, sich nahe der Oberfläche des Leiters zu verteilen. |

| WAK (Wärmeausdehnungskoeffizient) | Wie stark sich ein Material beim Erhitzen ausdehnt. Ungleichheiten verursachen Zuverlässigkeitsprobleme. |

| TDR (Zeitbereichsreflektometrie) | Eine Messtechnik zur Bestimmung der Impedanz einer Leiterbahn. |

| IPC Klasse 3 | Die höchste Leistungsklasse für die Leiterplattenfertigung, vorgesehen für hochzuverlässige Produkte, bei denen Ausfallzeiten nicht akzeptabel sind. |

| Vias (Blind/Vergraben) | Blindvias verbinden eine äußere Lage mit einer inneren Lage; vergrabene Vias verbinden nur innere Lagen. Werden in HDI verwendet. |

| Fiducial-Marke | Eine Kupfermarkierung auf der Leiterplatte, die von Bestückungsautomaten zur optischen Ausrichtung verwendet wird. |

Fazit: ECCM-Leiterplatte – nächste Schritte

Die Herstellung einer ECCM-Leiterplatte ist eine Disziplin, die Materialwissenschaft mit Präzisionstechnik verbindet. Ob die Anwendung eine Gefechtsführungs-Leiterplatte für ein Marineschiff oder eine Befehls- und Steuerungs-Leiterplatte für eine mobile Bodeneinheit ist, das Ziel bleibt dasselbe: absolute Signalrobustheit in einer chaotischen Umgebung.

Um sicherzustellen, dass Ihr Projekt reibungslos vom Konzept bis zum Einsatz verläuft, ist eine frühzeitige Validierung entscheidend. Wenn Sie bereit sind fortzufahren, bereiten Sie Ihre Gerber-Dateien, Lagenaufbauanforderungen und IPC-Klassenspezifikationen vor.

Bereit zur Fertigung? Kontaktieren Sie APTPCB für eine umfassende DFM-Überprüfung. Wir werden Ihr Design auf Materialkompatibilität, Impedanzkontrolle und Herstellbarkeit analysieren, um sicherzustellen, dass Ihre Verteidigungselektronik genau wie erforderlich funktioniert.