Hochleistungsrechnen erfordert schnellere Datenübertragungsraten zwischen heterogenen Chips, wodurch die EMIB-Interconnect-Board-Impedanzkontrolle zu einem kritischen Faktor in der modernen Halbleitergehäusefertigung wird. Da Designs sich in Richtung 2.5D-Packaging und Chiplet-Architekturen entwickeln, verschwimmen die traditionellen Grenzen zwischen der Leiterplatte (PCB) und dem Gehäusesubstrat. Die Sicherstellung der Signalintegrität über die eingebettete Brücke und das umgebende organische Substrat erfordert eine präzise Fertigungsausführung. Dieser Leitfaden bietet einen umfassenden Workflow für Ingenieure und Beschaffungsteams, um die Impedanz in diesen fortschrittlichen Interconnects zu verwalten.

Wichtige Erkenntnisse

- Definition: Die EMIB-Interconnect-Board-Impedanzkontrolle bezieht sich auf die Aufrechterhaltung einer spezifischen charakteristischen Impedanz (üblicherweise 85Ω oder 100Ω differentiell) über den Übergang von der Siliziumbrücke zum organischen Substrat.

- Kritisches Maß: Rückflussdämpfung und Einfügedämpfung sind bei der Hochgeschwindigkeits-Chiplet-Integration ebenso wichtig wie der Zielimpedanzwert ($Z_0$).

- Materialeinfluss: Die Fehlanpassung der Dielektrizitätskonstante ($D_k$) zwischen der Siliziumbrücke und den PCB-Aufbauschichten ist die Hauptursache für Signalreflexionen.

- Missverständnis: Viele gehen davon aus, dass Standard-Leiterplattentoleranzen (+/- 10%) ausreichen; EMIB-Designs erfordern jedoch oft eine Kontrolle von +/- 5% oder enger.

- Validierung: Zeitbereichsreflektometrie (TDR)-Tests müssen an spezifischen Test-Coupons durchgeführt werden, die den Übergang von der Brücke zur Platine nachbilden, nicht nur an Standard-Leiterbahn-Coupons.

- Fertigungstipp: Die Kontrolle der Kupferoberflächenrauheit ist unerlässlich, um Skin-Effekt-Verluste bei Frequenzen über 25 GHz zu minimieren.

- APTPCB (APTPCB PCB Factory) ist spezialisiert auf die hochpräzisen HDI- und substratähnlichen Leiterplattenprozesse, die zur Unterstützung dieser fortschrittlichen Gehäusearchitekturen erforderlich sind.

Was EMIB-Interconnect-Board-Impedanzkontrolle wirklich bedeutet

Das Verständnis der Kerndefinition ist der erste Schritt, bevor spezifische Metriken und Fertigungstoleranzen analysiert werden.

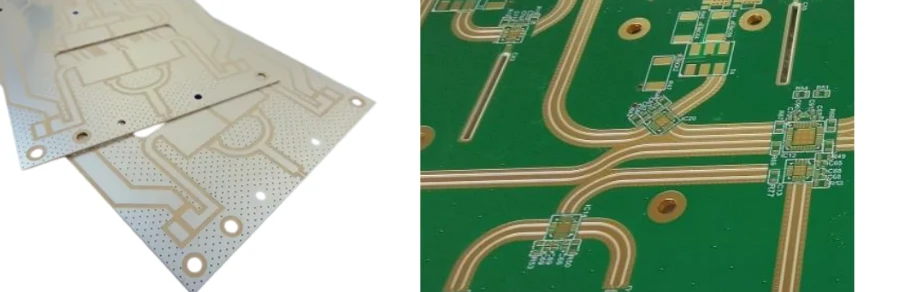

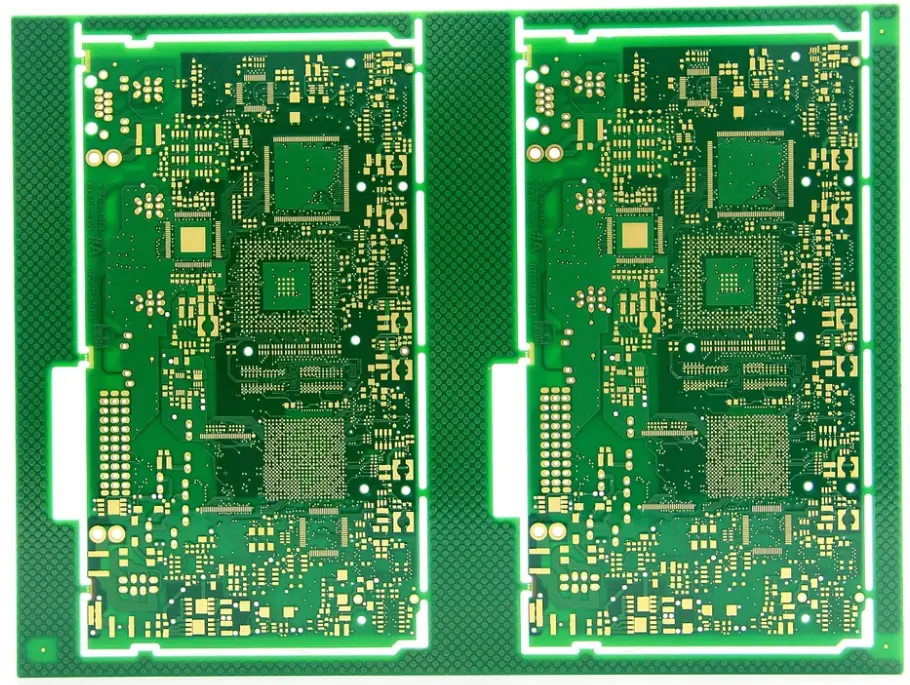

EMIB-Interconnect-Board-Impedanzkontrolle ist die Ingenieurdisziplin, die den elektrischen Widerstand gegenüber Wechselstromsignalen verwaltet, während diese zwischen der eingebetteten Siliziumbrücke und dem organischen Gehäusesubstrat verlaufen. Im Gegensatz zu Standard-Leiterplatten, bei denen Leiterbahnen auf gleichmäßigen Glasfaserschichten verlaufen, beinhaltet eine EMIB-Struktur (Embedded Multi-die Interconnect Bridge) eine hybride Umgebung. Signale müssen von einem Silizium-Die, durch Mikro-Bumps, in eine Siliziumbrücke und von dort zum Gehäusesubstrat gelangen. Die "Interconnect-Platine" fungiert in diesem Kontext als Träger. Sie muss die Impedanz der extrem feinen Leiterbahnführung auf der Siliziumbrücke anpassen. Wenn die Impedanz an der Schnittstelle nicht übereinstimmt, treten Signalreflexionen auf. Diese Reflexionen verursachen Datenkorruption, erhöhte Bitfehlerraten (BER) und reduzierte Energieeffizienz. Für APTPCB bedeutet die Erzielung dieser Kontrolle die Nutzung fortschrittlicher HDI-Techniken (High Density Interconnect), Laser-Mikrovias und ultradünner dielektrischer Materialien, die die Lücke zwischen der Halbleiterfertigung und der traditionellen Leiterplattenfertigung schließen.

Wichtige EMIB-Interconnect-Platinen-Impedanzkontrollmetriken

Sobald der Umfang der Impedanzkontrolle definiert ist, müssen Ingenieure die Qualität anhand spezifischer Leistungsindikatoren quantifizieren.

Der Erfolg eines EMIB-Interconnect-Platinendesigns hängt von der strikten Einhaltung der Signalintegritätsmetriken ab. In Hochgeschwindigkeitsanwendungen wie KI-Beschleunigern oder Rechenzentrumsprozessoren ist ein einfaches "Bestanden/Nicht bestanden" für den Widerstand unzureichend. Sie müssen bewerten, wie sich die Platine über ein Frequenzspektrum verhält.

| Metrik | Warum sie wichtig ist | Typischer Bereich / Faktoren | Wie zu messen |

|---|---|---|---|

| Charakteristische Impedanz ($Z_0$) | Bestimmt, ob der Signalpfad Quelle und Last anpasst. Fehlanpassungen verursachen Reflexionen. | 85Ω oder 100Ω (Differenziell); 50Ω (Single-ended). Toleranz: ±5% bis ±10%. | Zeitbereichsreflektometrie (TDR) an Test-Coupons. |

| Einfügedämpfung | Misst, wie viel Signalleistung beim Durchgang durch die Verbindung verloren geht. | < -1,5 dB pro Zoll bei Nyquist-Frequenz. Stark beeinflusst durch Kupferrauheit und $D_k$. | Vektor-Netzwerkanalysator (VNA) oder S-Parameter-Extraktion. |

| Rückflussdämpfung | Misst die Menge des Signals, das aufgrund von Impedanzdiskontinuitäten zur Quelle zurückreflektiert wird. | < -10 dB bis -15 dB ist wünschenswert. Weniger ist besser. | VNA (S11-Parameter). |

| Skew (Intra-Paar) | Die Zeitverzögerungsdifferenz zwischen den positiven und negativen Leitungen eines Differenzpaares. | < 5 ps (Pikosekunden). Kritisch für die Differenzialsignalisierung. | TDR oder Oszilloskop. |

| Dielektrizitätskonstanten ($D_k$) Stabilität | Variationen in $D_k$ verursachen Impedanzschwankungen entlang der Leiterbahn. | Stabiler $D_k$ über die Frequenz (z.B. 3,0 - 3,5 für fortschrittliche Substrate). | Überprüfung des Materialdatenblatts und Resonatorringe. |

| Kupferoberflächenrauheit | Raues Kupfer erhöht den Widerstand bei hohen Frequenzen (Skin-Effekt). | $R_z$ < 2 µm (VLP- oder HVLP-Kupferfolie empfohlen). | Profilometer oder REM (Rasterelektronenmikroskop). |

So wählen Sie die Impedanzkontrolle für EMIB-Verbindungsplatinen: Auswahlhilfe nach Szenario

Nachdem die Metriken festgelegt wurden, besteht die nächste Herausforderung darin, die richtige Kontrollstrategie basierend auf dem spezifischen Anwendungsszenario auszuwählen. Verschiedene Anwendungsfälle erfordern unterschiedliche Genauigkeitsgrade bei der Impedanzkontrolle von EMIB-Verbindungsplatinen. Eine Überspezifikation verursacht unnötige Kosten, während eine Unterspezifikation zu Systemausfällen führt.

Szenario 1: Hochleistungsrechnen (HPC) & KI

- Anforderung: Maximale Bandbreite (HBM-Integration).

- Kompromiss: Erfordert die engste Impedanztoleranz (±5 %) und Materialien mit extrem geringen Verlusten.

- Anleitung: Wählen Sie fortschrittliche Aufbaufilme (ABF) und HVLP-Kupfer. Kosten sind zweitrangig gegenüber der Leistung.

Szenario 2: Mobile Endgeräte für Verbraucher

- Anforderung: Miniaturisierung und Akkulaufzeit.

- Kompromiss: Platzbeschränkungen erzwingen dünnere Dielektrika, was die Impedanzkontrolle erschwert.

- Anleitung: Priorisieren Sie dünne Kernmaterialien. Akzeptieren Sie etwas lockerere Toleranzen (±7-10 %), um die Ausbeute zu erhalten und die Kosten zu senken.

Szenario 3: Automotive ADAS-Systeme

- Anforderung: Zuverlässigkeit und thermische Stabilität.

- Kompromiss: Materialien müssen thermischen Zyklen standhalten, die die Impedanz im Laufe der Zeit verschieben können.

- Anleitung: Wählen Sie Materialien mit hohem Tg und stabilem $D_k$ über weite Temperaturbereiche. Die Validierung muss thermische Belastungstests umfassen.

Szenario 4: 5G-Infrastruktur / Basisstationen

- Anforderung: Hohe Frequenz und geringe Latenz.

- Kompromiss: Lange Leiterbahnlängen auf dem Substrat erhöhen das Risiko von Einfügedämpfungen.

- Anleitung: Konzentrieren Sie sich auf „Low Loss“ und „Ultra Low Loss“ Laminate. Die Impedanzkontrolle muss die spezifischen Frequenzbänder (mmWave) berücksichtigen.

Szenario 5: Prototyp / NPI (Neue Produkteinführung)

- Anforderung: Liefergeschwindigkeit und Fehlersuche.

- Kompromiss: Schnelle Durchlaufzeiten können die Materialverfügbarkeit einschränken.

- Anleitung: Verwenden Sie standardmäßig verfügbare Hochgeschwindigkeitsmaterialien. Konzentrieren Sie sich auf die Validierung der Designlogik und nicht auf eine perfekte Impedanzoptimierung.

Szenario 6: Massenproduktion (kostensensitiv)

- Anforderung: Ausbeute und Kosteneffizienz.

- Kompromiss: Extrem enge Toleranzen können ohne hohe Ausschussraten nicht aufrechterhalten werden.

- Anleitung: Design for Manufacturing (DFM). Verbreitern Sie Leiterbahnen, wo möglich, um die Impedanz weniger empfindlich gegenüber Ätzschwankungen zu machen.

Prüfpunkte für die Implementierung der Impedanzkontrolle von EMIB-Verbindungsplatinen

Nach der Auswahl der richtigen Strategie verlagert sich der Fokus auf die taktische Umsetzung von den Designdateien bis zum Endprodukt.

Die Implementierung der Impedanzkontrolle von EMIB-Verbindungsplatinen erfordert eine synchronisierte Anstrengung zwischen dem Layout-Ingenieur und der Fertigung. Verwenden Sie diese Checkliste, um sicherzustellen, dass während des HDI PCB-Fertigungsprozesses kein kritischer Schritt übersehen wird.

- Lagenaufbau-Definition:

- Empfehlung: Definieren Sie Lagenanzahl, Dielektrikumsdicken und Kupfergewichte explizit.

- Risiko: Mehrdeutige Lagenaufbauten führen zu falschen Impedanzberechnungen durch den CAM-Ingenieur.

- Akzeptanz: Genehmigtes Lagenaufbau-Blatt, von Designer und Fertigung unterschrieben.

Materialauswahl:

- Empfehlung: Genaue Materialserie angeben (z.B. Megtron 6, Rogers oder spezifische ABF-Folien).

- Risiko: Generische "FR4"-Angaben werden bei EMIB-Geschwindigkeiten versagen.

- Akzeptanz: Materialzertifizierung (CoC) vom Lieferanten.

Leiterbahnbreite und -abstand (L/S):

- Empfehlung: Leiterbahnbreite in CAM anpassen, um Ätzfaktoren (trapezförmige Form) zu kompensieren.

- Risiko: Überätzen reduziert die Leiterbahnbreite und erhöht die Impedanz.

- Akzeptanz: Querschnittsanalyse (Mikroschliff) zur Überprüfung der Geometrie.

Referenzebenenkontinuität:

- Empfehlung: Feste Masseebenen unter Hochgeschwindigkeitssignalen sicherstellen, besonders nahe der Brückenschnittstelle.

- Risiko: Unterbrechungen in der Referenzebene verursachen sofortige Impedanzdiskontinuitäten.

- Akzeptanz: Automatische Optische Inspektion (AOI) der Innenlagen.

Mikrovia-Registrierung:

- Empfehlung: Die Ausrichtung der Laserbohrung muss präzise sein, um die Brückenpads mit dem Substrat zu verbinden.

- Risiko: Fehlausrichtung ändert die kapazitive Kopplung und somit die Impedanz.

- Akzeptanz: Röntgeninspektion der Via-Ausrichtung.

Kupferbeschichtungsdicke:

- Empfehlung: Gleichmäßige Beschichtungsverteilung beibehalten.

- Risiko: Variationen in der Kupferdicke beeinflussen die Gesamtinduktivität der Leitung.

- Akzeptanz: Zerstörungsfreie Dickenmessung (CMI).

Oberflächenveredelung:

- Empfehlung: ENIG oder ENEPIG für flache Oberflächen verwenden, die für Drahtbonden oder Flip-Chip geeignet sind.

- Risiko: Dicke HASL-Oberflächen erzeugen unebene Oberflächen und Impedanzschwankungen.

- Akzeptanz: Messung der Oberflächenveredelungsdicke (XRF).

Ätzkompensation:

- Empfehlung: Die Fabrik muss eine globale Ätzkompensation basierend auf dem Kupfergewicht anwenden.

- Risiko: Inkonsistentes Ätzen über die Platte führt zu Impedanzschwankungen zwischen den Einheiten.

- Akzeptanz: Impedanz-Coupon-Tests an den Plattenkanten.

Lötstopplack-Effekt:

- Empfehlung: Den $D_k$ des Lötstopplacks bei der Impedanzberechnung berücksichtigen (für äußere Lagen).

- Risiko: Lötstopplack reduziert die Impedanz um 2-3 Ohm; dies zu ignorieren führt zu Fehlern.

- Akzeptanz: TDR-Messung nach dem Auftragen des Lötstopplacks.

Endgültige TDR-Validierung:

- Empfehlung: 100%ige Prüfung der Impedanz-Coupons für kritische Chargen.

- Risiko: Versand von Platinen, die die elektrische Durchgängigkeit bestehen, aber die Signalintegrität nicht.

- Akzeptanz: TDR-Bericht, der Bestehen/Nichtbestehen gegenüber der Toleranz zeigt.

Häufige Fehler bei der Impedanzkontrolle von EMIB-Verbindungsplatinen

Selbst mit einer Checkliste treten in der komplexen Umgebung der Embedded-Bridge-Fertigung häufig spezifische Fehler auf.

Die Vermeidung dieser häufigen Fallstricke bei der Impedanzkontrolle von EMIB-Verbindungsplatinen kann Wochen an Neuentwicklungszeit und Tausende von Dollar an Ausschuss einsparen.

- Die "Übergangszone" ignorieren: Die kritischste Impedanzdiskontinuität tritt auf, wenn das Signal von der Siliziumbrücke zum Leiterplattensubstrat übergeht. Designer passen oft die Leiterbahnimpedanz an, ignorieren aber die parasitäre Kapazität des Landepads/Bumps. Korrektur: Simulieren Sie den Übergang in 3D-Feldsolvern und optimieren Sie den Pad-Stack.

- Generische Dielektrizitätskonstanten verwenden: Sich auf den "Marketing"-$D_k$-Wert (z.B. 4,0) verlassen, anstatt den frequenzabhängigen Wert (z.B. 3,8 bei 10 GHz) zu nutzen. Korrektur: Fordern Sie die frequenzabhängige Materialtabelle von APTPCB an.

- Kupferrauheitsmodelle vernachlässigen: Standard-Impedanzrechner gehen von glattem Kupfer aus. Bei EMIB-Geschwindigkeiten führt Rauheit zu erheblicher Verzögerung und Verlust. Korrektur: Verwenden Sie das Huray-Modell oder ähnliche Rauheitskorrekturfaktoren in den Berechnungen.

- Unzureichende Test-Coupons: Test-Coupons zu weit von der eigentlichen Schaltung entfernt platzieren oder Designs verwenden, die nicht der tatsächlichen Leiterbahndichte entsprechen. Korrektur: Verwenden Sie nach Möglichkeit eingebettete Coupons oder "In-Circuit"-Teststrukturen.

- Fertigungstoleranzen übersehen: Eine 50-Ohm-Leitung entwerfen, die eine 3,1 mil Leiterbahn erfordert, wenn die minimale Fertigungsfähigkeit der Fabrik 3 mil +/- 0,5 mil beträgt. Korrektur: Konsultieren Sie frühzeitig den Impedanzrechner und die Designregeln.

- Fehler beim Berücksichtigen harzreicher Bereiche: In heterogenen Substraten kann sich Harz in Lücken zwischen Leiterbahnen ansammeln, was den lokalen $D_k$ verändert. Korrektur: Verwenden Sie eine Kupferfüllung (Thieving), um eine gleichmäßige Harzverteilung und Pressung zu gewährleisten.

Häufig gestellte Fragen (FAQ) zur Impedanzkontrolle von EMIB-Verbindungsplatinen

Um die technischen Details abzurunden, finden Sie hier Antworten auf die dringendsten Fragen bezüglich Logistik und Ausführung.

F: Wie wirkt sich eine strenge Impedanzkontrolle bei EMIB-Verbindungsplatinen auf die Gesamtkosten aus? A: Eine Verschärfung der Toleranzen von ±10% auf ±5% kann die Kosten um 15-25% erhöhen. Dies liegt am Bedarf an hochwertigeren Materialien, häufigeren TDR-Tests und geringeren Fertigungsausbeuten.

F: Was ist die typische Lieferzeit für EMIB-Verbindungsplatinen-Prototypen mit Impedanzanforderungen? A: Standardlieferzeiten betragen 15-20 Tage. Wenn jedoch spezielle verlustarme Materialien oder ABF-Folien erforderlich sind, können sich die Lieferzeiten je nach Materialverfügbarkeit auf 4-6 Wochen verlängern.

F: Welche Materialien eignen sich am besten für die Impedanzkontrolle von EMIB-Verbindungsplatinen bei 56 Gbit/s? A: Standard-FR4 ist nicht geeignet. Sie sollten Materialien wie Panasonic Megtron 6/7, Isola Tachyon oder spezielle Ajinomoto Build-up Films (ABF) verwenden, die einen niedrigen Verlustfaktor ($D_f$) und einen stabilen $D_k$ bieten.

F: Wie werden Tests für vergrabene Schichten in einem EMIB-Substrat durchgeführt? A: Das Testen vergrabener Lagen ist auf der fertigen Platine schwierig. Wir verwenden "Test-Coupons", die sich auf den Platinenrändern befinden und die gleiche Lagenstruktur und Leiterbahngeometrie wie die eigentliche Platine aufweisen. Diese werden mittels TDR getestet, bevor die äußeren Lagen laminiert werden oder nach der endgültigen Fertigung.

Q: Was sind die Akzeptanzkriterien für TDR-Tests auf diesen Platinen? A: Das Standard-Akzeptanzkriterium ist, dass die gemessene Impedanz innerhalb der angegebenen Toleranz liegen muss (z.B. 100Ω ±10%). Zusätzlich sollte die TDR-Wellenform glatt sein, ohne scharfe Einbrüche oder Spitzen, die auf Diskontinuitäten hinweisen.

Q: Kann ich Standard-Vias für das Design von EMIB-Interconnect-Platinen verwenden? A: Im Allgemeinen nein. EMIB-Designs erfordern eine hohe Verdrahtungsdichte, die Laser-Mikrovias, Blind-Vias und Buried-Vias notwendig macht, um die Signalintegrität und Dichte zu gewährleisten. Mechanische Bohrer sind oft zu groß und erzeugen zu viel parasitäre Kapazität.

Q: Wie spezifiziere ich die Impedanzkontrolle in meinen Gerber-Dateien? A: Verlassen Sie sich nicht allein auf Gerber-Dateinamen. Fügen Sie eine detaillierte Fertigungszeichnung (Fab Drawing) bei, die die spezifischen Lagen, Leiterbahnbreiten, Referenzebenen und Zielimpedanzwerte für jede Signalgruppe auflistet.

Q: Was ist der Unterschied zwischen Single-Ended- und differentieller Impedanz in diesem Kontext? A: Die Single-Ended-Impedanz bezieht eine Leiterbahn auf eine Masseebene (üblicherweise 50Ω). Die differentielle Impedanz bezieht zwei Leiterbahnen aufeinander und auf die Masseebene (üblicherweise 85Ω oder 100Ω). EMIB-Datenpfade sind fast ausschließlich differentiell, um Rauschen zu unterdrücken.

Ressourcen zur Impedanzkontrolle von EMIB-Interconnect-Leiterplatten

- Leiterplattenfertigung für hohe Geschwindigkeiten: Entdecken Sie die Möglichkeiten zur Herstellung von Leiterplatten, die hohe Datenraten unterstützen.

- Impedanzrechner: Ein Werkzeug zur Abschätzung von Leiterbahnbreite und -abstand für Ihre Zielimpedanz.

- HDI-Leiterplattentechnologie: Erfahren Sie mehr über die Microvia- und Fine-Line-Technologien, die für EMIB-Substrate unerlässlich sind.

- Leiterplatten-Lagenaufbau-Design: Richtlinien zur Anordnung von Lagen, um eine optimale Signalintegrität zu erreichen.

Glossar zur Impedanzkontrolle von EMIB-Interconnect-Leiterplatten

| Begriff | Definition |

|---|---|

| EMIB | Embedded Multi-die Interconnect Bridge. Eine Technologie, die eine in ein Substrat eingebettete Siliziumbrücke verwendet, um Chips zu verbinden. |

| Impedanz ($Z_0$) | Der Widerstand, den ein Stromkreis dem Durchgang eines Stroms entgegensetzt, wenn eine Spannung angelegt wird. |

| TDR | Zeitbereichsreflektometrie. Eine Messtechnik zur Bestimmung der Impedanz einer Leitung. |

| Microvia | Ein kleines, mit einem Laser gebohrtes Loch (typischerweise < 150µm) zur Verbindung benachbarter Lagen in HDI-Leiterplatten. |

| ABF | Ajinomoto Build-up Film. Ein dominantes Isoliermaterial, das in IC-Substraten für Hochleistungs-CPUs/GPUs verwendet wird. |

| CTE | Wärmeausdehnungskoeffizient. Die Rate, mit der sich ein Material bei Erwärmung ausdehnt. Ungleichheiten verursachen Zuverlässigkeitsprobleme. |

| Insertion Loss | Einfügedämpfung. Der Verlust der Signalleistung, der durch das Einfügen eines Bauteils (oder einer Leiterbahn) in eine Übertragungsleitung entsteht. |

| Return Loss | Rückflussdämpfung. Der Leistungsverlust im Signal, das durch eine Diskontinuität in einer Übertragungsleitung zurückgesendet/reflektiert wird. |

| Differential Pair | Differenzialpaar. Zwei komplementäre Signale, die zur Datenübertragung verwendet werden und eine hohe Rauschimmunität bieten. |

| Skin Effect | Skin-Effekt. Die Tendenz von hochfrequentem Wechselstrom, sich nahe der Oberfläche des Leiters zu verteilen. |

| Dielectric Constant ($D_k$) | Dielektrizitätskonstante ($D_k$). Ein Maß für die Fähigkeit eines Materials, elektrische Energie in einem elektrischen Feld zu speichern. Beeinflusst Signalgeschwindigkeit und Impedanz. |

| Loss Tangent ($D_f$) | Verlustfaktor ($D_f$). Ein Maß für die als Wärme im dielektrischen Material verlorene Signalleistung. |

| RDL | Redistribution Layer (Neuverteilungsschicht). Metallschichten auf einem Chip oder Substrat, die I/O-Pads an verschiedene Stellen umleiten. |

Fazit: Nächste Schritte zur Impedanzkontrolle der EMIB-Verbindungsplatine

Die Beherrschung der EMIB-Interconnect-Board-Impedanzkontrolle ist eine Voraussetzung, um im Zeitalter von Chiplets und heterogener Integration wettbewerbsfähig zu sein. Es erfordert einen Mentalitätswandel vom "Verbinden von Punkten" zum "Verwalten von Übertragungsleitungen". Durch das Verständnis der Metriken von Einfügedämpfung und Rückflussdämpfung, die Auswahl der richtigen Materialien und die Durchsetzung strenger Fertigungskontrollpunkte können Sie sicherstellen, dass Ihre Hochleistungsdesigns wie beabsichtigt funktionieren.

Wenn Sie bereit sind, Ihr Design vom Konzept zur Produktion zu bringen, steht Ihnen APTPCB gerne zur Seite. Um eine genaue DFM-Überprüfung und ein Angebot zu erhalten, stellen Sie bitte Folgendes bereit:

- Gerber-Dateien (RS-274X) oder ODB++-Daten.

- Lagenaufbau-Diagramm, das die gewünschten Materialien und die Lagenanzahl angibt.

- Impedanzanforderungen (z. B. Lage 3, 100Ω Diff, Leiterbahnbreite 4mil).

- Netzliste zur Validierung elektrischer Tests.

Besuchen Sie unsere Angebotsseite, um Ihr Projekt noch heute zu starten.