EtherCAT-Schnittstellen-Leiterplattendesign: Definition, Umfang und an wen sich dieser Leitfaden richtet

EtherCAT-Schnittstellen-Leiterplattendesign bezieht sich auf die spezialisierten Engineering- und Layout-Prozesse, die zur Implementierung des EtherCAT-Protokolls (Ethernet for Control Automation Technology) auf einer Leiterplatte erforderlich sind. Im Gegensatz zu Standard-Büro-Ethernet arbeitet EtherCAT in rauen Industrieumgebungen, die eine Echtzeit-Datenübertragung mit Synchronisation im Mikrosekundenbereich erfordern. Der Umfang dieser Designarbeit umfasst das Layout der physikalischen Schicht (PHY), die Verlegung von Differentialpaaren, Impedanzkontrolle, magnetische Isolation und robuste Erdungsstrategien, um Paketverluste in elektrisch verrauschten Umgebungen zu verhindern.

Dieses Playbook richtet sich an Hardware-Ingenieure, technische Einkaufsleiter und Produktmanager, die einen Prototyp in die Massenproduktion überführen. Es geht über die grundlegende Schaltplantheorie hinaus und konzentriert sich auf Herstellbarkeit, Zuverlässigkeit und Lieferkettenvalidierung. Sie finden umsetzbare Spezifikationen zur Aufnahme in Ihre Dokumentation, eine Aufschlüsselung häufiger Fehlerursachen bei der Skalierung und eine strenge Checkliste, um sicherzustellen, dass Ihr Fertigungspartner eine gleichbleibende Qualität liefern kann. Bei APTPCB (APTPCB PCB Factory) stellen wir oft fest, dass Designs nicht aufgrund von Logikfehlern scheitern, sondern wegen Problemen mit dem physischen Layout, die die Signalintegrität unter Belastung beeinträchtigen. Dieser Leitfaden soll die Lücke zwischen einem funktionalen Datenblatt und einem robusten, feldbereiten Produkt schließen. Durch Befolgen dieser Schritte reduzieren Sie das Risiko von Kommunikationsausfällen (CRC-Fehler) und stellen sicher, dass Ihre Industrieautomatisierungsanlagen die strengen Zuverlässigkeitsstandards erfüllen, die auf dem Markt erwartet werden.

Wann das EtherCAT-Schnittstellen-Leiterplattendesign zu verwenden ist (und wann ein Standardansatz besser ist)

Das Verständnis der spezifischen Anforderungen industrieller Protokolle ist der erste Schritt, bevor man sich mit den technischen Spezifikationen Ihrer Platine befasst.

Während Standard-Ethernet-Layout-Richtlinien eine Basis bieten, ist das EtherCAT-Schnittstellen-Leiterplattendesign zwingend erforderlich, wenn Ihre Anwendung Bewegungssteuerung, Robotik oder Echtzeit-E/A umfasst, bei denen die Latenz deterministisch sein muss. Standard-Ethernet (TCP/IP) kann erneut gesendete Pakete und variable Latenz tolerieren; EtherCAT nicht. Geht ein Paket aufgrund schlechter Signalintegrität verloren oder verzögert sich, kann der gesamte Regelkreis ausfallen, was zu Maschinenstillstand führt. Wenn Ihr Gerät daher als EtherCAT-Slave oder -Master in einer Fabrikautomatisierungsumgebung fungiert, müssen Sie die hier beschriebenen strengen Impedanz- und Abschirmungspraktiken anwenden. Umgekehrt könnte ein standardmäßiger, weniger strenger Ethernet-Designansatz für administrative Datenports oder nicht-Echtzeit-Logging-Schnittstellen ausreichen, wo die Umgebung kontrolliert ist (z.B. ein Serverraum) und gelegentliche Latenz akzeptabel ist. Für die eigentlichen EtherCAT-Ports (IN/OUT) ist der „Standard“-Ansatz jedoch oft ein Rezept für sporadische Feldausfälle. Die Kosten eines spezialisierten Designs sind vernachlässigbar im Vergleich zu den Kosten für die Fehlersuche bei sporadischem Synchronisationsverlust in einer eingesetzten Industriemaschine.

EtherCAT-Schnittstellen-Leiterplatten-Designspezifikationen (Materialien, Lagenaufbau, Toleranzen)

Sobald Sie festgestellt haben, dass eine robuste EtherCAT-Implementierung notwendig ist, besteht der nächste Schritt darin, die Leistungsanforderungen in konkrete Fertigungsspezifikationen zu übersetzen.

Die frühzeitige Definition dieser Anforderungen verhindert „Engineering by Assumption“, bei dem der Hersteller Ihre Bedürfnisse errät. Fügen Sie diese 8–12 Spezifikationen in Ihre Fertigungszeichnung und RFQ ein, um sicherzustellen, dass das EtherCAT-Schnittstellen-Leiterplatten-Design korrekt ausgeführt wird:

- Differenzielle Impedanzkontrolle: Geben Sie 100Ω ±10% für alle differentiellen Paare (TX+/TX-, RX+/RX-) an. Dies ist der wichtigste Faktor für die Signalintegrität.

- Einseitige Impedanz: Definieren Sie 50Ω ±10% für MII/RMII/RGMII Takt- und Datenleitungen, die den EtherCAT Slave Controller (ESC) mit dem PHY verbinden.

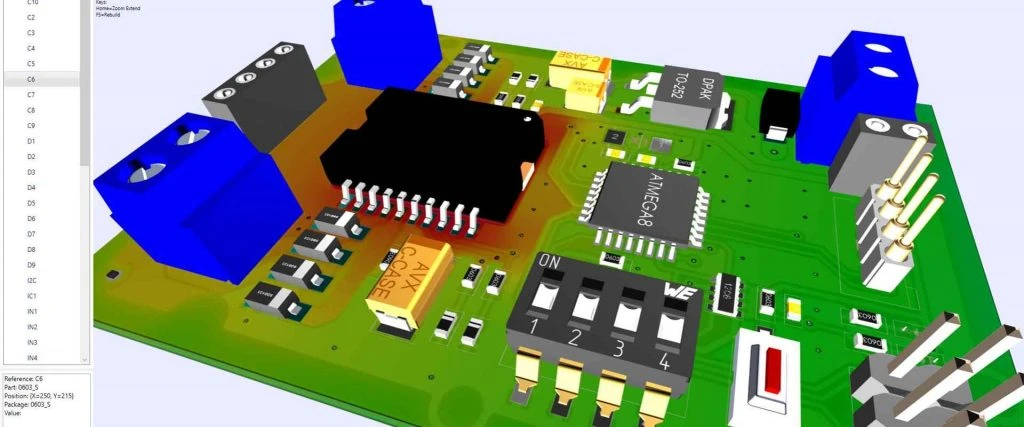

- PCB-Lagenaufbau-Strategie: Eine 4-Lagen-Platine ist für jedes EtherCAT-Design obligatorisch. Die Lagen 2 und 3 sollten als durchgehende Masse- und Versorgungsebenen dienen, um einen Rückpfad für Hochgeschwindigkeitssignale bereitzustellen.

- Kupferstärke: Standard 1 oz (35µm) ist für Signallagen in der Regel ausreichend, stellen Sie jedoch sicher, dass die Leistungsebenen den Strom bewältigen können, wenn die Platine auch Motoren oder schwere E/A ansteuert.

- Materialauswahl: Verwenden Sie FR-4 High Tg (Tg > 170°C), wenn das Gerät in Industrieschränken mit hohen Umgebungstemperaturen betrieben wird. Standard Tg (130-140°C) kann unter thermischer Belastung zu Laufbahnrissen führen.

- Leiterbahnbreite und -abstand: Geben Sie explizit die erforderliche Leiterbahnbreite und den Abstand an, um die Zielimpedanz basierend auf dem Lagenaufbau des Lieferanten zu erreichen. Typischerweise liegt dies bei etwa 4-6 mil Breite / 5-8 mil Abstand.

- Paarlängenanpassung (Skew): Der Intra-Pair-Skew muss weniger als 5 mil (0,127 mm) betragen, um Phasenverschiebungen zu verhindern, die das Datenauge schließen.

- Inter-Pair-Längenanpassung: Halten Sie Sende- und Empfangspaare innerhalb von 2 Zoll (50 mm) aufeinander abgestimmt, obwohl dies weniger kritisch ist als der Intra-Pair-Skew.

- Isolationsspannung: Legen Sie einen Freiraum auf dem PCB-Layout fest, um eine Isolation von 1,5 kVeff zwischen der Gehäusemasse (Schirm) und der digitalen Masse zu gewährleisten, typischerweise erreicht durch die Magnetics und eine physische Aussparung in den PCB-Ebenen.

- Durchkontaktierungsarten: Verwenden Sie standardmäßige Durchkontaktierungen. Vermeiden Sie verdeckte/vergrabene Durchkontaktierungen, es sei denn, die Dichte erfordert dies unbedingt, da sie Kosten und Komplexität erhöhen, ohne die Signalintegrität bei 100 Mbit/s zu verbessern.

- Oberflächenveredelung: Wählen Sie ENIG (Chemisch Nickel/Immersionsgold) für flache Pads, was das präzise Löten von feinrasterigen PHY-Chips und RJ45-Steckverbindern erleichtert.

- Lötstopplackfarbe: Obwohl oft ästhetisch, vermeiden Sie schwarze oder weiße matte Masken für erste Prototypen, da sie die visuelle Inspektion von Leiterbahnen erschweren; Grün oder Blau wird für NPI (New Product Introduction) bevorzugt.

Fertigungsrisiken beim PCB-Design von EtherCAT-Schnittstellen (Grundursachen und Prävention)

Nachdem die Spezifikationen definiert sind, müssen Sie nun antizipieren, wo das Design fehlschlagen könnte, wenn Sie von 5 Prototypen auf 5.000 Einheiten umsteigen.

Skalierungsrisiken im EtherCAT-Schnittstellen-PCB-Design resultieren oft aus Prozessschwankungen und Umweltbelastungen, die auf dem Labortisch nicht auftraten.

- Impedanzfehlanpassung aufgrund von Ätzschwankungen:

- Warum es passiert: Während der Massenproduktion kann Überätzen Leiterbahnen verengen und die Impedanz über 110Ω erhöhen.

- Erkennung: Signalreflexionen, erhöhte Bitfehlerrate (BER).

- Prävention: Fordern Sie TDR (Time Domain Reflectometry) Coupons auf jeder Produktionsplatte an und verlangen Sie einen TDR-Bericht.

- Startfehler des Quarzoszillators:

- Warum es passiert: Streukapazität durch Flussmittelrückstände oder schlechtes Layout verhindert, dass der PHY-Takt zuverlässig startet.

- Erkennung: Gerät stellt periodisch keine Verbindung her oder ist bei Ankunft defekt.

- Vermeidung: Halten Sie Quarzoszillator-Leiterbahnen extrem kurz (<10mm), umgeben Sie sie mit Masse-Schutzringen und stellen Sie sicher, dass der Leiterplatten-Montageprozess eine gründliche Reinigung beinhaltet (falls kein No-Clean-Flussmittel verwendet wird).

- ESD-Schaden am PHY:

- Warum es passiert: Industrielle Umgebungen weisen hohe statische Aufladung auf. Wenn die TVS-Dioden zu weit vom Stecker entfernt platziert werden, trifft der Spannungsstoß zuerst den PHY.

- Erkennung: Permanenter Portausfall nach Handhabung oder Installation.

- Vermeidung: Platzieren Sie ESD-Schutzvorrichtungen unmittelbar neben den Steckerpins. Leiten Sie Signale durch die Schutzpads, nicht nur "abzweigen".

- Sättigung oder Ausfall der Magnetics:

- Warum es passiert: Verwendung minderwertiger diskreter Magnetics oder integrierter RJ45s, die Gleichstromvorspannung oder extreme Temperaturen nicht bewältigen können.

- Erkennung: Paketverlust steigt bei hohen Temperaturen erheblich an.

- Vermeidung: Validieren Sie die Magnetics anhand der empfohlenen Liste des PHY-Herstellers. Tauschen Sie Magnetics nicht gegen ein "billigeres Äquivalent" ohne vorherige Prüfung aus.

- Masseschleifen / Abschirmungsprobleme:

- Warum es passiert: Falsche Kopplung zwischen Gehäusemasse und digitaler Masse (z.B. Fehlen des parallelen Schaltkreises aus 1MΩ Widerstand + Kondensator).

- Erkennung: Kommunikation bricht ab, wenn Motoren oder Frequenzumrichter in der Nähe starten.

- Prävention: Befolgen Sie strikt die "Bob Smith Termination"- und Isolierungsrichtlinien. Stellen Sie sicher, dass die RJ45-Abschirmung mit der Gehäusemasse (Chassis Ground) und nicht direkt mit der digitalen Masse (Digital Ground) verbunden ist.

- Mechanische Ermüdung des Steckverbinders:

- Warum es passiert: RJ45-Steckverbinder verlassen sich auf Lötstellen für ihre mechanische Festigkeit. Schwere Kabel vibrieren in industriellen Umgebungen und lassen die Lötstellen reißen.

- Erkennung: Zeitweise Verbindung, wenn das Kabel gewackelt wird.

- Prävention: Verwenden Sie Steckverbinder mit durchkontaktierten Abschirmungsnasen zur mechanischen Verankerung, auch wenn die Signalpins SMT sind.

- Thermisches Drosseln des PHY:

- Warum es passiert: Moderne PHYs werden heiß. Wenn die Leiterplatte keine thermischen Vias unter dem freiliegenden Pad (QFN-Gehäuse) hat, sammelt sich Wärme an.

- Erkennung: Verbindungsabbrüche nach 30-60 Minuten Betrieb.

- Prävention: Platzieren Sie eine dichte Anordnung von thermischen Vias, die direkt unter der PHY-Komponente mit der Masseebene verbunden sind.

- Referenzebenen-Diskontinuitäten:

- Warum es passiert: Verlegen von Differentialpaaren über eine Unterbrechung in der Masseebene (z. B. Übergang von 3,3V- zu 5V-Ebenenbereichen).

- Erkennung: Hohe EMI-Emissionen und schlechte Signalintegrität.

- Prävention: Stellen Sie sicher, dass Differentialpaare über eine durchgehende, ununterbrochene Massereferenzebene über ihre gesamte Länge verlaufen.

- Skew durch Fasergeflecht-Effekt:

- Warum es passiert: Bei sehr schnellen Leitungen (Gigabit EtherCAT G) kann das Glasgeflechtmuster in FR4 dazu führen, dass ein Bein des Paares schneller als das andere läuft.

- Erkennung: Jitter und Augendiagramm-Schließung.

- Prävention: Bei Standard-100-Mbit/s-EtherCAT ist dies selten. Bei Gigabit-Verbindungen Leiterbahnen in einem leichten Winkel (Zickzack) relativ zur Gewebestruktur verlegen.

- Flussmittelrückstände unter BGA/QFN:

- Warum es passiert: Schlechte Reinigung unter Bauteilen mit geringem Abstand verursacht Leckströme.

- Erkennung: Instabiler Betrieb in feuchten Umgebungen.

- Prävention: Verwenden Sie renommierte Bestückungsdienstleister mit verifizierten Waschprozessen oder qualifizierten No-Clean-Pasten.

Validierung und Abnahme des EtherCAT-Schnittstellen-Leiterplattendesigns (Tests und Bestehenskriterien)

Die Risikoprävention erfordert einen strukturierten Validierungsplan, der bestätigt, dass das EtherCAT-Schnittstellen-Leiterplattendesign alle physikalischen und funktionalen Anforderungen erfüllt.

Dieser Plan sollte während der NPI-Phase (New Product Introduction) ausgeführt werden, bevor die Massenproduktion freigegeben wird.

- TDR-Impedanzprüfung:

- Ziel: Bestätigung der Fertigungsgenauigkeit der Leiterbahnen.

- Methode: Messung von Testcoupons, die vom Leiterplattenhersteller bereitgestellt werden.

- Kriterien: 100Ω ±10% für Differentialpaare; 50Ω ±10% für Single-Ended.

- DC-Widerstands- & Durchgangsprüfung:

- Ziel: Sicherstellen, dass keine Unterbrechungen/Kurzschlüsse im Signalpfad vorhanden sind.

- Methode: Automatisierter Flying-Probe- oder Nadelbett-Test.

- Kriterien: 100% bestanden auf allen Netzen.

- Signalintegritäts-Test (Augendiagramm):

- Ziel: Validierung der Qualität des physikalischen Signals.

- Methode: Verwenden Sie ein Oszilloskop mit einer Differenztastkopf an den PHY TX-Pins.

- Kriterien: Das "Auge" muss weit geöffnet sein und die IEEE 802.3 Maskenanforderungen erfüllen. Kein Überschwingen >10%.

- Paketfehlerratentest (BERT):

- Ziel: Funktionale Zuverlässigkeit über die Zeit testen.

- Methode: Führen Sie eine EtherCAT-Master-Schleife aus, die Millionen von Paketen über 24-48 Stunden sendet.

- Kriterien: Keine verlorenen Pakete (CRC-Fehler) über die gesamte Dauer.

- Thermischer Stresstest:

- Ziel: Stabilität unter Hitze überprüfen.

- Methode: Betreiben Sie das Gerät in einer Kammer bei maximaler Nenntemperatur (z.B. 85°C) für 4 Stunden.

- Kriterien: Keine Verbindungsabbrüche; PHY-Temperatur bleibt innerhalb der Datenblattgrenzen.

- Vibrations-/Schocktest:

- Ziel: Mechanische Robustheit des Steckverbinders validieren.

- Methode: Zufälliges Vibrationsprofil (z.B. 5-500Hz), während die Verbindung aktiv ist.

- Kriterien: Keine physischen Risse; kein momentaner Verbindungsverlust.

- EMV/EMI-Vorkonformitätsscan:

- Ziel: Sicherstellen, dass das Gerät keine übermäßige Störung abstrahlt.

- Methode: Nahfeldsonden-Scan über den Steckverbinder- und PHY-Bereich.

- Kriterien: Emissionen sollten 3-6dB unter den Grenzwerten der Klasse A/B liegen.

- ESD-Immunitätstest:

- Ziel: Schutzdioden überprüfen.

- Methode: Kontaktentladung (±4kV) und Luftentladung (±8kV) auf den Steckverbinderschirm und die Pins anwenden.

- Kriterien: Gerät kann zurückgesetzt werden, muss sich aber selbst wiederherstellen; keine dauerhaften Schäden.

- Isolation (Hi-Pot) Test:

- Ziel: Galvanische Trennung überprüfen.

- Methode: 1500V AC zwischen der Ethernet-Kabelseite und der Schaltungsseite anlegen.

- Kriterien: Leckstrom < 1mA; kein Durchschlag.

- Interoperabilitätsprüfung:

- Ziel: Kompatibilität mit verschiedenen Mastern sicherstellen.

- Methode: Verbindung zu TwinCAT (Beckhoff), Omron und anderen Standard-Mastern herstellen.

- Kriterien: Erfolgreiche Enumeration und Übergang in den Betriebs-(OP)-Zustand.

Qualifizierungscheckliste für Lieferanten von EtherCAT-Schnittstellen-Leiterplatten-Designs (RFQ, Audit, Rückverfolgbarkeit)

Um den Validierungsplan erfolgreich auszuführen, benötigen Sie einen Fertigungspartner, der in der Lage ist, Ihre strengen Anforderungen an das EtherCAT-Schnittstellen-Leiterplatten-Design einzuhalten.

Verwenden Sie diese Checkliste, um potenzielle Lieferanten zu prüfen. Wenn sie diese Fragen nicht zuversichtlich beantworten können, sind sie wahrscheinlich nicht für die Industriekommunikationselektronik geeignet.

Gruppe 1: RFQ-Eingaben für das EtherCAT-Schnittstellen-Leiterplatten-Design (Was Sie senden)

- Gerber-Dateien: RS-274X-Format, klar und fehlerfrei.

- Fertigungszeichnung: Deutliche Angabe der IPC Klasse 2 oder 3 Anforderungen.

- Lagenaufbau-Definition: Explizite Lagenreihenfolge, Materialtyp und Dicke.

- Impedanztabelle: Auflistung von Lage, Leiterbahnbreite, Abstand und Zielimpedanz.

- Bohrtabelle: Definition der fertigen Bohrungsgrößen und Toleranzen.

- Bestückungsdatei (Pick & Place File): Zentroidendaten für die Bestückung.

- Stückliste (BOM): Mit Liste zugelassener Lieferanten (AVL) für kritische Bauteile wie PHYs und Magnetiken.

- Testanforderungen: Spezifische Anweisungen für TDR- und Funktionstests.

Gruppe 2: Nachweis der Fähigkeiten für das EtherCAT-Schnittstellen-Leiterplattendesign (Was sie nachweisen müssen)

- Impedanzkontrolle: Können sie eine Toleranz von ±10 % erreichen? Verfügen sie über hauseigene TDR-Ausrüstung?

- Minimaler Leiterbahn-/Abstand: Können sie zuverlässig 4mil/4mil ätzen, falls für hochdichte PHYs erforderlich?

- Materialbestand: Haben sie High-Tg FR4 und Materialien, die für industrielle Temperaturen geeignet sind, auf Lager?

- Bestückung mit kleinem Rastermaß: Können sie QFNs oder BGAs mit 0,5 mm Rastermaß handhaben, die für EtherCAT-Controller verwendet werden?

- Röntgeninspektion: Verfügen sie über Röntgenfähigkeit zur Inspektion von Lötstellen unter QFN/BGA-Chips?

- Schutzlackierung: Bieten sie Beschichtungsdienstleistungen zum Schutz vor rauen Umgebungsbedingungen an?

Gruppe 3: Qualitätssystem & Rückverfolgbarkeit

- Zertifizierungen: ISO 9001 ist obligatorisch; IATF 16949 ist ein Bonus für Industrie/Automobil.

- IPC-Standards: Schulen sie ihr Personal nach IPC-A-600 (Leiterplatte) und IPC-A-610 (Bestückung)?

- Wareneingangskontrolle (WEK): Wie überprüfen sie die Echtheit von Chips (um gefälschte PHYs zu vermeiden)?

- Lotpasteninspektion (SPI): Wird SPI auf jeder Platine eingesetzt, um Lötfehler zu verhindern?

- AOI (Automatische Optische Inspektion): Wird AOI nach dem Reflow-Löten durchgeführt?

- Rückverfolgbarkeit: Können sie eine bestimmte PCB-Seriennummer der verwendeten Rohmaterialcharge zuordnen?

Gruppe 4: Änderungskontrolle & Lieferung

- PCN (Produktänderungsmitteilung): Werden sie Sie benachrichtigen, bevor sie die Lötstopplackmarke oder den Laminatlieferanten wechseln?

- EQ (Technische Fragen): Prüfen sie die Dateien und stellen DFM-Fragen, bevor sie beginnen? (Schweigen ist ein Warnsignal).

- Lieferzeit: Ist die Lieferzeit für die von Ihnen erwarteten Mengen konsistent?

- Verpackung: Verwenden sie ESD-sichere, vakuumversiegelte Verpackungen mit Trockenmittel?

- Logistik: Können sie DDP (Delivered Duty Paid) versenden, wenn Sie international sind?

So wählen Sie das EtherCAT-Schnittstellen-PCB-Design (Kompromisse und Entscheidungsregeln)

Im EtherCAT-Schnittstellen-PCB-Design ist Ingenieurwesen die Kunst des Kompromisses. Hier erfahren Sie, wie Sie gängige Kompromisse bewältigen können.

- Integrierte Magnetik (MagJack) vs. Diskrete Magnetik:

- Wenn Sie Platzersparnis und einfachem Layout Priorität einräumen: Wählen Sie Integrierte MagJacks. Sie sparen Platinenplatz und reduzieren die Komponentenanzahl.

- Wenn Sie thermischer Leistung und Isolationszuverlässigkeit Priorität einräumen: Wählen Sie Diskrete Magnetik. Sie ermöglichen eine bessere Wärmeableitung und höhere Isolationsspannungsfestigkeiten, oft bevorzugt in Umgebungen mit starken Vibrationen.

- 4-Lagen- vs. 6-Lagen-Aufbau:

- Wenn Sie Kosten priorisieren: Wählen Sie 4-Lagen. Dies ist für die meisten 100-Mbit/s-EtherCAT-Designs ausreichend, wenn sorgfältig geroutet wird.

- Wenn Sie EMI-Leistung und Dichte priorisieren: Wählen Sie 6-Lagen. Die zusätzlichen Masseebenen bieten eine überlegene Abschirmung und eine einfachere Leitungsführung für komplexe ESCs mit vielen GPIOs.

- M12-Steckverbinder vs. RJ45-Steckverbinder:

- Wenn Sie IP67 (Wasser-/Staubschutz) priorisieren: Wählen Sie M12-Steckverbinder. Sie sind der Standard für die industrielle Verkabelung "außerhalb des Schranks".

- Wenn Sie Kosten und Standardverkabelung priorisieren: Wählen Sie RJ45-Steckverbinder. Sie sind allgegenwärtig und günstig, erfordern aber im Allgemeinen eine IP20-Umgebung (sauberer Schrank).

- Geschirmtes (STP) vs. Ungeschirmtes (UTP) Design:

- Wenn Sie Rauschimmunität priorisieren: Entwerfen Sie für Geschirmt (STP). Stellen Sie sicher, dass die Steckverbinderabschirmung korrekt mit dem Gehäuse geerdet ist.

- Wenn Sie die Verkabelungskosten priorisieren: Entwerfen Sie für Ungeschirmt (UTP). EtherCAT empfiehlt jedoch dringend geschirmte Kabel in Industriezonen.

- Hartgold vs. ENIG Oberflächenveredelung:

- Wenn Sie die Haltbarkeit der Steckverbindereinführung (Kontaktfinger) priorisieren: Wählen Sie Hartgold.

- Wenn Sie die Lötbarkeit von SMT-Bauteilen priorisieren: Wählen Sie ENIG. Für die meisten EtherCAT-Platinen ist ENIG die Standardwahl, es sei denn, die Leiterplatte selbst wird in eine Backplane gesteckt.

EtherCAT-Schnittstellen-Leiterplatten-Design-FAQ (Kosten, Lieferzeit, DFM-Dateien, Lagenaufbau, Impedanz, AOI-Inspektion)

F: Kann ich EtherCAT-Signale auf der untersten Lage routen? A: Ja, vorausgesetzt, Sie haben eine solide Massebezugsebene angrenzend an die unterste Schicht (z.B. Lage 3 in einer 4-Lagen-Platine). Vermeiden Sie das Verlegen von Hochgeschwindigkeitssignalen auf äußeren Lagen ohne Bezugsebene.

Q: Was ist die maximale Leiterbahnlänge für EtherCAT-Differenzialpaare? A: Obwohl der Standard lange Kabel (100 m) zulässt, sollten Leiterbahnen auf der Platine so kurz wie möglich gehalten werden, um die Dämpfung zu minimieren. Idealerweise sollten PHY-zu-Magnetics-Leiterbahnen unter 4 Zoll (100 mm) bleiben.

Q: Muss ich ungenutzte Paare im RJ45-Stecker terminieren? A: Ja. Für 10/100 Mbit/s EtherCAT sollten die ungenutzten Paare (4,5 und 7,8) über "Bob Smith"-Terminierungswiderstände (75Ω) und einen Hochspannungskondensator an Masse terminiert werden, um EMI zu reduzieren.

Q: Wie gehe ich mit "Erdmasse" vs. "Signalmasse" um? A: Signalmasse (GND) ist für Ihre Chips. Erd-/Chassis-Masse ist für die Abschirmung. Verbinden Sie diese nahe am Stecker mit einem 1MΩ-Widerstand und einem 1-2kV-Kondensator parallel, um statische Aufladung abzuleiten, aber Niederfrequenz-Rauschschleifen zu blockieren.

Q: Ist Impedanzkontrolle bei kurzen Leiterbahnen wirklich notwendig? A: Ja. Selbst bei kurzen Leiterbahnen verursachen Impedanzfehlanpassungen Reflexionen. Eine 1 cm lange Leiterbahn mag nicht sofort ausfallen, aber sie reduziert die Rauschmarge, wodurch das Gerät anfällig für externe industrielle Störungen wird.

Q: Kann ich einen Standard-Ethernet-PHY für EtherCAT verwenden? A: Im Allgemeinen ja. EtherCAT verwendet standardmäßige IEEE 802.3 physikalische Schichten. Stellen Sie jedoch sicher, dass der PHY die MII/RMII-Schnittstelle unterstützt, die von Ihrem spezifischen EtherCAT Slave Controller (ESC) benötigt wird.

F: Was ist der beste Weg, die differentiellen Paare zu routen? A: Routen Sie sie eng gekoppelt (dicht beieinander), symmetrisch und vermeiden Sie Vias, wenn möglich. Wenn Vias benötigt werden, platzieren Sie diese nahe an den Pins und stellen Sie sicher, dass Massevias in der Nähe platziert werden, um den Rückweg aufrechtzuerhalten.

F: Warum fällt mein EtherCAT-Gerät aus, wenn der Motor startet? A: Dies ist wahrscheinlich ein Erdungsproblem. Das Motorrauschen koppelt in Ihre Platine ein. Überprüfen Sie Ihre Schirmterminierung und stellen Sie sicher, dass Ihre Reset-Leitung zum PHY keine Störungen aufnimmt (fügen Sie einen Kondensator an den Reset-Pin hinzu).

Ressourcen für das EtherCAT-Schnittstellen-Leiterplattendesign (verwandte Seiten und Tools)

Um Sie bei Ihrem Design- und Beschaffungsprozess weiter zu unterstützen, nutzen Sie diese Ressourcen:

- Herstellung von Leiterplatten für die Industriesteuerung – Verstehen Sie die umfassenderen Anforderungen an industrietaugliche Platinen über die Schnittstelle hinaus.

- Impedanzrechner – Ein schnelles Tool zur Schätzung Ihrer Leiterbahnbreite und -abstände, bevor Sie den Lagenaufbau festlegen.

- DFM-Richtlinien – Umfassende Design-for-Manufacturing-Regeln, um sicherzustellen, dass Ihr Layout in großem Maßstab herstellbar ist.

- Schlüsselfertige Leiterplattenbestückung – Erfahren Sie, wie die Kombination von Leiterplattenfertigung und -bestückung Logistikrisiken für komplexe NPIs reduzieren kann.

- High-Speed-Leiterplattendesign – Tiefere technische Einblicke in die Signalintegrität für Hochfrequenzprotokolle.

Angebot für EtherCAT-Schnittstellen-Leiterplattendesign anfordern (DFM-Überprüfung + Preisgestaltung)

Bereit, Ihr EtherCAT-Schnittstellen-Leiterplattendesign vom Konzept in die Realität umzusetzen? APTPCB bietet zu jedem Angebot eine kostenlose DFM-Überprüfung an, um Impedanz- und Layoutprobleme zu erkennen, bevor sie zu kostspieligem Ausschuss werden.

Was Sie für ein genaues Angebot senden sollten:

- Gerber-Dateien (RS-274X)

- BOM (Stückliste für die Bestückung)

- Lagenaufbau- und Impedanzanforderungen

- Menge & Lieferzeitanforderungen

Klicken Sie hier, um ein Angebot & eine DFM-Überprüfung anzufordern

Fazit: Nächste Schritte für das EtherCAT-Schnittstellen-Leiterplattendesign

Die erfolgreiche Implementierung eines EtherCAT-Schnittstellen-Leiterplattendesigns erfordert mehr als nur das Verbinden von Pins in einem Schaltplan; es erfordert einen ganzheitlichen Ansatz für Signalintegrität, mechanische Robustheit und Lieferkettenvalidierung. Durch die Definition strenger Impedanzspezifikationen, die Antizipation von Skalierungsrisiken wie Wärmemanagement und ESD und die rigorose Validierung der Fähigkeiten Ihres Lieferanten sichern Sie die Zuverlässigkeit Ihres Industrieautomatisierungsprodukts. Befolgen Sie die bereitgestellte Checkliste, validieren Sie frühzeitig und wählen Sie einen Fertigungspartner, der die für die Echtzeit-Industriekommunikation erforderliche Präzision versteht.