Wichtige Erkenntnisse

- Definition: Die ICT-Abdeckung (In-Circuit Test) in der Fertigung für SPS bezieht sich auf den Prozentsatz der Netze und Komponenten auf einer speicherprogrammierbaren Steuerung (SPS)-Platine, die während der Herstellung elektrisch überprüft werden können.

- Kritikalität: Im Gegensatz zu Unterhaltungselektronik erfordern SPS eine nahezu 100%ige Zuverlässigkeit; übersehene Defekte können zu katastrophalen Industrieausfällen führen.

- Metriken: Der PCOLA/SOQ-Standard ist der Industriestandard zur Messung der Abdeckungsqualität, nicht nur einfacher Prozentpunkte.

- Design for Test (DFT): Eine hohe Abdeckung beginnt bereits in der Schaltplanphase, nicht erst in der Fabrik.

- Kompromisse: Eine höhere Abdeckung erfordert oft größere PCBs oder teurere Prüfadapter; dies auszubalancieren ist entscheidend für eine kostengünstige Produktion.

- Validierung: Simulationsberichte müssen während der Erstmusterprüfung (FAI) anhand physischer Testergebnisse validiert werden.

- Partnerschaft: Die Zusammenarbeit mit einem fähigen Hersteller wie APTPCB (APTPCB PCB Factory) stellt sicher, dass Ihre DFT-Strategie mit den tatsächlichen Produktionskapazitäten übereinstimmt.

Prozentsatz der Netze und Komponenten auf einer speicherprogrammierbaren Steuerung (SPS) wirklich bedeutet (Umfang & Grenzen)

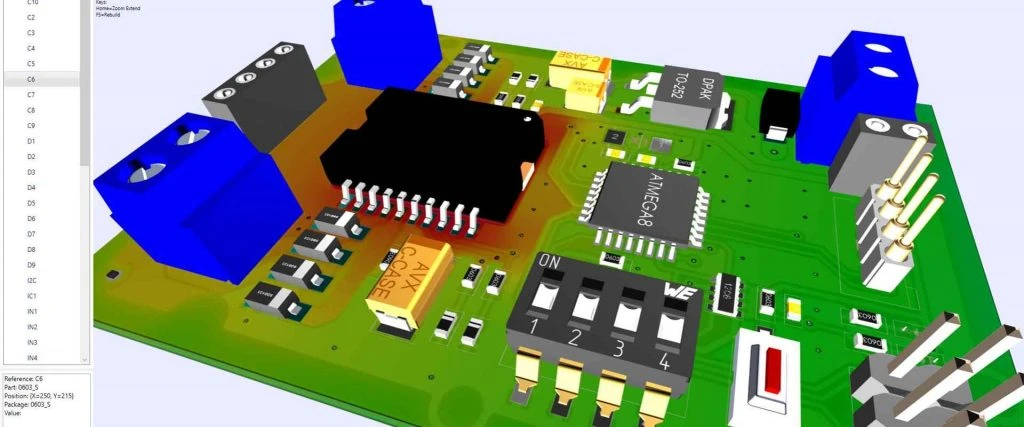

Das Verständnis des Testumfangs ist der erste Schritt zur Gewährleistung der industriellen Zuverlässigkeit in Steuerungssystemen. Die ICT-Abdeckung in der Fertigung für SPS ist ein quantitatives Maß dafür, wie viel der Logik und Konnektivität einer Leiterplatte mit einem "Nadelbett"-Tester validiert werden kann. Im Kontext von speicherprogrammierbaren Steuerungen (SPS) ist diese Metrik weitaus kritischer als in der allgemeinen Elektronik. SPS arbeiten in rauen Umgebungen mit Vibrationen, extremen Temperaturen und elektromagnetischen Störungen. Eine Lötstelle, die eine Sichtprüfung besteht, aber einen elektrischen Stresstest nicht besteht, kann Monate später zu einem Fabrikstillstand führen.

Der ICT (In-Circuit Test) zielt speziell ab auf:

- Kurzschlüsse und Unterbrechungen: Sicherstellen, dass keine unbeabsichtigten Brücken zwischen Netzen bestehen und dass Leiterbahnen durchgängig sind.

- Bauteilwerte: Überprüfung, ob Widerstand, Kapazität und Induktivität mit der Stückliste (BOM) übereinstimmen.

- Bauteilpräsenz und -ausrichtung: Sicherstellen, dass Chips korrekt montiert und ausgerichtet sind.

- Funktion aktiver Bauteile: Durchführung grundlegender Logikprüfungen an Dioden, Transistoren und ICs.

Es ist wichtig, die ICT-Abdeckung von der Abdeckung des Funktionstests (FCT) zu unterscheiden. Der ICT sucht nach Fertigungsfehlern (Lötbrücken, falsche Bauteile), während der FCT überprüft, ob die Platine ihre beabsichtigte Logik ausführt. Für eine SPS ist eine hohe ICT-Abdeckung die Grundlage, die den FCT sinnvoll macht. Wenn die physikalischen Verbindungen nicht zuerst überprüft werden, wird das funktionale Debugging unmöglich. Bei APTPCB betonen wir, dass Abdeckung nicht nur eine Prozentzahl ist. Es ist ein Risikomanagement-Tool. Eine Platine mit 95% Abdeckung könnte immer noch das eine kritische Sicherheitsrelais übersehen, das das gesamte System schützt. Daher muss der Umfang "kritische Netze" gegenüber generischen Abdeckungsstatistiken priorisieren.

Wichtige Metriken (wie man Qualität bewertet)

Die Messung der Abdeckung erfordert mehr als ein einfaches Gut/Schlecht-Verhältnis; sie erfordert eine detaillierte Analyse spezifischer Fehlertypen.

Um die ICT-Abdeckung der Fabrik für SPS wirklich zu bewerten, verwenden Ingenieure spezifische Metriken, die kategorisieren, was und wie gut getestet wird. Der Industriestandard dafür ist das PCOLA/SOQ-Modell. Dieses Modell trennt Komponentenattribute (PCOLA) von Verbindungsattributen (SOQ).

| Metrik | Warum es wichtig ist | Typischer Bereich oder Einflussfaktoren | Wie man misst |

|---|---|---|---|

| Testzugangsverhältnis | Bestimmt, ob die Prüfspitzen die Netze physisch erreichen können. | 90% - 100%. Niedriger bei HDI-Leiterplatten. | (Netze mit Testpunkten / Gesamtzahl der Netze) × 100. |

| Komponentenabdeckung | Stellt sicher, dass die richtigen Teile installiert sind. | 85% - 98%. Begrenzt durch Bypass-Kondensatoren parallel. | Anzahl der Komponenten mit verifizierten Werten / Gesamtzahl der Stückliste. |

| Netzabdeckung | Überprüft Kontinuität und Isolation. | 95% - 100%. Kritisch für Strom- und Masseebenen. | Anzahl der vollständig getesteten Netze / Gesamtzahl der Netzliste. |

| Fehlerrate bei falschen Ausfällen | Hohe Fehlalarme verlangsamen die Produktion und beschädigen die Pads. | < 500 PPM. Beeinflusst durch die Qualität der Prüfvorrichtung und Belastung. | (Fehlalarme / Gesamtanzahl der getesteten Platinen) × 1.000.000. |

| PCOLA-Wert | Prüft Anwesenheit, Korrektheit, Ausrichtung, Funktion, Justierung. | Hoch. Wesentlich für komplexe ICs und Steckverbinder. | Automatisierte Softwareanalyse der Testprogrammgenerierung. |

| SOQ-Wert | Prüft Kurzschlüsse, Unterbrechungen, Qualität (Lötstellenintegrität). | Kritisch. Muss für die SPS-Sicherheit nahe 100% liegen. | Gemessen über Widerstandsschwellen während der Kurzschluss-/Unterbrechungs-Testphase. |

| Gauge R&R | Stellt sicher, dass die Prüfvorrichtung konsistent und wiederholbar ist. | < 10%. Wenn >30%, ist das Testsystem unzuverlässig. | Statistische Analyse wiederholter Messungen an derselben Einheit. |

Auswahlhilfe nach Szenario (Kompromisse)

Verschiedene Fertigungsszenarien erfordern unterschiedliche Ansätze, um eine optimale Testabdeckung zu erreichen.

Eine 100%ige Werks-ICT-Abdeckung für SPS ist oft physikalisch unmöglich oder wirtschaftlich unrentabel. Sie müssen die richtige Strategie basierend auf dem Produktlebenszyklus und den technischen Einschränkungen wählen. Nachfolgend sind gängige Szenarien und der empfohlene Ansatz für jedes aufgeführt.

1. Hochvolumen-, Niedrigmix-Produktion

- Szenario: Massenproduktion von Standard-SPS-E/A-Modulen.

- Empfehlung: Investition in eine hochwertige Vakuumvorrichtung mit doppelseitiger Kontaktierung.

- Kompromiss: Hohe anfängliche Werkzeugkosten (5.000 $ - 15.000 $), aber die niedrigste Testzeit pro Einheit und höchste Wiederholbarkeit.

- APTPCB Einblick: Bei Stückzahlen über 5.000 Einheiten amortisieren sich die Vorrichtungskosten schnell, was die Ausgaben für maximale Abdeckung rechtfertigt.

2. Prototyp und NPI (Neue Produkteinführung)

- Szenario: Erster Durchlauf einer neuen SPS-CPU-Platine.

- Empfehlung: Verwenden Sie Flying Probe Testing (FPT) anstelle einer festen ICT-Vorrichtung.

- Kompromiss: Keine Werkzeugkosten, aber sehr langsame Testzeit pro Platine.

- Warum: Designänderungen sind häufig. FPT ermöglicht es Ihnen, Testpunkte in der Software zu aktualisieren, ohne eine physische Vorrichtung neu aufbauen zu müssen.

3. HDI-Designs (Leiterplatten mit hoher Verbindungsdichte)

- Szenario: Kompakte SPSen mit Micro-Vias und Fine-Pitch-BGAs.

- Empfehlung: Kombinieren Sie ICT mit Boundary Scan (JTAG) und automatischer Röntgeninspektion (AXI).

- Kompromiss: ICT-Sonden können nicht jedes Netz in der HDI-Leiterplattentechnologie erreichen. Sie müssen sich auf JTAG für die digitale Logik und auf Röntgen für BGA-Lötstellen verlassen.

- Risiko: Sich hier ausschließlich auf ICT zu verlassen, führt zu einer geringen Abdeckung (<60 %).

4. Sicherheitskritische SPSen (SIL 3 / SIL 4)

- Szenario: SPSen, die in Notabschaltsystemen verwendet werden.

- Empfehlung: Redundante Tests. 100 % ICT-Abdeckung auf Sicherheitsnetzen, gefolgt von 100 % FCT.

- Kompromiss: Höchste Kosten und längste Zykluszeit.

- Fokus: Die Einhaltung von Sicherheitsstandards für das Design von SPS-Leiterplatten erfordert oft physische Isolationsschlitze, was die Vakuumversiegelung für Vorrichtungen erschweren kann. Mechanische Niederhalter sind hier vorzuziehen.

5. Hochspannungs-Industriesteuerungen

- Szenario: SPSen, die 220V/480V-Eingänge direkt verwalten.

- Empfehlung: Selektiver ICT. Hochspannungsnetze nicht direkt prüfen, wenn das Testgerät die potenzielle Entladung nicht handhaben kann.

- Kompromiss: Geringere Abdeckung bei Stromeingängen zum Schutz der Testausrüstung.

- Minderung: Visuelle Inspektion (AOI) für den Hochspannungsbereich und ICT für die Niederspannungslogik verwenden.

6. Beschichtete Platinen (Schutzlack)

- Szenario: SPSen, die für feuchte oder korrosive Umgebungen bestimmt sind.

- Empfehlung: Vor der Beschichtung testen. Wenn ein Test nach der Beschichtung erforderlich ist, verwenden Sie leitfähige Gummispitzen oder spezielle Maskierungen.

- Kompromiss: Maskierung erhöht den Arbeitsaufwand. Durchstoßende Sonden können die Beschichtung beschädigen und den Feuchtigkeitsschutz beeinträchtigen.

Vom Design zur Fertigung (Implementierungs-Checkpoints)

Eine erfolgreiche ICT-Implementierung ist ein linearer Prozess, der lange vor der Fertigstellung des Leiterplattenlayouts beginnt.

Um eine hohe Werks-ICT-Abdeckung für SPSen zu gewährleisten, müssen Designer einen strengen Design-for-Test (DFT)-Workflow befolgen. Das Nachrüsten von Testpunkten auf einem fertigen Layout führt zu Problemen mit der Signalintegrität und einer schlechten Abdeckung.

- Schaltplanphase - Netzpriorisierung: Kritische Netze (Stromversorgung, Reset, Takte, Kommunikationsbusse) identifizieren. Diese im Schaltplan als "Muss getestet werden" kennzeichnen.

- Layoutphase - Testpunktplatzierung: Testpunkte (TPs) möglichst auf der Unterseite der Leiterplatte platzieren. Einseitige Prüfadapter sind deutlich günstiger und zuverlässiger als zweiseitige.

- Rasterausrichtung: TPs an einem 2,54 mm (100 mil) oder 1,27 mm (50 mil) Raster ausrichten. Punkte außerhalb des Rasters erfordern teure kundenspezifische Bohrungen für den Prüfadapter.

- TP-Geometrie: Einen Mindest-Pad-Durchmesser von 0,8 mm bis 1,0 mm für Standard-Prüfspitzen verwenden. Kleinere Pads (0,5 mm) erfordern teure, empfindliche Prüfspitzen.

- Abstandsregeln: Mindestens 1,5 mm Abstand zwischen Testpunkten und Bauteilkörpern einhalten, um zu verhindern, dass der Prüfspitzenkopf das Bauteil berührt.

- EMV-Überlegungen: Bei EMV-Zonierung und Erdung für SPS sicherstellen, dass Testpunkte auf Hochgeschwindigkeitsleitungen nicht als Antennen wirken. "Stub-freie" Testpunkte verwenden oder diese bei Bedarf mit einer Masseabschirmung abdecken.

- Passbohrungen: Mindestens zwei unplattierte Passbohrungen (3mm+) in gegenüberliegenden Ecken vorsehen. Diese richten die Leiterplatte am Prüfadapter aus. Ohne sie ist eine genaue Kontaktierung unmöglich.

- Gerber-Generierung: Eine spezielle "Testpunkt"-Datei oder eine IPC-356-Netzliste exportieren. Sich nicht darauf verlassen, dass der Hersteller errät, welche Pads zum Testen dienen.

- Prüfadapterfertigung: Daten 2-3 Wochen vor der Leiterplattenfertigung an den Prüfadapterhersteller senden.

- Fehlerbehebung: Der erste Durchlauf führt normalerweise zu Fehlalarmen. Passen Sie Softwaretoleranzen an (z. B. Widerstandsvarianz), anstatt die Platine physisch zu modifizieren.

- Dehnungsmessstreifen-Test: Messen Sie vor der Massenproduktion die mechanische Belastung, die die Vorrichtung auf die Leiterplatte ausübt. Übermäßiges Biegen kann Keramikkondensatoren reißen lassen.

- Dokumentation: Erstellen Sie einen "Abdeckungsbericht", der genau detailliert, welche Netze getestet und welche übersprungen werden. Dies ist entscheidend für die zukünftige Fehlerbehebung.

Für detaillierte Spezifikationen zu Layout-Anforderungen, beachten Sie unsere DFM-Richtlinien.

Häufige Fehler (und der richtige Ansatz)

Selbst erfahrene Ingenieure tappen in Fallen, die die Abdeckung reduzieren oder die Herstellungskosten erhöhen.

Die Vermeidung dieser Fallstricke stellt sicher, dass Ihre Strategie zur Werks-ICT-Abdeckung für SPS effektiv und sicher ist.

- Fehler: Testpunkte unter BGA- oder flachen Komponenten platzieren.

- Korrektur: Testpunkte müssen zugänglich sein. Wenn ein Netz nur unter einem BGA zugänglich ist, führen Sie es zu einem Via oder einem dedizierten Pad heraus.

- Fehler: Sich auf "Via-in-Pad" für die Sondierung verlassen.

- Korrektur: Das Sondieren von plattierten Vias kann zu "Barrel Cracking" oder unzuverlässigem Kontakt aufgrund von Lötfehlstellen führen. Verwenden Sie immer ein flaches, solides Testpad.

- Fehler: Hohe Komponenten ignorieren.

- Korrektur: Hohe Kondensatoren oder Transformatoren auf der Unterseite verhindern, dass die Platine flach auf der Vorrichtung aufliegt. Halten Sie die Unterseite relativ flach oder erstellen Sie "Keep-out"-Zonen für hohe Bauteile.

- Fehler: Annahme, dass 100% Abdeckung notwendig ist.

- Korrektur: Das Erreichen der letzten 5% Abdeckung (normalerweise Bypass-Kondensatoren oder Pull-up-Widerstände) kann die Kosten der Vorrichtung verdoppeln. Akzeptieren Sie eine geringere Abdeckung bei unkritischen passiven Bauteilen, wenn die Prozesskontrolle gut ist.

- Fehler: Die "Entlade"-Routine vergessen.

- Korrektur: Große Kondensatoren in SPSen speichern Energie. Die ICT-Vorrichtung muss über einen Entladeschaltkreis verfügen, um zu verhindern, dass die Prüfspitzen beim Kontakt durchbrennen.

- Fehler: Lötstopplack über Testpunkten verwenden.

- Korrektur: Testpunkte müssen maskenoffen sein. Prüfspitzen können Lötstopplack nicht zuverlässig durchdringen, ohne die Spitze oder die Platine zu beschädigen.

- Fehler: Die Sondendichte vernachlässigen.

- Korrektur: Zu viele Sonden auf kleiner Fläche (hohe Dichte) erzeugen massiven Aufwärtsdruck, der die Platine verziehen kann. Verteilen Sie die Testpunkte gleichmäßig.

- Fehler: Standards für die Herstellung von Leiterplatten für die Industriesteuerung übersehen.

- Korrektur: Industrielle Platinen haben dickeres Kupfer und andere thermische Profile. Stellen Sie sicher, dass die Testparameter die höhere Strombelastbarkeit der Leiterbahnen berücksichtigen.

Häufig gestellte Fragen (FAQ)

F: Was sind die typischen Kosten für eine SPS-ICT-Vorrichtung? A: Eine Standard-"Nadelbett"-Vorrichtung kostet typischerweise zwischen 2.000 und 6.000 US-Dollar, abhängig von der Anzahl der Testpunkte und davon, ob sie einseitig oder zweiseitig ist.

F: Kann IKT die Software auf der SPS testen? A: Im Allgemeinen nein. IKT testet die Hardware (Physik). Einige fortschrittliche IKT-Systeme können jedoch eine "Flash-Programmierung" durchführen, um den initialen Bootloader zu laden, was eine Brücke zur Softwareprüfung darstellt.

F: Wie unterscheidet sich IKT vom Flying-Probe-Test? A: IKT verwendet eine feste Vorrichtung, um alle Punkte gleichzeitig zu testen (schnell, hohe Einrichtungskosten). Flying Probe verwendet bewegliche Roboterarme, um Punkte sequenziell zu testen (langsam, keine Einrichtungskosten). IKT ist für die Serienproduktion; Flying Probe ist für Prototypen.

F: Was ist der Mindestabstand zwischen Testpunkten? A: Für Standard-Sonden (100 mil) halten Sie 2,54 mm Mitte-zu-Mitte ein. Für feinen Raster (50 mil) können Sie auf 1,27 mm heruntergehen, aber die Kosten der Vorrichtung steigen und die Haltbarkeit nimmt ab.

F: Beschädigt IKT die Leiterplatte? A: Es hinterlässt kleine "Kontaktspuren" (Dellen) auf den Testpads. Dies ist normal und akzeptabel. Übermäßiger Druck kann jedoch Lötstellen reißen, weshalb eine Dehnungsmessstreifen-Prüfung erforderlich ist.

F: Kann ich Vias als Testpunkte verwenden? A: Es wird nicht empfohlen. Vias sind oft mit Lötstopplack abgedeckt. Selbst wenn sie offen sind, sind sie uneben. Es ist besser, ein dediziertes Testpad hinzuzufügen, das mit dem Via verbunden ist.

F: Wie gehe ich mit Testpunkten für Hochgeschwindigkeits-Differenzpaare um? A: Das Hinzufügen eines Testpunkts erzeugt einen „Stub“, der Signale reflektieren kann. Bei sehr schnellen SPS-Kommunikationsbussen sollte eine Simulation verwendet werden, um sicherzustellen, dass der Testpunkt die Signalintegrität nicht beeinträchtigt, oder diese Leitungen stattdessen über Boundary Scan getestet werden.

Q: Warum zeigt mein Abdeckungsbericht einen niedrigen Prozentsatz an? A: Dies geschieht häufig, wenn Sie viele parallele Kondensatoren haben (der Tester sieht sie als einen großen Kondensator) oder wenn Sie viele Netze haben, die physisch unzugänglich sind (z. B. innerhalb eines BGA ohne Fan-Out).

Q: Benötige ich ICT, wenn ich AOI (Automated Optical Inspection) habe? A: Ja. AOI prüft nur, ob das Teil korrekt aussieht. Es kann nicht feststellen, ob ein Widerstand den falschen Wert hat, ob ein Chip defekt ist oder ob sich unter einer Komponente eine kalte Lötstelle befindet.

Q: Welche Daten benötigt APTPCB, um ICT anzubieten? A: Wir benötigen die Gerber-Dateien, die Stückliste (BOM), die XY Pick and Place-Datei und die elektrische Netzliste (IPC-356-Format).

Verwandte Seiten & Tools

- ICT-Testdienstleistungen: Entdecken Sie unsere spezifischen Fähigkeiten in Bezug auf In-Circuit-Test-Hardware und -Software.

- Industrielle Steuerungs-Leiterplatten: Erfahren Sie mehr über die spezifischen Material- und Fertigungsanforderungen für Industrieelektronik.

- DFM-Richtlinien: Laden Sie unsere Checkliste herunter, um sicherzustellen, dass Ihr Design für Massenproduktionstests bereit ist.

Glossar (Schlüsselbegriffe)

| Begriff | Definition |

|---|---|

| Nagelbett | Eine traditionelle ICT-Vorrichtung, die Hunderte von federbelasteten Sonden enthält, die gleichzeitig die Leiterplatte kontaktieren. |

| DFT (Design for Test) | Die Ingenieurpraxis, ein Leiterplattenlayout speziell so zu gestalten, dass eine einfache und umfassende Prüfung ermöglicht wird. |

| DUT (Device Under Test) | Die spezifische Leiterplattenbaugruppe, die sich derzeit in der Prüfvorrichtung befindet. |

| Prüfvorrichtung | Die mechanische Schnittstelle (kundenspezifische Hardware), die die Leiterplatte hält und die Sonden an den Testpunkten ausrichtet. |

| Netzliste | Eine Textdatei, die die elektrische Konnektivität der Leiterplatte beschreibt und definiert, welche Komponentenpins mit welchen Netzen verbunden sind. |

| Pogo-Pin | Eine federbelastete Sonde, die in Prüfvorrichtungen verwendet wird, um elektrischen Kontakt mit den Leiterplattenpads herzustellen. |

| IPC-356 | Das Standarddateiformat, das verwendet wird, um Testpunktkoordinaten und Netzinformationen an den Hersteller zu übermitteln. |

| Boundary Scan (JTAG) | Eine Methode zum Testen von Verbindungen auf komplexen ICs (wie FPGAs) ohne physische Sonden, unter Verwendung einer seriellen Schnittstelle. |

| Prüfspur | Die kleine Vertiefung, die die Prüfsonde auf einem Lötpad hinterlässt; Beweis dafür, dass der Punkt getestet wurde. |

| Dehnungsmessstreifen | Ein Sensor, der verwendet wird, um die physikalische Biegung oder Spannung zu messen, die während der Vakuumkompression der Vorrichtung auf die Leiterplatte ausgeübt wird. |

| False Fail | Ein Testergebnis, das einen Defekt anzeigt, obwohl die Platine tatsächlich in Ordnung ist, meist verursacht durch schlechten Sondenkontakt oder enge Toleranzen. |

| Guard Trace | Eine Technik in der IKT, bei der umgebende Netze auf eine bestimmte Spannung gebracht werden, um die zu messende Komponente zu isolieren. |

Fazit (nächste Schritte)

Eine hohe Werks-IKT-Abdeckung für SPS ist kein nachträglicher Gedanke; es ist eine strategische Entscheidung, die die Sicherheit und Zuverlässigkeit industrieller Systeme beeinflusst. Durch das Verständnis der PCOLA/SOQ-Metriken, die Auswahl der richtigen Fixture-Strategie und die Einhaltung strenger DFT-Regeln stellen Sie sicher, dass jede SPS, die die Linie verlässt, für die raue Realität der Fertigungshalle bereit ist.

Um Ihr SPS-Projekt voranzutreiben, empfiehlt APTPCB eine umfassende DFM-Überprüfung, bevor Sie Ihr Layout finalisieren. Bei der Angebotsanfrage geben Sie bitte an:

- Gerber-Dateien (einschließlich einer dedizierten Testpunkt-Schicht, falls vorhanden).

- BOM (Stückliste) mit Herstellerteilenummern.

- Netzliste (IPC-356-Format).

- Schaltpläne (PDF) als Referenz für die Fehlersuche.

- Spezifische Testanforderungen (z.B. "Muss 100% der Sicherheitsrelais-Schaltkreise testen").

Hochwertige Tests sind die Versicherungspolice für den Ruf Ihrer Marke. Beginnen Sie Ihre Validierungsreise mit den richtigen Daten und dem richtigen Partner.