Definition, Umfang und Zielgruppe dieses Leitfadens

Die Impedanzkontrolle von GaN-Leistungsstufen-Leiterplatten bezeichnet die präzise Steuerung von Leiterbahngeometrien, Lagenaufbauten und Dielektrika, damit die Signalintegrität erhalten bleibt und parasitäre Induktivitäten in Gallium-Nitrid-(GaN-)Schaltungen minimiert werden. Im Unterschied zu siliziumbasierten Designs schalten GaN-Bauelemente mit extrem hohen Geschwindigkeiten, also mit sehr hohem dv/dt und di/dt. Ohne strikte Impedanzkontrolle führen diese schnellen Flanken zu Überschwingen, Ringing und elektromagnetischen Störungen (EMI), die das Bauteil beschädigen oder Zulassungstests scheitern lassen können.

Dieser Leitfaden richtet sich an technische Leiter und Einkaufsverantwortliche, die von klassischen Silizium-MOSFET-Designs auf GaN-Technologie umstellen. Der Schwerpunkt liegt auf den realen Fertigungsbedingungen solcher Baugruppen. Sie müssen kein Physiker sein, um diesen Leitfaden zu nutzen; entscheidend ist, dass Sie als verantwortlicher Entscheider eine belastbare Lieferkette absichern wollen.

Der Umfang umfasst die kritische Schnittstelle zwischen Design und Fertigung von GaN-Leistungsstufen-Leiterplatten. Wir erläutern, wie Anforderungen so spezifiziert werden, dass ein Werk sie tatsächlich bauen kann, wie die Ergebnisse validiert werden und wie sich typische Beschaffungsfehler vermeiden lassen. APTPCB (APTPCB PCB Factory) hat diesen Leitfaden entwickelt, um die Lücke zwischen theoretischer Simulation und physischer Produktion zu schließen.

Wann dieser Ansatz sinnvoll ist und wann nicht

Wenn Sie den tatsächlichen Bedarf von GaN-Anforderungen sauber einordnen, erkennen Sie, ob Ihr Projekt die Mehrkosten einer fortgeschrittenen Impedanzkontrolle wirklich braucht oder ob eine Standardfertigung ausreicht.

Setzen Sie eine strikte Impedanzkontrolle für GaN-Leistungsstufen-Leiterplatten ein, wenn:

- die Schaltfrequenz über 500 kHz liegt: Bei diesen Geschwindigkeiten wird die parasitäre Induktivität in der Gate-Schleife zu einer kritischen Fehlerquelle.

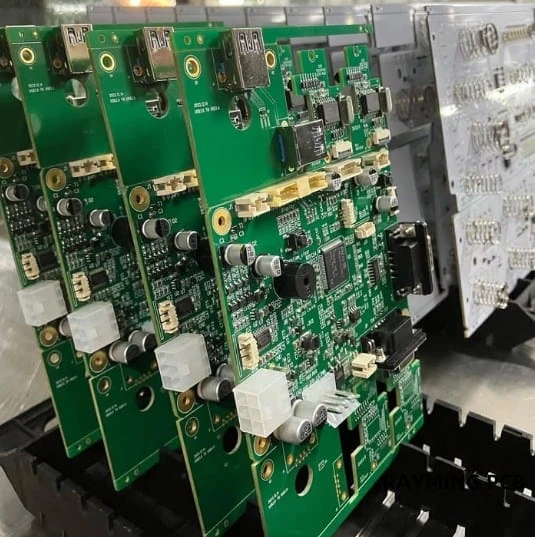

- eine hohe Leistungsdichte gefordert ist: Anwendungen wie Servernetzteile oder EV-On-Board-Charger mit dicht gepackten Bauteilen benötigen HDI-Technik (High Density Interconnect) mit kontrollierter Impedanz.

- sehr kurze Anstiegszeiten (<10ns) vorliegen: Wenn Ihre GaN-Transistoren im Nanosekundenbereich schalten, verhalten sich Leiterbahnen wie Übertragungsleitungen; dafür ist angepasste Impedanz nötig, um Reflexionen zu vermeiden.

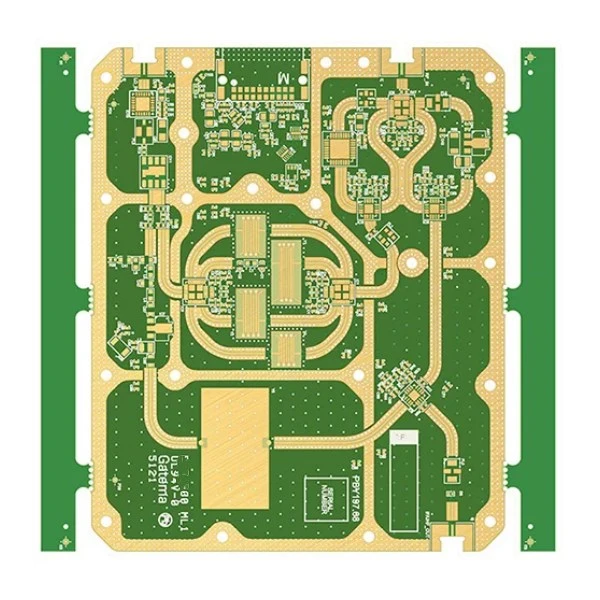

- HF-Leistungsverstärker gebaut werden: In der HF-Technik ist GaN Standard; dort ist Impedanzanpassung für einen effizienten Leistungstransfer zwingend.

Ein Standardansatz ist besser geeignet, wenn:

- Sie mit älteren Siliziumdesigns arbeiten: Bei Standard-Si-MOSFETs unter 100 kHz reichen Standardtoleranzen von +/- 10% meist aus.

- nur langsame Hilfsschaltungen betroffen sind: Steuerlogik oder Hilfsversorgungen auf derselben Leiterplatte brauchen oft nicht dieselben teuren Materialien wie die eigentliche Leistungsstufe.

- es zunächst nur um Form- und Einbaunachweise geht: Wenn ausschließlich die Mechanik verifiziert werden soll, können Sie auf aufwendige Impedanztests verzichten und dadurch Zeit sparen.

Welche Spezifikationen Sie festlegen sollten (Materialien, Lagenaufbau, Toleranzen)

Sobald feststeht, dass Ihr Projekt eine Hochleistungsfertigung verlangt, müssen Sie eindeutige Spezifikationen definieren, damit Entwicklungsteam und Hersteller dieselbe Zielvorgabe haben.

- Auswahl des Dielektrikums: Legen Sie Materialien mit stabiler Dielektrizitätskonstante (Dk) und niedrigem Verlustfaktor (Df) über hohe Frequenzen fest. Übliche Optionen sind High-Tg-FR4 für niedrigere Frequenzen oder Rogers-/Isola-Laminate für GaN-Anwendungen im HF-Bereich.

- Symmetrie des Lagenaufbaus: Definieren Sie einen ausgewogenen Stackup, um Verzug zu vermeiden. Bei GaN muss der Abstand zwischen Top-Lage (Bauteilseite) und der ersten inneren Referenzebene (GND) minimal sein, damit die Schleifeninduktivität sinkt.

- Impedanztoleranz: Wechseln Sie bei kritischen Gate-Drive- und Power-Loop-Leiterbahnen vom üblichen +/- 10% auf +/- 5% oder +/- 7%.

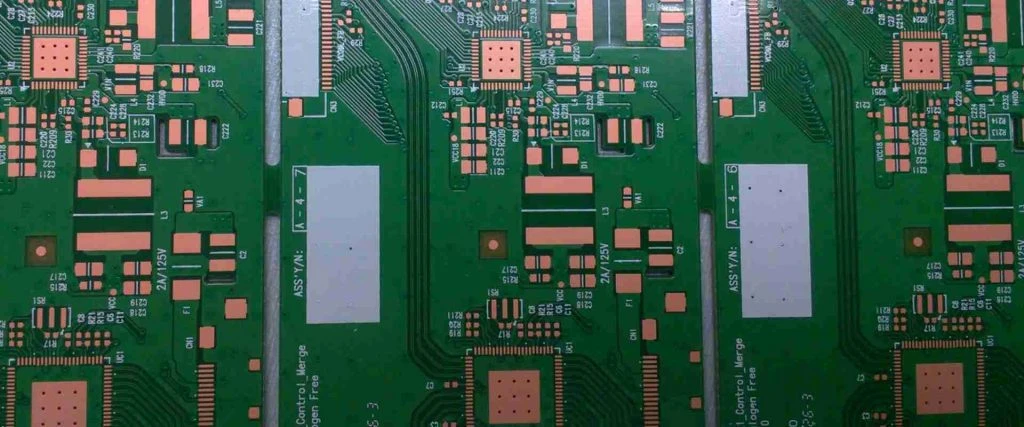

- Kupfergewicht: Geben Sie das Kupfergewicht bewusst vor. Dickes Kupfer (2oz+) ist für das Wärmemanagement vorteilhaft, erschwert aber das Feinlinienätzen für kontrollierte Impedanz.

- Leiterbahnbreite und -abstand: Definieren Sie minimale Breite und minimale Abstände passend zum Kupfergewicht. Für 1oz-Kupfer sind 4mil/4mil üblich; für 2oz ist 6mil/6mil robuster.

- Via-Typen: Geben Sie vor, ob Blind Vias oder Buried Vias notwendig sind. GaN-Designs nutzen häufig überplattierte Via-in-Pad-Lösungen (POFV), um Induktionspfade direkt unter dem thermischen Pad des Bauteils zu verkürzen.

- Oberflächenfinish: ENIG (Electroless Nickel Immersion Gold) oder ENEPIG ist HASL vorzuziehen. Die plane ENIG-Oberfläche ist für die präzise Platzierung kleiner GaN-Gehäuse wie CSP oder QFN entscheidend.

- Lötstoppmaske: Spezifizieren Sie eine LPI-Lötstoppmaske (Liquid Photoimageable). Beachten Sie, dass die Maskendicke die Impedanz beeinflusst; der Hersteller muss diesen Effekt in seine Berechnung einbeziehen.

- Schälfestigkeit: GaN-Bauelemente arbeiten heiß. Stellen Sie sicher, dass das Laminat eine hohe Kupfer-Schälfestigkeit besitzt, damit es unter Temperaturwechseln nicht zur Delamination kommt.

- Glasgewebetyp: Fordern Sie "spread glass" oder engere Gewebetypen wie 1067 oder 1080 an, um den Fasergewebeeffekt zu reduzieren, der bei schnellen Differenzpaaren Skew verursachen kann.

- Sauberkeitsanforderungen: Ionische Verunreinigungen müssen streng begrenzt werden, damit unter hohen elektrischen Feldern kein dendritisches Wachstum entsteht.

- Dokumentation: Verlangen Sie einen mitgelieferten Impedanzkontrollbericht, der die TDR-Messungen gegen die Designdaten nachweist.

Fertigungsrisiken (Ursachen und Vorbeugung)

Selbst bei perfekten Spezifikationen bringt die reale Fertigung Variablen mit sich, die die Impedanzkontrolle von GaN-Leistungsstufen-Leiterplatten stören können. Wer diese Risiken früh erkennt, vermeidet Ausschuss.

Risiko: Schwankender Ätzfaktor

- Ursache: Mit zunehmender Kupferdicke entfernt das chemische Ätzmedium oben mehr Kupfer als unten; die Leiterbahn wird trapezförmig.

- Nachweis: Querschliffanalyse (Mikrosektion).

- Vorbeugung: APTPCB rechnet Ätzkompensationsfaktoren vor Produktionsstart in die Gerber-Daten ein. Designer sollten leichte Breitenkorrekturen einplanen.

Risiko: Uneinheitliche Dielektrikumsdicke

- Ursache: Der Prepreg-Fluss während der Laminierung kann variieren und damit den Abstand zwischen Leiterbahn und Referenzebene verändern.

- Nachweis: TDR-Tests zeigen Impedanzsprünge.

- Vorbeugung: Setzen Sie in freien Bereichen Dummy-Kupfer (Thieving) ein, damit der Druck bei der Laminierung gleichmäßiger verteilt wird und die Dicke konstant bleibt.

Risiko: Registrierfehler (Lagenversatz)

- Ursache: Mechanische Toleranzen beim Bohren und bei der Laminierausrichtung.

- Nachweis: Röntgeninspektion oder Bohrprüfcoupons.

- Vorbeugung: Nutzen Sie Laser Direct Imaging (LDI) für engere Registrierung und ergänzen Sie gezielte Fiducials für kritische Lagen.

Risiko: Schwankende Lötstoppmaskendicke

- Ursache: Ein ungleichmäßiger Auftrag der Lötstoppmaske verändert die effektive Dielektrizitätskonstante um die Leiterbahn herum.

- Nachweis: Sichtprüfung und TDR.

- Vorbeugung: Setzen Sie hochwertige Sprüh- oder Curtain-Coating-Verfahren ein und berücksichtigen Sie den Maskeneffekt bereits in der ursprünglichen Stackup-Berechnung.

Risiko: Via-Zuverlässigkeit unter thermischer Belastung

- Ursache: GaN-Bauelemente erzeugen lokal konzentrierte Wärme. Die Ausdehnung der Leiterplatte in Z-Richtung kann die Via-Metallisierung reißen lassen.

- Nachweis: Thermoschocktest.

- Vorbeugung: Verwenden Sie High-Tg-Materialien (Tg > 170°C) und stellen Sie eine ausreichende Schichtdicke der Via-Metallisierung sicher, im Mittel 25µm.

Risiko: Harzverarmung

- Ursache: Schwerkupfer-Designs brauchen mehr Harz, um Zwischenräume zwischen den Leiterbahnen zu füllen. Reicht der Harzanteil im Prepreg nicht aus, entstehen Hohlräume.

- Nachweis: Hochspannungstest (dielektrischer Durchschlag) oder Mikrosektion.

- Vorbeugung: Wählen Sie Prepregs mit hohem Harzanteil für Lagen neben Schwerkupfer.

Risiko: Oxidation des Oberflächenfinishs

- Ursache: Ungeeignete Lagerung oder Handhabung von ENIG-Oberflächen.

- Nachweis: Lötbarkeitstest.

- Vorbeugung: Vakuumverpackung mit Trockenmittel und Feuchteindikator-Karten sowie eine strikt überwachte Lagerdauer.

Risiko: Feuchtigkeitsaufnahme

- Ursache: Leiterplattenmaterialien nehmen Feuchtigkeit aus der Umgebung auf, wodurch Dk steigt und beim Reflow Delamination entstehen kann.

- Nachweis: Gewichtstest oder Ausheizen.

- Vorbeugung: Backen Sie die Leiterplatten vor der Bestückung und lagern Sie sie in Moisture Barrier Bags (MBB).

Validierung und Abnahme (Prüfungen und Akzeptanzkriterien)

Damit die beschriebenen Fertigungsrisiken tatsächlich beherrscht sind, muss vor der Abnahme des GaN-Leistungsstufen-Leiterplatten-Loses ein belastbarer Validierungsplan ausgeführt werden.

Ziel: Genauigkeit der Impedanz verifizieren

- Methode: Time Domain Reflectometry (TDR) an Testcoupons oder realen Leiterplatten.

- Akzeptanzkriterium: Die gemessene Impedanz muss innerhalb der spezifizierten Toleranz liegen, zum Beispiel 50 Ohm +/- 5%.

Ziel: Aufbau des Lagenstapels verifizieren

- Methode: Mikrosektion (Querschliffanalyse).

- Akzeptanzkriterium: Dielektrikumsdicken und Kupfergewichte müssen innerhalb von +/- 10% der freigegebenen Stackup-Zeichnung entsprechen.

Ziel: Isolation verifizieren

- Methode: Hi-Pot-Test (High Potential).

- Akzeptanzkriterium: Kein Durchschlag und kein Leckstrom über dem Grenzwert, zum Beispiel <1mA, bei der festgelegten Prüfspannung.

Ziel: Lötbarkeit verifizieren

- Methode: Lotfloat-Test oder Benetzungswaagentest.

- Akzeptanzkriterium: >95% der Pad-Fläche müssen mit einer glatten, durchgehenden Lotschicht bedeckt sein.

Ziel: Thermische Zuverlässigkeit verifizieren

- Methode: Interconnect Stress Test (IST) oder Thermoschock (-40°C bis +125°C).

- Akzeptanzkriterium: Die Widerstandsänderung von Daisy-Chain-Vias muss nach der vorgegebenen Zyklenzahl <10% bleiben.

Ziel: Sauberkeit verifizieren

- Methode: Test auf ionische Verunreinigung (ROSE-Test).

- Akzeptanzkriterium: Der Kontaminationswert muss unter 1,56 µg/cm² NaCl-Äquivalent liegen, oder gemäß IPC-6012-Klasse.

Ziel: Maßhaltigkeit verifizieren

- Methode: CMM (Coordinate Measuring Machine) oder optische Inspektion.

- Akzeptanzkriterium: Außenkontur, Bohrpositionen und Slot-Abmessungen müssen innerhalb der Toleranzen der mechanischen Zeichnung liegen.

Ziel: Beschichtungsqualität verifizieren

- Methode: Röntgenfluoreszenz (XRF) zur Messung der Oberflächenfinish-Dicke.

- Akzeptanzkriterium: ENIG-Goldschicht 2-5µin; Nickelschicht 120-240µin.

Checkliste zur Lieferantenqualifizierung (RFQ, Audit, Rückverfolgbarkeit)

Mit dieser Checkliste bewerten Sie potenzielle Partner für die Fertigung und Bestückung von GaN-Leistungsstufen-Leiterplatten.

Gruppe 1: RFQ-Eingaben (was Sie bereitstellen)

- Gerber-Daten (RS-274X oder X2) mit klarer Lagenbenennung.

- Fertigungszeichnung mit Angabe der IPC-Klasse (Klasse 2 oder 3).

- Stackup-Diagramm mit Zielimpedanzen und Referenzlagen.

- Anforderungen an Materialdatenblätter (Tg, Dk, Df, CTI).

- Bohrtabelle mit Unterscheidung zwischen metallisierten und nicht metallisierten Bohrungen.

- Impedanztabelle, die Leiterbahnbreiten, Lagen und Ziel-Ohm-Werte verknüpft.

- Anforderungen an die Nutzenaufteilung, falls für die Bestückung relevant.

- Besondere Hinweise zu Via-in-Pad oder gefüllten Vias.

Gruppe 2: Nachweis der Fertigungsfähigkeit (was der Anbieter liefert)

- Maschinenliste mit Nachweis der LDI-Fähigkeit (Laser Direct Imaging).

- Beispielhafte TDR-Berichte aus früheren High-Speed-Projekten.

- UL-Zertifikat für den konkret geforderten Materialaufbau.

- DFM-Bericht als Nachweis, dass Ihre Dateien projektspezifisch geprüft wurden.

- Beleg, dass dickes Kupfer und Fine-Pitch-Strukturen auf derselben Leiterplatte beherrscht werden.

- Zertifizierung nach ISO 9001 und IATF 16949, falls Automotive relevant ist.

Gruppe 3: Qualitätssystem und Rückverfolgbarkeit

- Werden einzelne Leiterplatten serialisiert oder nur ganze Nutzen?

- Kann der Hersteller Rohmaterial-Chargen wie Laminat und Kupferfolie bis zur fertigen Leiterplatte zurückverfolgen?

- Wird AOI (Automated Optical Inspection) auf jeder Innenlage durchgeführt?

- Erfolgt ein elektrischer 100%-Test mit Flying Probe oder Nadelbett?

- Gibt es einen dedizierten Reinraum für Belichtung und Laminierung?

- Wie lautet das Verfahren für nichtkonformes Material (MRB)?

Gruppe 4: Änderungsmanagement und Lieferung

- Gibt es einen formalen PCN-Prozess (Product Change Notification)?

- Werden Stackup und Materialmarke nach der Prototypfreigabe eingefroren?

- Wie lang ist die Standardlieferzeit für dieses Technologieniveau?

- Gibt es Quick-Turn-Optionen für NPI (New Product Introduction)?

- Ist die Verpackung ESD-sicher und feuchtigkeitskontrolliert?

- Wird zu jeder Lieferung ein Certificate of Conformance (CoC) bereitgestellt?

Entscheidungshilfe (Abwägungen und Entscheidungsregeln)

Die richtige Strategie für die Impedanzkontrolle von GaN-Leistungsstufen-Leiterplatten erfordert einen sauberen Ausgleich zwischen Performance, Kosten und Herstellbarkeit.

- Wenn maximale Schaltgeschwindigkeit (>1 MHz) Priorität hat: Wählen Sie Rogers- oder High-Speed-Materialien statt FR4. Der niedrigere Verlustfaktor rechtfertigt die 2- bis 3-fachen Materialkosten, weil Signalverschlechterung vermieden wird.

- Wenn Wärmemanagement Priorität hat: Wählen Sie Schwerkupfer (3oz+) oder Metallkern-Leiterplatten. Akzeptieren Sie dabei, dass sich die Impedanztoleranz wegen der Ätzherausforderungen bei dickem Kupfer auf +/- 10% lockern kann.

- Wenn hohe Dichte und kleiner Formfaktor Priorität haben: Wählen Sie HDI mit Via-in-Pad. Das reduziert die Schleifeninduktivität deutlich, erhöht die Leiterplattenkosten aber gegenüber Durchstecktechnik um 30-50%.

- Wenn Kosten Priorität haben: Wählen Sie Standard-High-Tg-FR4 mit normalem Stackup. Für GaN-Anwendungen unter 500kHz ist das praktikabel, verlangt aber ein sorgfältiges Layout, um Materialnachteile auszugleichen.

- Wenn Zuverlässigkeit in Automotive- oder Industrieanwendungen Priorität hat: Wählen Sie eine Fertigung nach IPC Class 3. Damit gelten strengere Kriterien für Schichtdicken und Inspektion, sodass die Leiterplatte harte Temperaturwechsel besser übersteht.

- Wenn Signalintegrität wichtiger ist als Leistung: Wählen Sie dünnere Dielektrika. Dünne Lagen wie 3-4mil-Prepreg erhöhen die Kopplung und senken das Übersprechen, sind in der Fertigung aber empfindlicher.

FAQ (Kosten, Lieferzeit, DFM-Dateien, Prüfungen)

Wie stark steigen die Kosten durch Impedanzkontrolle bei GaN-Leistungsstufen-Leiterplatten? Eine strikte Impedanzkontrolle erhöht die Stückkosten der Leiterplatte in der Regel um 10-20%. Darin enthalten sind die Kosten für TDR-Testcoupons, die spezialisierte Stackup-Planung und niedrigere Fertigungsausbeuten aufgrund engerer Toleranzen.

Wie unterscheidet sich die Lieferzeit gegenüber Standardleiterplatten? Rechnen Sie mit 2-3 zusätzlichen Tagen gegenüber der Standardlieferzeit. Das Engineering-Team braucht mehr Zeit für EQs (Engineering Questions) zum Stackup, und die TDR-Prüfung erweitert den finalen QC-Ablauf.

Welche DFM-Dateien werden konkret benötigt? Zusätzlich zu Standard-Gerbern sollten Sie nach Möglichkeit eine IPC-2581- oder ODB++-Datei sowie eine detaillierte Stackup-Zeichnung bereitstellen. Markieren Sie ausdrücklich, welche Leiterbahnen "impedance critical" sind, damit der CAM-Ingenieur weiß, welche Linien gemessen werden müssen.

Kann ich Standard-FR4 für die Impedanzkontrolle von GaN-Leistungsstufen-Leiterplatten verwenden? Ja, für GaN-Anwendungen mit niedrigeren Frequenzen unter 1 MHz. Sie müssen dann jedoch "High-Tg"-FR4 mit Tg > 170°C einsetzen, damit das Material der thermischen Belastung standhält. Für höhere Frequenzen ist Standard-FR4 zu verlustbehaftet.

Welche Abnahmekriterien gelten für TDR-Tests auf GaN-Leiterplatten? Der Standard liegt bei +/- 10% der Zielimpedanz. Für Hochleistungs-GaN können Sie +/- 5% verlangen, was aber die Zahl geeigneter Lieferanten begrenzen und die Kosten erhöhen kann.

Wie beeinflusst die Kupferdicke die Impedanzkontrolle? Dickeres Kupfer (2oz+) erschwert das präzise Ätzen feiner Leiterbahnen und erhöht dadurch die Impedanzstreuung. Wenn Sie gleichzeitig hohen Strom und enge Impedanztoleranzen brauchen, sollten Sie unterschiedliche Kupfergewichte auf verschiedenen Lagen in Betracht ziehen.

Warum wird Via-in-Pad bei GaN-Leistungsstufen-Leiterplatten empfohlen? Bei Via-in-Pad liegt das Via direkt unter dem Lötpad des Bauteils. Dadurch entsteht der kürzestmögliche Weg zur Massefläche, was die parasitäre Induktivität minimiert, den zentralen Gegner guter GaN-Performance.

Muss ich 100% der Leiterplatten auf Impedanz prüfen? Normalerweise nicht. TDR ist destruktiv, wenn direkt auf der Leiterplatte gemessen wird, daher testet man auf Prüfcoupons an den Nutzenrändern. Üblicherweise wird pro Nutzen oder pro Los ein Coupon geprüft, um den Prozess abzusichern.

Verwandte Seiten und Tools

- Fertigung von Hochfrequenz-Leiterplatten – Hier finden Sie Materialoptionen und Prozessfähigkeiten speziell für schnelle Schaltanwendungen wie GaN.

- Impedanzrechner – Mit diesem Werkzeug können Sie Leiterbahnbreiten und Abstände für Ihre Zielimpedanz abschätzen, bevor das Layout finalisiert wird.

- HDI-Leiterplatten-Fähigkeiten – Erfahren Sie mehr über High Density Interconnect, das in GaN-Designs oft nötig ist, um die Schleifeninduktivität zu minimieren.

- DFM-Richtlinien – Prüfen Sie die Designregeln, damit Ihre impedanzkontrollierte Leiterplatte ohne Verzögerungen gefertigt werden kann.

- PCB-Bestückungsservice – So gehen wir nach der Fertigung mit der Bestückung feinrastiger GaN-Bauteile um.

Angebot anfordern (DFM-Prüfung + Preis)

Sind Sie bereit, vom Design in die Produktion zu wechseln? Senden Sie Ihre Daten an APTPCB, damit wir eine umfassende DFM-Prüfung und ein Preisangebot erstellen können. Wir prüfen Ihren Stackup gegen unseren Materialbestand und validieren Ihre Impedanzberechnungen, bevor Sie bezahlen.

Bitte stellen Sie für ein belastbares Angebot Folgendes bereit:

- Gerber-Daten: RS-274X oder ODB++.

- Stackup-Zeichnung: Einschließlich Materialtyp und Zielimpedanz.

- Menge: Prototypenstückzahl im Vergleich zum Serienvolumen.

- Prüfanforderungen: Geben Sie an, ob TDR-Berichte oder IPC Class 3 erforderlich sind.

Angebot und DFM-Prüfung anfordern

Fazit (nächste Schritte)

Die erfolgreiche Einführung von Gallium-Nitrid-Technologie verlangt mehr, als nur den richtigen Transistor auszuwählen. Sie erfordert einen ganzheitlichen Ansatz für die Impedanzkontrolle von GaN-Leistungsstufen-Leiterplatten. Wenn Sie enge Vorgaben für Materialien und Lagenaufbau definieren, Fertigungsrisiken verstehen und einen strikten Validierungsplan durchsetzen, stellen Sie sicher, dass Ihre Leistungsstufe effizient und zuverlässig arbeitet. Nutzen Sie die bereitgestellte Checkliste, um Lieferanten zu bewerten und sicherzustellen, dass sie die hohen Anforderungen schneller GaN-Schaltvorgänge erfüllen können.