Die Interpretation eines TDR-Berichts, also eines Berichts zur Time Domain Reflectometry, ist der letzte Verifikationsschritt zwischen einer gefertigten Printed Circuit Board, PCB, und einem funktionierenden Hochgeschwindigkeitssystem. Fuer technische Einkaeufer und Qualitaetsingenieure ist dieser Bericht das Konformitaetsdokument, das bestaetigt, dass der reale Lagenaufbau und die Aetzprozesse die in der Designphase definierten Anforderungen an die Signalintegritaet eingehalten haben.

Highlights

- Was vorab spezifiziert werden muss, also Daten, Stack-up, Materialien und Tests.

- Zentrale Risiken und fruehe Warnsignale.

- Validierungsplan und Pass-Fail-Kriterien.

- Checkliste zur Lieferantenqualifizierung und RFQ-Eingaben.

Kernaussagen

- Was vorab spezifiziert werden muss, also Daten, Stack-up, Materialien und Tests.

- Zentrale Risiken und fruehe Warnsignale.

- Validierungsplan und Pass-Fail-Kriterien.

- Checkliste zur Lieferantenqualifizierung und RFQ-Eingaben.

- Standardtoleranz: Die meisten starren Standardleiterplatten zielen auf eine Impedanztoleranz von $\pm$10%; engere Kontrolle, etwa Klasse 3 oder High-Speed, verlangt oft $\pm$5%.

- Coupon-Prinzip: TDR-Tests sind an den Testpads destruktiv; deshalb pruefen Hersteller einen Coupon, also eine Replikschaltung am Panelrand, statt der eigentlichen Baugruppe.

- Launch-Artefakt: Die ersten 200 bis 500 Pikosekunden, ps, der Kurve zeigen den Uebergang der Sonde auf den Coupon und sollen bei der eigentlichen Impedanzablesung ignoriert werden.

Highlights

- Standardtoleranz: Die meisten starren Standardleiterplatten zielen auf $\pm$10% Impedanztoleranz; engere Kontrolle bei Klasse 3 oder High-Speed verlangt oft $\pm$5%.

- Coupon-Prinzip: TDR-Testung ist an den Testpads destruktiv; deshalb wird ein Coupon am Panelrand statt der eigentlichen Leiterplatte gemessen.

- Launch-Artefakt: Die ersten 200 bis 500 ps der Kurve repraesentieren den Anschluss der Sonde an den Coupon und muessen bei der eigentlichen Bewertung ignoriert werden.

- Messzone: Das gueltige Messfenster ist das flache Plateau in der Mitte der Kurve und repraesentiert typischerweise 3 bis 6 Zoll Leiterbahnlaenge.

- Umgebungsfaktoren: Temperatur und Luftfeuchte koennen die Impedanz um 1 bis 2 Ohm verschieben; die Messung sollte daher in kontrollierter Umgebung erfolgen.

- Korrelation: Ein bestandener Coupon belegt einen korrekten Fertigungsprozess, aber Designfehler auf der realen Leiterplatte, zum Beispiel fehlende Referenzebenen, koennen dennoch zu Systemausfaellen fuehren.

- Validierungstipp: Pruefen Sie immer, ob die Leiterbahnbreite auf dem physischen Coupon zum Querschliffbericht passt, damit die TDR-Daten glaubwuerdig sind.

Inhalt

- Umfang, Entscheidungskontext und Erfolgskriterien

- Vorab zu definierende Spezifikationen

- Zentrale Risiken

- Validierung und Abnahme

- Checkliste zur Lieferantenqualifizierung

- Wie man entscheidet

- FAQ

- Glossar

Umfang, Entscheidungskontext und Erfolgskriterien

Bei der Beschaffung einer impedanzkontrollierten Leiterplatte ist der TDR-Bericht keine Formalitaet, sondern der wichtigste Nachweis dafuer, dass die Leiterplatte bei ihrer Zielgeschwindigkeit funktionieren wird. Dieser Leitfaden behandelt die Interpretation solcher Berichte fuer starre, flexible und Starrflex-Schaltungen.

Erfolgskriterien

Eine TDR-Validierung gilt nur dann als erfolgreich, wenn folgende Kennzahlen eingehalten werden:

- Impedanzkonformitaet: Alle geprueften Leitungen liegen innerhalb der spezifizierten Toleranz, zum Beispiel 50 $\Omega$ $\pm$5 $\Omega$.

- Wellenformstabilitaet: Die TDR-Kurve zeigt im Testfenster ein stabiles Plateau ohne ausgepraegte induktive Spitzen oder kapazitive Einbrueche von mehr als 2 bis 3 $\Omega$.

- Prozessfaehigkeit: In der Serienfertigung sollte der Cpk, also der Prozessfaehigkeitsindex, fuer die Impedanz $\ge$ 1.33 sein. Das spricht fuer eine statistisch stabile Fertigung.

Grenzfaelle

- Kurze Leiterbahnen: Leiterbahnen unter 1.5 Zoll lassen sich mit Standard-TDR-Sonden schwer exakt messen, weil die Launch-Reflexion den Messwert ueberdeckt.

- Verlustreiche Materialien: Bei Standard-FR4 kann die Impedanz auf langen Leiterbahnen leicht ansteigen, bedingt durch Gleichstromwiderstand und dielektrische Verluste. Das erfordert eine definierte Korrektur oder eine passende Interpretationsregel.

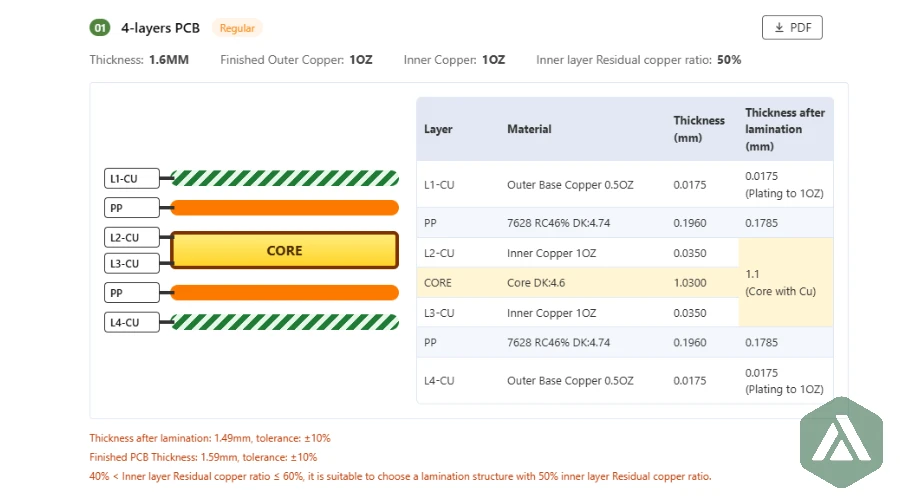

Vorab zu definierende Spezifikationen

Ein gut lesbarer TDR-Bericht beginnt mit einer klaren Fertigungszeichnung. Wenn Anforderungen nicht eindeutig sind, arbeitet der Hersteller moeglicherweise nach einem Best-Effort-Ansatz, der seine internen Checks besteht, aber Ihre Systemanforderungen nicht absichert.

Kritische Fertigungshinweise

Diese Anforderungen sollten in RFQ und Fertigungszeichnung klar vorgegeben werden:

- Impedanzmodelle: Jede kontrollierte Leitung eindeutig auffuehren, zum Beispiel "Layer 1, 50 Ohm Single-Ended, 5 mil Breite".

- Testfrequenz und Anstiegszeit: Die Anstiegszeit fuer den TDR-Impuls vorgeben. Ueblich sind 200 ps oder 500 ps. Bei sehr schnellen Anwendungen, etwa 25 Gbit/s und mehr, sollte eine schnellere Anstiegszeit wie 35 ps verlangt werden.

- Coupon-Design: Festlegen, dass Coupons gemaess IPC-2221 ausgelegt werden und bis zur Endkontrolle am Panel verbleiben.

- Dielektrische Materialien: Die exakte Materialfamilie angeben, zum Beispiel Isola PCB oder Rogers, damit die Dielektrizitaetskonstante Dk feststeht.

- Referenzebenen: Explizit definieren, welche Lagen als Massebezug dienen. Unklarheiten an dieser Stelle sind die haeufigste Ursache fuer Stack-up-Fehler.

Tabelle wichtiger Parameter

| Parameter | Standardspezifikation | High-Performance-Spezifikation | Warum das wichtig ist |

|---|---|---|---|

| Impedanztoleranz | $\pm$10% | $\pm$5% | Bestimmt den Spielraum fuer Signalreflexionen. |

| Leiterbahnbreitentoleranz | $\pm$20% | $\pm$10% oder $\pm$0.5 mil | Aetzschwankungen veraendern die Impedanz direkt. |

| Dielektrikumshoehe | $\pm$10% | $\pm$5% | Der Abstand zur Referenzebene ist der staerkste Impedanztreiber. |

| Kupferdicke | IPC Klasse 2 | IPC Klasse 3 | Die Plattierungsdicke beeinflusst die Signalausbreitung. |

| Testcoupon | Herstellerstandard | IPC-2221 Typ Z | Stellt sicher, dass das Testvehikel zur PCB-Geometrie passt. |

| TDR-Anstiegszeit | < 200 ps | < 50 ps | Schnellere Anstiegszeit zeigt kleinere Diskontinuitaeten. |

| Dk-Toleranz | $\pm$5% | $\pm$2% | Materialkonstanz sichert Wiederholbarkeit von Charge zu Charge. |

| Feuchtegehalt | < 0.2% | < 0.1% | Wasseraufnahme senkt die Impedanz, weil Wasser etwa Dk 80 hat. |

Zentrale Risiken

Wer TDR-Berichte fuer Impedanz-Coupons lesen will, muss erkennen koennen, wie ein Fehlerbild aussieht. Die meisten Fehler gehen auf physische Fertigungsabweichungen zurueck.

1. Ueberaetzung, hohe Impedanz

- Ursache: Das Aetzmedium hat zu viel Kupfer entfernt, wodurch die Leiterbahn schmaler als vorgesehen wurde. Eine Reduktion der Breite um 0.5 mil kann die Impedanz bereits um 2 bis 4 Ohm erhoehen.

- Frueherkennung: Die TDR-Kurve wirkt flach, liegt aber durchgehend ueber dem Sollwert, zum Beispiel bei 58 $\Omega$ statt 50 $\Omega$.

- Praevention: Strenge Kontrolle des PCB-Fertigungsprozesses und Einsatz einer Aetzkompensation im Artwork, etwa 0.5 bis 1.0 mil breiter ausgelegte Leiterbahnen.

2. Schwankung der Prepreg-Dicke, niedrige Impedanz

- Ursache: Waehrend der Laminierung fliesst mehr Harz als geplant ab, wodurch sich der Abstand zwischen Leiterbahn und Referenzebene verringert.

- Frueherkennung: Die TDR-Kurve ist stabil, liegt aber durchgehend unter dem Zielwert.

- Praevention: Low-Flow-Prepregs verwenden oder die Presszyklusparameter des PCB-Stack-ups verifizieren.

3. Impedanzdiskontinuitaeten, der Einbruch

- Ursache: Lokale Kapazitaetserhoehung, oft verursacht durch einen Via-Stub, ein Bauteilpad oder einen Wechsel der Referenzebene, etwa beim Ueberqueren eines Splits.

- Frueherkennung: Ein scharfer Abwaertseinbruch in der TDR-Wellenform.

- Praevention: Durchgaengige Rueckstrompfade im Design sicherstellen. Fertigungsseitig auf gleichmaessige Plattierung achten.

4. Glasgewebeeffekt

- Ursache: Bei locker gewebtem Glas, etwa Stil 106 oder 1080, kann eine Leiterbahn abwechselnd ueber Glasbuendel mit hohem Dk und Harzbereiche mit niedrigerem Dk laufen.

- Frueherkennung: Die TDR-Linie wirkt wellig oder periodisch statt flach.

- Praevention: Spread Glass FR4 oder Zickzack-Routing fuer kritische High-Speed-Leitungen verwenden.

5. Coupon-zu-Board-Abweichung

- Ursache: Das Coupon-Design entspricht nicht der echten Geometrie der Leiterplatte, zum Beispiel durch andere Freistellungen gegenueber Masseflaechen.

- Frueherkennung: Der Coupon besteht, die reale Leiterplatte faellt aber im Funktionstest durch.

- Praevention: Mikroquerschliff an der realen PCB durchfuehren und mit der Coupon-Geometrie vergleichen.

6. Feuchtigkeitsaufnahme

- Ursache: Die Leiterplatte nimmt vor der Messung Feuchtigkeit aus der Luft auf.

- Frueherkennung: Die Impedanz liegt auf allen Lagen generell niedriger als erwartet.

- Praevention: Leiterplatten vor der Messung trocknen und vakuumversiegelt lagern.

7. Probleme beim Sondenkontakt

- Ursache: Verschmutzte Sonden oder unzureichender Kontaktdruck auf dem Testpad.

- Frueherkennung: Der Launch-Bereich der Kurve ist verrauscht oder zeigt eine sehr grosse induktive Spitze von mehr als 10 $\Omega$.

- Praevention: Sonden regelmaessig reinigen und automatisierte TDR-Systeme wie Polar Atlas verwenden.

8. Laminationshohlraeume

- Ursache: Eingeschlossene Luft zwischen den Lagen veraendert den effektiven Dk, Luft hat Dk 1.0.

- Frueherkennung: Unvorhersehbare, scharfe Impedanzspitzen, haeufig begleitet von Delamination.

- Praevention: Vakuumlaminierdruck und Verweilzeit optimieren.

Validierung und Abnahme

Wenn Sie den TDR-Bericht erhalten, sollten Sie nicht nur nach einem "PASS"-Stempel suchen, sondern die Wellenformdaten selbst bewerten.

Anatomie einer TDR-Wellenform

- Bereich 1: Launch, 0 bis 0.5 ns: Hier sieht man Kabel und Sonde beim Uebergang auf den Coupon. Dieser Stoerbereich ist zu ignorieren.

- Bereich 2: Testleiterbahn, 0.5 ns bis Ende: Dies ist das eigentliche Pruefobjekt, also das DUT. Diese Linie sollte moeglichst flach sein.

- Bereich 3: Open, Ende: Am Ende der Coupon-Leiterbahn steigt die Linie steil ins Offene an.

Checkliste fuer Akzeptanzkriterien

| Testpunkt | Akzeptanzkriterium | Stichprobenplan |

|---|---|---|

| Mittlere Impedanz | Muss innerhalb der Toleranz liegen, zum Beispiel 50 $\Omega$ $\pm$10% | 100% der Coupons, meist 2 pro Panel |

| Impedanzvariation | Im Testfenster nicht mehr als $\pm$2 $\Omega$ Welligkeit | Alle getesteten Leitungen |

| Verifikation der Leiterbahnbreite | Reale Breite muss dem Design mit $\pm$20% oder spezifizierter Toleranz entsprechen | 1 Mikroquerschliff pro Los |

| Lagenausrichtung | Registrierung zwischen Lagen < 5 mil Abweichung | 1 Mikroquerschliff pro Los |

| Dk-Verifikation | Aus TDR berechneter Dk muss zur Materialspezifikation mit $\pm$5% passen | Periodisches Audit |

| Testlaenge | Das gueltige Datenfenster muss mindestens 60% der Couponlaenge abdecken | Sichtpruefung der Kurve |

So validieren Sie die Berichtsdaten

- Skalierung pruefen: Manche Hersteller veraendern die Y-Achse, damit eine wellige Linie flacher aussieht. Die Skala sollte typischerweise 2 bis 5 Ohm pro Division betragen und nicht 20.

- Datum und Uhrzeit pruefen: Der Bericht muss nach dem finalen Plattierungsprozess erstellt worden sein.

- Stack-up verifizieren: Den im Bericht verwendeten Aufbau mit Ihrem Design vergleichen. Wenn die Dielektrikumshoehe um mehr als 10% veraendert wurde, um die Impedanz zu treffen, kann das Ihre mechanischen Randbedingungen verletzen.

Checkliste zur Lieferantenqualifizierung

Bevor Sie einen Auftrag fuer eine impedanzkontrollierte Leiterplatte vergeben, sollten Sie die Faehigkeiten des Lieferanten systematisch pruefen.

- Ausstattung: Verwendet der Anbieter marktuebliche TDR-Systeme wie Polar CITS880s, Tektronix DSA8300 oder Agilent?

- Software: Nutzt er einen Feldloeser wie Polar SI8000 oder SI9000 fuer die Stack-up-Berechnung oder nur Naeherungsformeln?

- Coupon-Erzeugung: Wird der Coupon automatisch aus den CAM-Daten erzeugt oder manuell gezeichnet, was ein hoeheres Fehlerrisiko bedeutet?

- Rueckverfolgbarkeit: Laesst sich eine konkrete TDR-Kurve einem bestimmten Fertigungspanel und einer Datumskennung zuordnen?

- Datenaufbewahrung: Werden TDR-Daten mindestens 2 Jahre archiviert?

- Materiallager: Sind benoetigte High-Speed-Materialien wie Megtron oder Rogers auf Lager oder wird substituiert?

- Aetzkompensation: Gibt es ein dokumentiertes Verfahren zur Berechnung des Aetzfaktors in Abhaengigkeit vom Kupfergewicht?

- Umgebung: Sind Temperatur und Luftfeuchte im Messlabor kontrolliert?

- Kalibrierung: Wird die TDR-Hardware jaehrlich mit rueckverfolgbaren Standards kalibriert?

- DFM-Unterstuetzung: Bietet der Lieferant ein DFM-Review an, um vor Fertigungsstart Stack-up-Anpassungen vorzuschlagen?

- Klasse-3-Faehigkeit: Kann er IPC-Klasse-3-Impedanztoleranzen von $\pm$5% nachweislich beherrschen?

- Sondenwartung: Gibt es ein Wartungsprotokoll fuer den Austausch der Sondenspitzen? Verschlissene Sonden erzeugen verrauschte Daten.

Wie man entscheidet

Wie streng die Impedanzkontrolle sein muss, ist immer ein Abwaegen zwischen Kosten und Risiko fuer die Signalintegritaet.

- Wenn die Schnittstelle nur Standard-USB 2.0 oder langsames GPIO unter 100 MHz ist, waehlen Sie Standard-PCB-Fertigung ohne gesonderten TDR-Bericht.

- Wenn die Schnittstelle DDR3, DDR4, PCIe Gen 3 oder Ethernet ab 1 Gbit/s ist, waehlen Sie $\pm$10% Toleranz mit 100% TDR-Pruefung.

- Wenn die Schnittstelle PCIe Gen 5, 56G PAM4 oder HF ueber 5 GHz ist, waehlen Sie $\pm$5% Toleranz und Kupfer mit geringer Rauheit.

- Wenn das Budget der Hauptengpass ist, waehlen Sie TDR-Pruefung nur fuer die kritischsten Single-Ended- und Differenzleitungen statt fuer jede kontrollierte Leitung.

- Wenn die Leiterplatte eine Rigid-Flex-PCB ist, waehlen Sie einen Anbieter mit Erfahrung in schraffierter Masseflaechen-Impedanzkontrolle.

- Wenn Sie HDI-PCB mit Mikrovias verwenden, waehlen Sie einen Anbieter, der Coupons mit Mikrovia-Strukturen pruefen kann.

- Wenn die Leiterbahnbreite unter 4 mil liegt, waehlen Sie einen Lieferanten mit Laser Direct Imaging, LDI, fuer hoehere Aetzpraezision.

- Wenn der Aufbau asymmetrisch ist, waehlen Sie eine entspanntere Bow-and-Twist-Toleranz, weil strenge Dielektrikumsdicken die Verwerfungsneigung erhoehen koennen.

- Wenn Sie Quick Turn PCB benoetigen, waehlen Sie wenn moeglich Standardmaterialien wie FR4 statt exotischer HF-Materialien, sofern das Verlustbudget es erlaubt.

- Wenn der TDR-Bericht einen Fehler zeigt, waehlen Sie zuerst die Querschliffanalyse. Wenn die Geometrie stimmt, aber die Impedanz nicht, ist moeglicherweise das Material und sein Dk der Ausloeser.

FAQ

F: Wie stark erhoeht die Impedanzpruefung die PCB-Kosten? A: Typischerweise erhoehen Impedanzkontrolle und TDR-Bericht die Board-Kosten um 5% bis 15%. Darin enthalten sind zusaetzlicher CAM-Aufwand, Coupon-Flaeche am Panel und der Testaufwand.

F: Laesst sich eine Leiterplatte mit fehlerhafter Impedanz nacharbeiten? A: Nein. Sobald Leiterbahnen geaetzt und Lagen laminiert sind, steht die Geometrie fest. Ist die Impedanz ausserhalb der Spezifikation, muessen die Boards verschrottet und mit angepasster Aetzkompensation oder Dielektrikumsdicke neu gefertigt werden.

F: Warum steigt die TDR-Linie am Ende der Leiterbahn stark an? A: Ein offener Stromkreis am Leitungsende hat theoretisch unendliche Impedanz. Deshalb schiesst die TDR-Kurve am Ende des Coupons steil nach oben. Das bestaetigt gleichzeitig, dass das Signal die volle Couponlaenge durchlaufen hat.

F: Worin besteht der Unterschied zwischen Single-Ended- und Differential-TDR? A: Single-Ended misst eine Leitung gegen Masse, typischerweise 50 $\Omega$. Differential misst die Wechselwirkung zweier gekoppelter Leitungen, meist 90 $\Omega$ oder 100 $\Omega$. Dazu wird ein TDR mit zwei synchronisierten Pulsen benoetigt.

F: Warum scheitern kurze Leiterbahnen oft im TDR-Test? A: Leiterbahnen kuerzer als 1.5 bis 2 Zoll liegen oft im Bereich der Launch-Reflexion verborgen. Eine saubere Messung ist physikalisch schwierig. In solchen Faellen sollte man sich auf die Prozesskontrolle des Herstellers auf laengeren Leiterbahnen derselben Lage stuetzen.

F: Beeinflusst Loetstoppmaske die Impedanz? A: Ja. Loetstoppmaske senkt die Impedanz typischerweise um 2 bis 3 Ohm, weil ihr Dk hoeher ist als der von Luft. Die Berechnung des Herstellers muss also beruecksichtigen, ob die Leiterbahn mit Maske ueberzogen oder freigestellt ist.

F: Was bedeutet "Impedanztoleranz: was PCB-Fabriken realistisch halten koennen"? A: Standardfertiger halten meist $\pm$10%. Fortschrittliche Fertiger mit LDI und automatisierter Laminierung erreichen $\pm$5%. Alles Engere, etwa $\pm$2%, ist in der Regel experimentell oder nur mit sehr aufwendiger Selektion erreichbar.

F: Kann ich Impedanz mit einem normalen Multimeter messen? A: Nein. Ein Multimeter misst den Gleichstromwiderstand. Impedanz ist frequenzabhaengiger Wechselstromwiderstand. Dafuer braucht man TDR oder einen Vector Network Analyzer, VNA.

Angebot oder DFM-Review fuer das Lesen eines TDR-Berichts fuer Impedanz-Coupons anfragen

Glossar

| Begriff | Definition |

|---|---|

| TDR, Time Domain Reflectometry | Messmethode, bei der ein schneller Impuls in eine Leitung eingespeist und die Reflexion ausgewertet wird, um die Impedanz zu berechnen. |

| Coupon | Testschaltung auf der Panelleiste, die die realen Leiterbahnen der PCB repraesentieren soll. |

| Charakteristische Impedanz, $Z_0$ | Verhaeltnis von Spannung zu Strom fuer eine Welle auf einer Uebertragungsleitung. |

| Differenzpaar | Zwei komplementaere Signale zur Datenuebertragung mit hoher Stoerfestigkeit. |

| Dielektrizitaetskonstante, Dk oder $\epsilon_r$ | Mass dafuer, wie stark ein Material elektrische Energie speichern kann; beeinflusst Signallaufzeit und Impedanz. |

| Verlustfaktor, Df | Mass fuer den als Waerme verlorenen Signalanteil im Dielektrikum. |

| Anstiegszeit | Zeit, die ein Signal fuer den Uebergang von 10% auf 90% seines Endwertes braucht; kuerzere Zeiten erfordern bessere Impedanzkontrolle. |

| Microstrip | Leiterbahn auf einer Aussenlage mit einer Referenzebene auf einer Seite. |

| Stripline | Leiterbahn auf einer Innenlage zwischen zwei Referenzebenen. |

| Aetzfaktor | Verhaeltnis von Aetztiefe zu seitlichem Unteraetzen; entscheidend fuer die Berechnung der finalen Leiterbahnbreite. |

| Launch | Uebergang zwischen TDR-Sonde und Testcoupon; erzeugt am Anfang der Kurve ein Artefakt. |

| DUT, Device Under Test | Das konkret gemessene Bauteil oder die gemessene Leiterbahn. |

Fazit

Wer TDR-Berichte fuer Impedanz-Coupons sicher lesen kann, wird vom passiven Einkaeufer zum aktiven Qualitaetspartner. Wenn Sie die Anforderungen frueh klar definieren, insbesondere Anstiegszeit, Coupon-Design und Toleranzklasse, vermeiden Sie teure Fehler bei der Signalintegritaet. Die TDR-Kurve ist der Pulsschlag Ihrer High-Speed-PCB: Eine flache und stabile Linie innerhalb von $\pm$10% oder $\pm$5% ist der deutlichste Hinweis auf einen gesunden Fertigungsprozess. Stellen Sie bei Ihrem naechsten High-Speed-Projekt deshalb sicher, dass Ihr Partner fuer die PCB-Fertigung die notwendige Messtechnik und Transparenz fuer dieses Validierungsniveau mitbringt.