Die Investition in Design for Manufacturability (DFM) und Design for Testability (DFT) ist eine strategische Entscheidung, die die Qualitätssteuerung von einer reaktiven Fehlerbehebung in eine vorbeugende Fehlervermeidung verschiebt. Für Einkäufer und Produktmanager ist das Verständnis, wie sich PCBA-Defekte mit DFM und DFT reduzieren lassen, der wirksamste Hebel, um Gesamtkosten zu senken und die Markteinführung zu beschleunigen. Dieser Leitfaden beschreibt die technischen Spezifikationen und Entscheidungslogiken, mit denen sich Entwicklung und Fertigungskapazität sauber aufeinander abstimmen lassen.

Highlights

- Vorbeugung statt Nacharbeit: DFM erkennt Layoutprobleme, die zu Brückenbildung, Tombstoning und Voids führen, bevor die Fertigung startet.

- Testabdeckung: DFT stellt sicher, dass auftretende Fehler durch ICT oder Funktionstest erkannt werden, statt später im Feld aufzufallen.

- Kostenreduktion: Die Behebung eines Fehlers in der Designphase kostet etwa 10x weniger als in der Montage und etwa 100x weniger als nach Auslieferung.

- Lieferantenabstimmung: Klare Vorgaben zu Schablonendesign und Reflow-Profilen sind bei komplexen Bauteilen wie BGAs und QFNs entscheidend.

Wichtigste Erkenntnisse

Bevor wir in die technischen Details einsteigen, zeigt die folgende Übersicht, wie sich beide Methoden direkt auf Ihre Kostenbasis und die Produktzuverlässigkeit auswirken.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Hauptziel | Sicherstellen, dass das Produkt reproduzierbar mit hoher Ausbeute gefertigt werden kann. | Sicherstellen, dass das Produkt schnell und präzise geprüft werden kann. |

| Defektfokus | Verhindert das Entstehen von Defekten, z. B. Lötbrücken. | Erkennt Defekte, die trotz Prävention auftreten, z. B. Unterbrechungen. |

| Wesentliches Ergebnis | Optimierte Pad-Geometrien, Thermal Reliefs, Bauteilabstände. | Testpunkte, JTAG-Zugang, Scan-Chains. |

| ROI-Treiber | Höherer First Pass Yield (FPY), weniger Nacharbeit. | Geringere Feldausfallquote, schnellere Fehlerdiagnose. |

PCBA-Defekte mit DFM und DFT reduzieren: Umfang, Entscheidungskontext und Erfolgskriterien

Die Reduzierung von Defekten beginnt nicht erst an der Linie, sondern bereits bei Schaltplan und Layout. Wer fragt, wie sich PCBA-Defekte mit DFM und DFT reduzieren lassen, muss verstehen, dass er keine Standardplatine einkauft, sondern eine belastbare Prozessfähigkeit.

Entscheidungskontext

Einkäufer stehen häufig vor dem Zielkonflikt zwischen zusätzlichem Engineering-Aufwand zu Beginn und schnellerem Fortschritt im weiteren Produktionsablauf. Wer DFM-Prüfungen überspringt, um einen Prototypen schneller zu bekommen, erhält später oft Platinen, die sich kaum oder nur mit hoher Ausschussquote fertigen lassen. Der Entscheidungskontext hängt stark von der Komplexität der PCBA ab. Eine einfache Baugruppe mit großen passiven Bauteilen benötigt möglicherweise nur eine begrenzte DFM-Prüfung, während ein HDI-Board mit BGAs eine konsequente Analyse verlangt.

Erfolgskriterien

Um zu bewerten, ob Ihre DFM- und DFT-Maßnahmen wirken, sollten Sie diese Kennzahlen verfolgen:

- First Pass Yield (FPY): Anteil der Baugruppen, die alle Prüfungen ohne Nacharbeit bestehen. Für ausgereifte Produkte sind 98%+ ein üblicher Zielwert.

- Testabdeckung: Anteil der Netze und Komponenten, die automatisiert geprüft werden können. Ein starkes DFT-Ziel liegt bei 90%+ Abdeckung.

- False Fail Rate: Häufigkeit, mit der gute Baugruppen wegen ungeeigneter Grenzwerte oder instabiler Fixtures fälschlich als fehlerhaft markiert werden.

- Engineering Change Orders (ECOs): Weniger ECOs infolge von Montageproblemen sind ein klares Signal für erfolgreiches DFM.

Spezifikationen, die Sie vorab festlegen sollten

| Parameter | Empfohlener Wert / Option | Warum das wichtig ist | So prüfen Sie es |

|---|---|---|---|

| Lagenzahl | 4–8 (typisch), bei Bedarf mehr | Beeinflusst Kosten, Ausbeute und Routing-Spielraum | Stackup + DFM-Report |

| Min. Leiterbahn/Abstand | 4/4 mil (typisch) | Wirkt sich auf Ausbeute und Lieferzeit aus | DRC + Fertigungsfähigkeit |

| Via-Strategie | Through Vias vs. VIPPO vs. Microvias | Beeinflusst die Montagezuverlässigkeit | Mikroschliff + IPC-Kriterien |

| Oberflächenfinish | ENIG/OSP/HASL | Beeinflusst Lötbarkeit und Ebenheit | COC + Lötbarkeitstests |

| Lötstoppmaske | Mattgrün (Standard) | Verbessert AOI-Lesbarkeit und reduziert Brückenrisiko | AOI-Versuch + Maskenregistrierung |

| Test | Flying Probe / ICT / FCT | Abwägung zwischen Abdeckung und Kosten | Coverage-Report + Fixture-Plan |

| Akzeptanzklasse | IPC Class 2 / 3 | Definiert zulässige Defektgrenzen | Zeichnungsnotizen + Prüfbericht |

| Lieferzeit | Standard vs. expedited | Beeinflusst Terminrisiko | Angebot + Kapazitätsbestätigung |

Wenn DFM und DFT wirksam greifen sollen, müssen die relevanten Anforderungen explizit im Datenpaket stehen. Bleiben Punkte unklar, entstehen Annahmen auf dem Shopfloor, und genau daraus entstehen viele Defekte.

1. DFM-Datenanforderungen

Geben Sie Ihrem Contract Manufacturer (CM) mehr als nur Gerber-Daten.

- Auswahl der IPC-Klasse: Legen Sie ausdrücklich fest, ob die Baugruppe nach IPC-A-610 Class 2 oder Class 3 gefertigt werden soll. Daraus ergeben sich Kriterien für Lotvolumen und Ausrichtung.

- Bauteil-Footprints: Fordern Sie einen Abgleich der Footprints mit der Bill of Materials (BOM). Abweichungen zwischen realem Bauteil und Land Pattern gehören zu den häufigsten DFM-Problemen.

- Panelisierungsstrategie: Definieren Sie das Nutzenlayout. Schlechte Panelisierung kann beim Trennen der Nutzen Spannungsrisse in Keramikkondensatoren verursachen.

- Lötstoppstege: Geben Sie minimale Lötstoppstege zwischen Pads vor, typischerweise 4 mil, um Brückenbildung bei Fine-Pitch-ICs zu vermeiden.

2. DFT-Datenanforderungen

DFT wird oft zu spät berücksichtigt. Das führt dann zu teuren Nadelbett-Fixtures, die kritische Netze gar nicht erreichen.

- Zugänglichkeit der Testpunkte: Fordern Sie, dass alle kritischen Netze einen Testpunkt auf der Unterseite des PCB haben. So wird ein einseitiger In-Circuit-Test (ICT) möglich, der deutlich günstiger ist.

- Abstand um Testpunkte: Geben Sie einen Mindestabstand, z. B. 50 mil, zwischen Testpunkten und hohen Bauteilen vor, damit Prüfspitzen nicht kollidieren oder beschädigt werden.

- JTAG/Boundary Scan: Stellen Sie bei komplexen Digitalbaugruppen sicher, dass die JTAG-Kette geroutet und zugänglich ist. So lassen sich Verbindungen zwischen ICs ohne physische Prüfspitzen testen.

- Netlist: Liefern Sie immer eine IPC-356-Netlist mit. Damit kann der Hersteller die elektrische Konnektivität aus den Gerber-Daten mit der Konnektivität des Schaltplans vergleichen.

Verwandte Ressourcen

Zentrale Risiken: Ursachen, Früherkennung und Prävention

Wer konkrete Fehlertypen versteht, kann DFM-Prüfungen sinnvoll priorisieren. Besonders kritisch sind Defekte unter Bottom-Terminated Components wie QFNs (Quad Flat No-lead) und BGAs.

1. Voids in QFN- und BGA-Bauteilen

Voids sind Lufteinschlüsse in der Lötverbindung. Zu viele Voids verringern die Wärmeableitung und schwächen die mechanische Stabilität.

- Risiko: Hochleistungs-QFNs überhitzen, weil die Wärme wegen void-behafteter Lötstellen schlecht abgeführt wird.

- Prävention (DFM): Setzen Sie qfn reflow best practices to reduce voids um. Dazu gehört eine Fensterstruktur in der Lotpastenöffnung des Thermal Pads. Statt eines großen Pastenblocks, der Gase einschließt, wird ein Raster kleinerer Quadrate mit etwa 50-70% Abdeckung gedruckt. So entstehen Ausgasungskanäle, über die flüchtige Bestandteile während des Reflow entweichen können.

2. BGA-Lötfehler: Brückenbildung und Opens

BGA-Lötstellen sind anspruchsvoll, weil sie optisch verdeckt sind.

- Risiko: Head-in-Pillow-(HiP)-Defekte, bei denen die Lotkugel auf der Paste sitzt, aber keine vollständige Benetzung stattfindet.

- Prävention (DFM/Prozess): Es braucht eine strenge bga voiding control: stencil, reflow, and x-ray criteria.

- Schablone: Nutzen Sie elektropolierte Schablonen mit trapezförmigen Öffnungen, damit sich die Paste sauber auslöst.

- Reflow: Optimieren Sie das Soak-Zonen-Profil. Brennt das Flussmittel zu früh ab, verhindert Oxidation die Benetzung.

- Röntgenkriterien: Definieren Sie klare Pass/Fail-Grenzen. Für IPC Class 2 gilt typischerweise, dass Voids kleiner als 25% der Ball-Fläche bleiben müssen.

3. Tombstoning

Hierbei richtet sich ein kleines passives Bauteil während des Reflow an einem Ende auf.

- Ursache: Ungleiche Benetzungskräfte, oft weil ein Pad an eine große Massefläche angebunden ist und als Wärmesenke wirkt, während das andere nur an einer schmalen Leiterbahn hängt.

- Prävention (DFM): Verwenden Sie Thermal Reliefs an Massepads. So wird der Wärmestrom begrenzt und beide Pads erreichen gleichzeitig die Reflow-Temperatur.

4. Shadowing

Beim Wellen- oder Selektivlöten können große Bauteile die Lötwelle abschirmen, sodass kleinere Komponenten dahinter nicht ausreichend benetzt werden.

- Prävention (DFM): Legen Sie Abstandsregeln fest, die sich an der Förderrichtung durch die Lötanlage orientieren.

Validierung und Abnahme: Prüfungen und Pass-Kriterien

| Test / Prüfung | Methode | Pass-Kriterien (Beispiel) | Nachweis |

|---|---|---|---|

| Elektrische Durchgängigkeit | Flying Probe / Fixture | 100% der Netze geprüft, keine Opens/Shorts | E-Test-Bericht |

| Kritische Abmessungen | Messung | Erfüllt Zeichnungstoleranzen | Prüfprotokoll |

| Integrität von Beschichtung / Füllung | Mikroschliff | Keine Voids/Risse außerhalb der IPC-Grenzen | Mikroschliff-Fotos |

| Lötbarkeit | Benetzungstest | Ausreichende Benetzung, kein Dewetting | Lötbarkeitsbericht |

| Warpage | Ebenheitsmessung | Innerhalb der Spezifikation, z. B. ≤0,75% | Warpage-Protokoll |

| Funktionale Validierung | FCT | Alle Fälle bestanden, Log gespeichert | FCT-Logs |

Wie weisen Sie nach, dass DFM und DFT erfolgreich umgesetzt wurden? Sie brauchen einen Validierungsplan, der zu Ihren Zielen für die NPI-Bestückung passt.

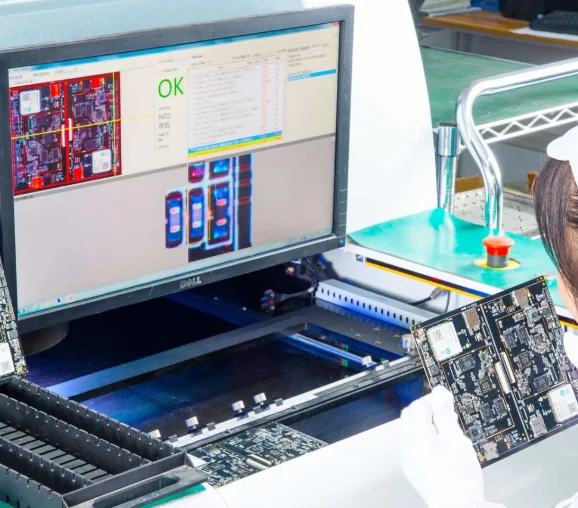

Automated Optical Inspection (AOI)

AOI ist die erste Verteidigungslinie. Kameras prüfen Bauteilvorhandensein, Polarität, Versatz und Lötqualität.

- Pass-Kriterien: Keine fehlenden Bauteile, korrekt ausgerichtete Polaritätsmarken, Lötfillets nach IPC-Anforderung.

- Grenze: Unter BGAs oder QFNs kann AOI nicht sehen.

X-Ray Inspection (Axi)

Für BGA- und QFN-Bewertung ist Röntgenprüfung unverzichtbar.

- Pass-Kriterien: Die Vorgaben aus bga voiding control: stencil, reflow, and x-ray criteria müssen erfüllt sein. Voids <25%, gleichmäßige Ball-Geometrie, keine Brückenbildung.

- Anwendung: 100%-Prüfung bei Prototypen, Stichprobenprüfung in der Serienfertigung.

- Mehr dazu: Röntgeninspektion

In-Circuit Test (ICT) und Flying Probe

Hier zeigt sich der Nutzen von DFT.

- ICT: Prüft mit einem Fixture im Nadelbett alle Netze gleichzeitig. Schnell, aber mit hohen Fixture-Kosten verbunden. Erfordert definierte Testpunkte aus dem DFT.

- Flying Probe: Tastet Punkte mit Robotik ab. Kein Fixture nötig, aber langsamer. Ideal für Prototypen.

- Pass-Kriterien: Alle passiven Werte innerhalb der Toleranz, keine Kurzschlüsse oder Unterbrechungen auf aktiven Netzen.

Functional Circuit Test (FCT)

Dies ist die abschließende funktionale Validierung. Die Baugruppe wird bestromt und muss ihre reale Funktion ausführen.

- Pass-Kriterien: Gerät bootet, Firmware wird geladen, I/O-Ports reagieren.

Checkliste zur Lieferantenqualifizierung: RFQ, Audit und Rückverfolgbarkeit

Wenn Sie einen Partner auswählen, der Sie beim Reduzieren von PCBA-Defekten mit DFM und DFT unterstützt, sollte diese Checkliste in die Bewertung einfließen.

1. Engineering-Fähigkeiten

- Führt der Lieferant vor dem Tooling zwingend ein DFM-Review durch?

- Liefert er einen detaillierten DFM-Bericht und nicht nur ein einfaches Pass/Fail, inklusive Risiken wie Acid Traps oder Slivers?

- Kann er alternative Footprints empfehlen, um die Ausbeute zu verbessern?

- Siehe DFM-Richtlinien für den erwartbaren Standard.

2. Prozesskontrolle

- Sind SPI-Systeme inline vorhanden? SPI verhindert einen großen Teil typischer Lötfehler.

- Stehen Röntgensysteme im eigenen Haus zur Verfügung?

- Kann der Lieferant qfn reflow best practices to reduce voids sicher beherrschen, etwa per Vakuum-Reflow oder Profiloptimierung?

3. Rückverfolgbarkeit und Qualitätssystem

- Ist der Standort nach ISO 9001 oder IATF 16949 zertifiziert?

- Gibt es Rückverfolgbarkeit auf Bauteilebene, also die Zuordnung konkreter Bauteillose zu konkreten Seriennummern?

- Prüfen Sie das vorhandene Qualitätssystem.

Wie Sie den richtigen DFM/DFT-Ansatz wählen: Zielkonflikte und Entscheidungsregeln

Nicht jede Baugruppe braucht dieselbe DFM/DFT-Intensität. Mit den folgenden Regeln lassen sich Kosten und Risiko gegeneinander abwägen.

Szenario A: Einfache Consumer-Elektronik mit niedrigem Stückpreis und hohem Volumen

- Strategie: Schwerpunkt auf DFM, um Ausbeute zu maximieren und Zykluszeit zu senken.

- DFT: Minimal. Verlassen Sie sich auf AOI und funktionale Stichproben.

- Trade-off: Eine etwas höhere Feldausfallrate wird akzeptiert, um die Stückkosten niedrig zu halten.

Szenario B: Medizin- und Automotive-Produkte mit hoher Zuverlässigkeit und mittlerem Volumen

- Strategie: Konsequentes DFM und DFT.

- DFT: 100% ICT und 100% Funktionstest.

- Trade-off: Höhere NRE-Kosten für Fixtures und Testprogrammierung, dafür nahezu keine Feldausfälle.

- Spezifikum: Strikte Einhaltung von bga voiding control: stencil, reflow, and x-ray criteria.

Szenario C: Schnelles Prototyping

- Strategie: "Soft" DFM. Es werden nur Showstopper behoben, die den Aufbau verhindern.

- DFT: Flying-Probe-Test ohne Fixture-Kosten.

- Trade-off: Höhere Prüfzeit pro Einheit, dafür schnellere Verfügbarkeit.

FAQ: Kosten, Lieferzeit, DFM-Daten, Materialien und Tests

1. Erhöhen zusätzliche DFM/DFT-Anforderungen den Angebotspreis? Ja, zunächst schon. Engineering-Aufwand und Test-Fixtures als NRE verursachen zusätzliche Anfangskosten. Gleichzeitig sinken jedoch Stückkosten und Gesamtkosten häufig, weil Ausbeute steigt und Nacharbeit entfällt.

2. Wie viel Zeit verlängert ein DFM-Review die Lieferzeit? Typischerweise um 1–2 Tage. Ein fundiertes DFM-Review findet statt, bevor Material bestellt wird. Diese kurze Verzögerung verhindert oft wochenlange Terminverluste durch später entdeckte Unfertigbarkeit.

3. Kann DFM ein schlechtes Schaltungsdesign korrigieren? Nein. DFM stellt sicher, dass eine Platine gebaut werden kann, nicht dass sie elektrisch richtig funktioniert. Enthält der Schaltplan Logikfehler, wird die Platine korrekt gefertigt und fällt trotzdem funktional durch.

4. Was ist der Unterschied zwischen DFM und DFA? DFM bezieht sich meist auf die Leiterplattenfertigung, also etwa Ätzen und Bohren. DFA bezieht sich auf die Baugruppenmontage, also Bestückung, Löten und Freiräume. In der Praxis wird DFM oft als Oberbegriff für beides verwendet.

5. Brauche ich ICT, wenn ich bereits einen Funktionstest habe? Im Idealfall ja. ICT zeigt, welches Bauteil oder Netz ausgefallen ist, zum Beispiel "Widerstand R5 offen". Der Funktionstest zeigt meist nur, dass die Baugruppe nicht funktioniert. Für Diagnose und Reparatur ist ICT deutlich schneller.

6. Welchen Einfluss haben Materialien auf DFM? Die Materialwahl, etwa High Tg FR4, beeinflusst, wie sich die Platine beim Reflow ausdehnt. Ein unpassender CTE zwischen Bauteil und Board ist eine häufige Ursache für Lötstellen-Ermüdung.

7. Wie kommuniziert man DFM-Hinweise am besten? Legen Sie eine Read-Me-Datei oder ein PDF in das Gerber-Zip. Besondere Anforderungen wie "Do not X-out arrays" oder "Mask plug vias at U1" sollten dort ausdrücklich aufgeführt sein.

Angebot oder DFM-Review anfragen: Was Sie senden sollten

Sie möchten Ihre PCBA für die Serienfertigung optimieren? Dann senden Sie Ihr Datenpaket für ein umfassendes DFM-Review.

Checkliste für die Angebotsanfrage:

- Gerber-Dateien (RS-274X): Kupferlagen, Lötstoppmaske, Siebdruck, Bohrdaten und Pastenlagen.

- Bill of Materials (BOM): Excel-Datei mit Manufacturer Part Numbers (MPN) und Referenzkennzeichen.

- Centroid-Datei (Pick and Place): X-Y-Koordinaten und Rotationsdaten.

- Assembly Drawings: PDF mit Bauteilpositionen und Polaritätsmarkierungen.

- Testanforderungen: Beschreibung der gewünschten Testabdeckung, z. B. ICT, FCT oder Burn-in.

Glossar: Zentrale Begriffe

| Begriff | Bedeutung | Warum das in der Praxis zählt |

|---|---|---|

| DFM | Design for Manufacturability: Layoutregeln zur Reduzierung von Defekten. | Verhindert Nacharbeit, Verzögerungen und versteckte Kosten. |

| AOI | Automated Optical Inspection zur Erkennung von Löt- und Montagefehlern. | Erhöht Abdeckung und entdeckt frühe Abweichungen. |

| ICT | In-Circuit Test zur Prüfung von Unterbrechungen, Kurzschlüssen und Werten. | Schneller struktureller Test für Serienbaugruppen. |

| FCT | Functional Circuit Test mit bestromter Baugruppe und Funktionsprüfung. | Bestätigt die reale Funktion unter Last. |

| Flying Probe | Fixtureloser elektrischer Test mit beweglichen Prüfspitzen. | Geeignet für Prototypen und kleine bis mittlere Stückzahlen. |

| Netlist | Verbindungsdefinition zum Vergleich von Design und gefertigtem PCB. | Erkennt Opens und Shorts vor der Montage. |

| Stackup | Lagenaufbau mit Kernen, Prepregs, Kupfergewichten und Dicken. | Beeinflusst Impedanz, Warpage und Zuverlässigkeit. |

| Impedanz | Kontrolliertes Leitungsverhalten für High-Speed- und RF-Signale, z. B. 50Ω. | Verhindert Reflexionen und SI-Probleme. |

| ENIG | Electroless Nickel Immersion Gold als Oberflächenfinish. | Gute Balance aus Lötbarkeit und Ebenheit; Nickeldicke beachten. |

| OSP | Organic Solderability Preservative als Oberflächenfinish. | Kostengünstig, aber empfindlicher bei Handling und Mehrfach-Reflow. |

Fazit: Nächste Schritte

Zu verstehen, wie sich PCBA-Defekte mit DFM und DFT reduzieren lassen, ist eine Investition in Lebensdauer und Marktvertrauen Ihres Produkts. Wenn Sie klare Spezifikationen für Schablonendesign, Reflow-Profile und Testzugänglichkeit definieren, wird aus einem schwer steuerbaren Fertigungsablauf ein kontrollierbarer und reproduzierbarer Prozess.

Beziehen Sie Ihren Fertigungspartner früh in die Designphase ein. Eine gemeinsame Durchsicht von qfn reflow best practices to reduce voids sowie bga voiding control: stencil, reflow, and x-ray criteria spart Zeit und Kapital. Sorgen Sie für Transparenz im Datenpaket, validieren Sie konsequent und wählen Sie einen Lieferanten, der Qualität als gemeinsame Verantwortung versteht.