Inferenzserver-Leiterplatte: Kurzantwort (30 Sekunden)

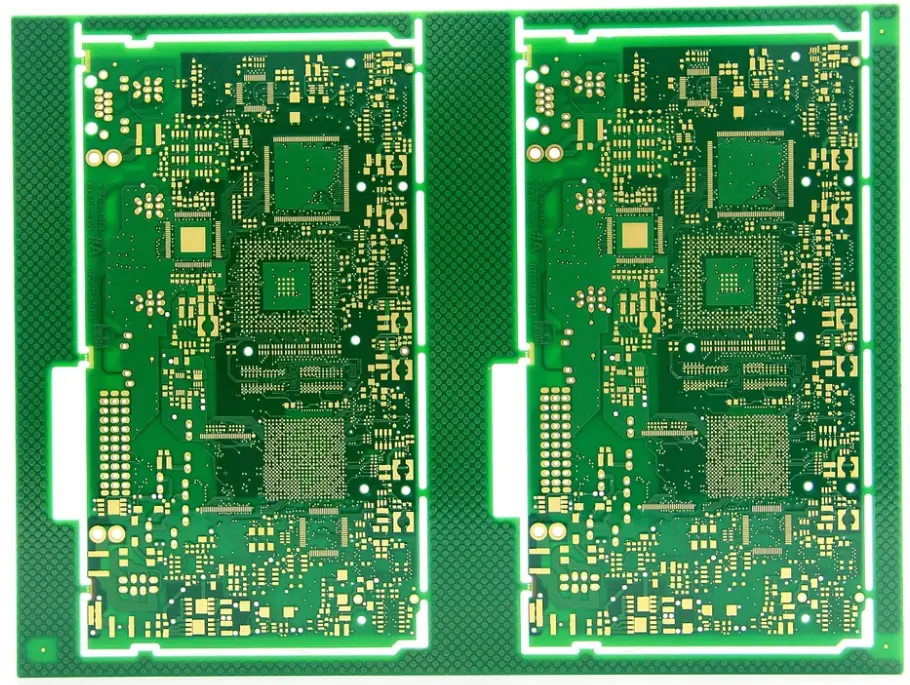

Das Design und die Herstellung einer Inferenzserver-Leiterplatte erfordert ein Gleichgewicht zwischen der Integrität von Hochgeschwindigkeitssignalen und einer hohen thermischen Dichte. Im Gegensatz zu Allzweck-Computerplatinen müssen diese Leiterplatten einen dauerhaften Durchsatz für KI-Workloads ohne Latenzspitzen unterstützen, die durch Signalverschlechterung oder thermisches Throttling verursacht werden.

- Materialauswahl ist entscheidend: Standard-FR-4 ist für PCIe Gen5/6-Geschwindigkeiten unzureichend. Sie müssen Materialien mit extrem geringen Verlusten (z. B. Panasonic Megtron 6/7/8 oder Isola Tachyon) verwenden, um die Einfügedämpfung zu minimieren.

- Backdrilling ist obligatorisch: Um Signalreflexionen in Hochgeschwindigkeitsverbindungen (>25 Gbit/s) zu reduzieren, müssen Via-Stubs bis auf 8-10 mil an die Signalschicht entfernt (rückgebohrt) werden.

- Dickes Kupfer für die Stromversorgung: Inferenzbeschleuniger ziehen erheblichen Strom. Stromversorgungsebenen erfordern oft 2oz oder 3oz Kupfer, um den IR-Abfall zu minimieren und die Wärmeverteilung zu steuern.

- Strenge Impedanzkontrolle: Differenzielle Paare erfordern normalerweise 85Ω oder 100Ω ±5% Toleranz. Abweichungen verursachen Jitter und Datenpaketverluste in KI-Verarbeitungsströmen.

- Strategie für das Wärmemanagement: Layouts mit hoher Dichte in 1U- oder 2U-Gehäuseformaten erfordern oft das Einbetten von Kupfer-Coins oder die VIPPO-Technologie (Via-in-Pad Plated Over), um Wärme von GPUs oder ASICs abzuleiten.

- Lagenanzahl und Stackup: Die meisten Inferenzserverplatinen reichen von 12 bis 24 Lagen, um eine dichte Verdrahtung zu ermöglichen und Hochgeschwindigkeitssignale zwischen Masseebenen zu isolieren.

Wann Inferenz-Server-PCBs zum Einsatz kommen (und wann nicht)

Das Verständnis des spezifischen Einsatzbereichs einer Inferenz-Server-Leiterplatte stellt sicher, dass Sie einen einfachen Controller nicht überdimensionieren oder einen missionskritischen KI-Knoten nicht unterspezifizieren.

Wann Inferenz-Server-PCB-Standards anzuwenden sind:

- KI/ML-Edge-Einsatz: Sie bauen Server, die darauf ausgelegt sind, vorab trainierte Modelle (Inferenz) für Videoanalyse, Verarbeitung natürlicher Sprache oder Datenverarbeitung für autonomes Fahren auszuführen.

- Integration von Hochgeschwindigkeitsbeschleunigern: Das Board muss mehrere PCIe-basierte Beschleuniger (GPUs, TPUs, FPGAs) hosten oder damit verbunden sein, die PCIe Gen5- oder CXL-Schnittstellen erfordern.

- Dichte Rechenknoten: Sie entwerfen 1U-Server-PCB- oder 2U-Server-PCB-Formfaktoren, bei denen der Luftstrom eingeschränkt ist und die Wärmeleitfähigkeit der Leiterplatte ein primärer Kühlpfad ist.

- Low-Latency-Anforderungen: Die Anwendung erfordert Echtzeitverarbeitung, bei der Signaljitter oder Rauschen der Stromversorgungsintegrität zu inakzeptablen Latenzen führen könnten (z. B. Finanzhandel oder Sicherheitssysteme).

- ARM-basierte Architekturen: Sie verwenden Designs für ARM-Server-PCBs mit hoher Kernanzahl (wie Ampere Altra), die spezifische Impedanzen des Stromversorgungsnetzwerks (PDN) erfordern.

Wann stattdessen Standard-PCB-Regeln gelten:

- Allzweck-Webhosting: Standard-Commodity-Server, auf denen grundlegender Web-Traffic läuft, benötigen nicht die teuren verlustarmen Materialien, die für KI-Inferenz erforderlich sind.

- IoT-Sensorknoten: Datenerfassungsgeräte mit niedriger Geschwindigkeit benötigen keine impedanzkontrollierten Platinen mit hoher Lagenanzahl.

- Massive Modell-Trainingscluster: Obwohl ähnlich, haben "Trainings"-Server im Vergleich zu Standard-Inferenzknoten oft noch höhere Leistungsdichten (Kilowatt pro Board) und andere Interconnect-Topologien (NVLink/Infinity Fabric).

- Veraltete Industriesteuerungen: Systeme, die mit Frequenzen unter 1 GHz oder Standard-Ethernet-Geschwindigkeiten laufen, benötigen kein Backdrilling oder ultraglatte Kupferfolie.

Inferenz-Server-PCB-Regeln und Spezifikationen (wichtige Parameter und Grenzwerte)

Die folgende Tabelle skizziert die nicht verhandelbaren Fertigungsparameter für eine hochzuverlässige Inferenz-Server-Leiterplatte. APTPCB (APTPCB PCB Factory) verwendet diese Basislinien, um sicherzustellen, dass die Platinen die Leistungsstufen der IPC-6012 Klasse 3 erfüllen.

| Regelkategorie | Empfohlener Wert / Bereich | Warum es wichtig ist | Wie man es überprüft | Wenn ignoriert (Fehlermodus) |

|---|---|---|---|---|

| Basismaterial | Low Loss / Ultra-Low Loss (Df < 0,005 @ 10GHz) | Verhindert Signaldämpfung über lange Leiterbahnen, die bei Server-Boards typisch sind. | IPC-TM-650 Testmethode; Materialdatenblatt prüfen (z. B. Megtron 7). | Massiver Datenpaketverlust; System kann bei Gen5-Geschwindigkeiten keine Verbindung herstellen. |

| Lagenanzahl | 12 – 24 Lagen | Bietet ausreichend Routing-Kanäle und Masseabschirmung für Hochgeschwindigkeitsspuren. | Überprüfung des Stackup-Diagramms; Querschnittsanalyse (Schliffbild). | Übermäßiges Übersprechen; Unfähigkeit, alle Signale zu routen; EMI-Ausfälle. |

| Kupferfolienrauheit | HVLP (Hyper Very Low Profile) oder VLP-2 | Raues Kupfer wirkt bei hohen Frequenzen wie ein Widerstand (Skin-Effekt), was den Verlust erhöht. | SEM (Rasterelektronenmikroskop)-Inspektion der Folienoberfläche. | Erhöhte Einfügedämpfung; Verschlechterung der Signalintegrität bei >10GHz. |

| Impedanztoleranz | ±5% (Ziel 85Ω oder 100Ω) | Passt sich der Treiber-/Empfängerimpedanz an, um Signalreflexionen zu verhindern. | TDR (Time Domain Reflectometry)-Coupons auf dem Produktionsnutzen. | Signalreflexion (Ringing); reduzierte Augenöffnungsdiagramm; Datenfehler. |

| Backdrilling-Tiefe | Stub-Länge < 10 mils (0,25mm) | Lange Via-Stubs wirken als Antennen/Kondensatoren, verursachen Resonanz und Signaleinbrüche. | Röntgenprüfung; Querschnittsanalyse. | Spitzen in der "Bitfehlerrate"; bestimmte Frequenzen werden vollständig blockiert. |

| Aspektverhältnis (Bohrung) | 10:1 bis 12:1 (Standard); bis zu 16:1 (Erweitert) | Stellt sicher, dass die Galvanisierlösung eindringen und die Via-Hülse zuverlässig beschichten kann. | Schliffbildanalyse der Plattierungsdicke in der Mitte des Vias. | Unterbrechungen in Vias (Hülsenrisse) während thermischer Zyklen. |

| Plattierungsdicke | > 25µm (1 mil) durchschnittlich im Loch | Bietet mechanische Festigkeit, um der thermischen Ausdehnung dicker Leiterplatten standzuhalten. | CMI- oder Querschnittsmessung. | Eckenrisse oder Hülsenermüdung, die zu intermittierenden Ausfällen führen. |

| Lötstopplack-Steg | Min 3-4 mils (0,075-0,1mm) | Verhindert Lötbrücken zwischen Fine-Pitch-BGA-Pads. | AOI (Automated Optical Inspection). | Kurzschlüsse unter teuren BGA-Komponenten (GPUs/CPUs). |

| Verzug / Wölbung & Verdrehung | < 0,5% (IPC Klasse 3 Ziel) | Große Server-Boards (E-ATX) müssen für die BGA-Montage flach bleiben. | Shadow Moiré Messgerät. | Offene BGA-Verbindungen (Head-in-Pillow-Defekte); Montageausfall. |

| Glasübergangstemperatur (Tg) | High Tg (> 170°C) | Verhindert Materialerweichung und Z-Achsen-Ausdehnung während Reflow und Betrieb. | DSC (Differential Scanning Calorimetry). | Pad-Cratering; Delamination während der Montage oder bei Hochlastbetrieb. |

| CAF-Beständigkeit | Anti-CAF-Materialien erforderlich | Hohe Spannungsverzerrung in Server-Stromschichten kann leitfähiges Fadenwachstum verursachen. | SIR (Surface Insulation Resistance)-Prüfung; CAF-Testcoupons. | Katastrophale Kurzschlüsse, die sich Monate nach der Bereitstellung entwickeln. |

| Via-in-Pad | VIPPO (Plated Over) für BGAs | Ermöglicht das Routing aus Fine-Pitch-BGAs (0,8 mm oder weniger) ohne Dog-Bone-Traces. | Visuelle Inspektion; Querschnitt. | Lötstellen-Hohlräume in BGA-Verbindungen, wenn sie nicht korrekt gekappt/plattiert sind. |

Inferenz-Server-PCB-Implementierungsschritte (Prozess-Checkpoints)

Der Weg vom Schaltplan zu einer physischen Inferenzserver-Leiterplatte erfordert einen disziplinierten Workflow. Jeder Schritt unten enthält eine spezifische Aktion und eine Abnahmeprüfung, um kostspielige Neudrehs (Respins) zu vermeiden.

Stackup-Definition & Materialauswahl

- Aktion: Definieren Sie den Lagenaufbau (z. B. 16 Lagen) mithilfe einer High-Speed PCB-Materialbibliothek. Balancieren Sie das Kupfergewicht (Leistung) mit der dielektrischen Dicke (Impedanz) aus.

- Parameter: Sorgen Sie für Symmetrie, um Verzug zu vermeiden. Wählen Sie Prepreg-Glasarten (z. B. 1035, 1078), um den Glasfaser-Gewebe-Effekt (Fiber Weave Effect) zu minimieren.

- Prüfung: Führen Sie eine Simulation mit einem Impedanzlöser aus. Bestätigen Sie, dass die Leiterbahnbreiten herstellbar sind (z. B. >3,5 mils).

Floorplanning & Thermische Simulation

- Aktion: Platzieren Sie Hochleistungskomponenten (CPUs, Beschleuniger, VRMs), um den Luftstrom im 1U/2U-Gehäuse zu optimieren.

- Parameter: Halten Sie Hochgeschwindigkeits-Transceiver in der Nähe von Randsteckern oder Backplane-Schnittstellen, um die Leiterbahnlängen zu verkürzen.

- Prüfung: Führen Sie eine vorläufige thermische Simulation durch. Stellen Sie sicher, dass sich Hotspots nicht überschneiden.

Power Integrity (PI) Analyse

- Aktion: Entwerfen Sie das Power Delivery Network (PDN), um hohe transiente Ströme (di/dt), die für KI-Workloads typisch sind, zu bewältigen.

- Parameter: Ziel-PDN-Impedanz unter 10 mΩ bis 100 MHz.

- Prüfung: Überprüfen Sie, ob der DC-IR-Abfall bei allen Hauptstromschienen <2% ist.

High-Speed Routing & Backdrill-Definition

- Aktion: Routen Sie zuerst die PCIe Gen5/6- und DDR5-Spuren. Weisen Sie spezifische Schichten zu, um Via-Übergänge zu minimieren.

- Parameter: Markieren Sie alle High-Speed-Vias für das Backdrilling. Definieren Sie die "must-not-cut"-Schichten (Schichten, die nicht geschnitten werden dürfen) deutlich in den Designdateien.

- Prüfung: Führen Sie eine Signal Integrity (SI) Simulation (Channel Operating Margin) durch.

DFM (Design for Manufacturing) Überprüfung

- Aktion: Senden Sie Gerber-Dateien an APTPCB für eine umfassende DFM-Prüfung vor der Fertigung.

- Parameter: Überprüfen Sie minimale Restringe (Annular Rings), Aspektverhältnisse und Abstände auf internen Stromversorgungsebenen.

- Prüfung: Bestätigen Sie, dass die Toleranzen für die Backdrill-Tiefe erreichbar sind (normalerweise ±5 mils).

Fertigung: Laminieren & Bohren

- Aktion: Der Hersteller führt sequenzielles Laminieren (falls HDI) oder Standardlaminieren durch.

- Parameter: Steuern Sie die Temperatur des Presszyklus, um eine vollständige Aushärtung des Harzes ohne Hohlräume sicherzustellen.

- Prüfung: Röntgenprüfung der Lagenregistrierung (Bohrung-zu-Kupfer-Ausrichtung).

Fertigung: Plattieren & Oberflächenfinish

- Aktion: Tragen Sie eine Kupferbeschichtung auf, gefolgt von einem Oberflächenfinish (ENIG, Immersion Silver oder ENEPIG).

- Parameter: Stellen Sie sicher, dass die Kupferdicke an der Lochwand Klasse 3 (>25µm) entspricht.

- Prüfung: Querschnittsanalyse eines Testcoupons, um die Integrität der Plattierung zu überprüfen.

Elektrischer Test (BBT & TDR)

- Aktion: 100% Netzlisten-Test (Flying Probe oder Nadelbett) und Impedanz-Test.

- Parameter: TDR-Coupons müssen innerhalb von ±5% oder ±10% wie spezifiziert bestehen.

- Prüfung: Konformitätsbescheinigung (CoC), die TDR-Pass-Ergebnisse anzeigt.

Inferenz-Server-PCB Fehlerbehebung (Fehlermodi und Behebungen)

Wenn eine Inferenzserver-Leiterplatte ausfällt, liegt dies oft an subtilen Problemen der Signalintegrität oder an thermischer Belastung und nicht an einfachen offenen Schaltkreisen. Verwenden Sie diesen Leitfaden, um die Grundursachen zu diagnostizieren.

Symptom 1: Hohe Bitfehlerrate (BER) bei PCIe-Links

- Mögliche Ursachen:

- Falsche Backdrilling-Tiefe (Stub zu lang gelassen).

- Glasfaser-Gewebe-Effekt (Versatz zwischen differenziellen Paaren).

- Impedanzfehlanpassung aufgrund von Überätzung.

- Prüfungen: TDR-Analyse der fehlerhaften Verbindung; Querschnitt des Via-Stubs; VNA-Messung der Einfügedämpfung.

- Behebung: Respin mit engerer Backdrill-Toleranz oder Verwendung von "Zickzack"-Routing (10-Grad-Winkel), um den Glasfaser-Gewebe-Effekt abzuschwächen.

- Prävention: Geben Sie "Spread Glass" oder mechanisch gespreiztes Gewebe in den Materialhinweisen an.

Symptom 2: Intermittierende Systemabstürze unter Last

- Mögliche Ursachen:

- Power Integrity-Fehler (Spannungseinbruch), der CPU/GPU-Instabilität verursacht.

- Thermische Abschaltung aufgrund schlechter Wärmeübertragung durch die Leiterplatte.

- Prüfungen: Messen Sie die Spannungswelligkeit an den Lastkondensatoren mit einem Oszilloskop; Überprüfen Sie Wärmebildkamerabilder auf Hotspots.

- Behebung: Entkopplungskondensatoren hinzufügen; Kupfergewicht auf Stromebenen erhöhen; Verwenden Sie Heavy Copper PCB Technologie.

- Prävention: Führen Sie während des Designs eine strenge PI-Simulation (DC-Abfall und AC-Impedanz) durch.

Symptom 3: BGA Pad Cratering oder Verbindungsbruch

- Mögliche Ursachen:

- CTE-Fehlanpassung zwischen dem großen BGA-Gehäuse und dem PCB-Material.

- Übermäßige Biegung der Leiterplatte bei Montage oder Installation.

- Prüfungen: Dye-and-Pry-Test; Mikro-Schliffbild der gebrochenen Verbindung.

- Behebung: Verwenden Sie ein Material mit höherem Tg und niedrigerem Z-Achsen-CTE; Fügen Sie Eckkleber/Underfill zu BGAs hinzu.

- Prävention: Stellen Sie Stackup-Symmetrie sicher, um Verzug zu reduzieren; Verwenden Sie harzgefüllte Vias (VIPPO) für besseren mechanischen Halt.

Symptom 4: Leitfähige anodische Filament (CAF) Kurzschlüsse

- Mögliche Ursachen:

- Eindringen von Feuchtigkeit in die Glasbündel in Kombination mit hoher Spannungsverzerrung.

- Schlechte Bohrqualität (Mikrorisse im Harz).

- Prüfungen: Isolationswiderstandsprüfung; Mikro-Schliffbild, das Kupferwachstum entlang von Glasfasern zeigt.

- Behebung: Verschrottete Platinen können nicht repariert werden. Die neue Produktion muss Anti-CAF-Materialien verwenden.

- Prävention: Spezifizieren Sie "Anti-CAF" oder "CAF-resistentes" Laminat (z. B. Isola 370HR oder Megtron-Serie).

Symptom 5: Delamination nach Reflow

- Mögliche Ursachen:

- In der Leiterplatte eingeschlossene Feuchtigkeit (Popcorning).

- Inkompatible Harzsysteme in Hybrid-Stackups.

- Prüfungen: Visuelle Inspektion auf Blasenbildung; Rasterakustikmikroskopie (SAM).

- Behebung: Platinen vor der Montage backen (120°C für 4-6 Stunden).

- Prävention: Lagern Sie PCBs in vakuumversiegelten Beuteln mit Feuchtigkeitsindikatorkarten; Befolgen Sie die MSL-Richtlinien.

Wie man eine Inferenz-Server-Leiterplatte auswählt (Designentscheidungen und Kompromisse)

Die Wahl der richtigen Spezifikation für eine Inferenzserver-Leiterplatte beinhaltet das Abwägen von Kompromissen zwischen Leistung, thermischer Kapazität und Kosten.

1. Material: Mid-Loss vs. Ultra-Low Loss

- Mid-Loss (z. B. Isola 370HR): Akzeptabel für PCIe Gen3 oder kurze Gen4 Leiterbahnen. Geringere Kosten, einfacher zu verarbeiten.

- Ultra-Low Loss (z. B. Megtron 7, Tachyon): Zwingend erforderlich für PCIe Gen5/6 und lange Leiterbahnen (>10 Zoll). Deutlich teurer und erfordert spezielle Laminierparameter.

- Entscheidung: Wenn Ihr Inferenzserver Gen5-Beschleuniger verwendet, müssen Sie verlustarme Materialien verwenden. Gehen Sie hier keine Kompromisse ein.

2. Formfaktor: 1U vs. 2U/4U

- 1U-Server-PCB: Extrem platzbeschränkt. Erfordert horizontale Speichersteckplätze und optimierte Luftstromkanäle. Das Wärmemanagement hängt stark davon ab, dass die PCB die Wärme an das Gehäuse abgibt.

- 2U/4U-Server-PCB: Ermöglicht vertikale Riser-Karten und größere Kühlkörper. Das PCB-Layout kann etwas weniger dicht sein, aber die schiere Größe der Platine (oft E-ATX oder kundenspezifisch) bringt Herausforderungen beim Verzug mit sich.

- Entscheidung: 1U-Designs erfordern oft HDI (High Density Interconnect), um das Routing unterzubringen, was die Boardkosten erhöht, aber Rack-Platz spart.

3. Through-Hole vs. HDI (High Density Interconnect)

- Through-Hole: Standard-Multilayer-Platinen. Billiger, begrenzt aber die Routing-Dichte unter großen BGAs.

- HDI (Microvias): Verwendet lasergebohrte blinde und begrabene Vias (Blind/Buried Vias). Unverzichtbar für das Routing von BGAs mit 0,65 mm oder kleinerem Pitch, die in modernen KI-Chips zu finden sind.

- Entscheidung: Die meisten High-End-KI-Server-PCB-Designs erfordern mittlerweile mindestens Typ-3-HDI (gestapelte Microvias), um die Hochgeschwindigkeitssignale vom Hauptprozessor nach außen zu führen.

4. Oberflächenfinish: ENIG vs. Immersion Silver vs. OSP

- ENIG: Hervorragende Haltbarkeit und flache Oberfläche. Gut für die meisten Anwendungen, kann aber unter "Black Pad" leiden, wenn es nicht kontrolliert wird.

- Immersion Silver: Besser für sehr hochfrequente Signale (kein Nickel-Skin-Effekt). Häufig bei Supercomputer-/Serverplatinen.

- OSP: Am billigsten, aber kürzeste Haltbarkeit. Selten für hochzuverlässige Server-Boards verwendet.

- Entscheidung: Wählen Sie Immersion Silver für erstklassige Signalintegrität; wählen Sie ENIG für allgemeine Zuverlässigkeit und Haltbarkeit.

Inferenz-Server-PCB FAQ (Kosten, Vorlaufzeit, häufige Defekte, Abnahmekriterien, Design for Manufacturability (DFM) Dateien)

F: Was ist die typische Lagenanzahl für eine KI-Inferenz-Server-Leiterplatte? A: Die meisten Inferenzserverplatinen liegen zwischen 12 und 24 Lagen.

- 12-16 Lagen: Üblich für Single-Socket Edge-Inferenzserver.

- 18-24 Lagen: Erforderlich für Dual-Socket-Rechenzentrumsserver mit mehreren Beschleunigerkarten, um die Routing-Dichte und Stromebenen zu verwalten.

F: Wie wirkt sich Backdrilling auf die Kosten der Leiterplatte aus? A: Backdrilling erhöht die Kosten je nach Anzahl der Bohrungen um 10-20%.

- Es fügt einen sekundären CNC-Bohrprozess hinzu.

- Es erfordert eine spezielle Inspektion (Röntgen), um die Tiefenkontrolle zu überprüfen.

- Es ist jedoch billiger, als mehr Schichten hinzuzufügen, um Stubs zu vermeiden.

F: Kann ich FR-4 für einen PCIe Gen5 Inferenzserver verwenden? A: Im Allgemeinen nein. Standard-FR-4 hat einen zu hohen Dissipationsfaktor (Df) (~0,02), was zu übermäßigem Signalverlust bei 16-32 GHz führt.

- Sie benötigen Materialien mit Df < 0,005 (z. B. Megtron 6/7).

- Die Verwendung von FR-4 wird wahrscheinlich zu einem Kanal führen, der die Konformitätsprüfung nicht besteht.

F: Was sind die Abnahmekriterien für Class 3 Server PCBs? A: IPC-6012 Klasse 3 "High Reliability" (Hohe Zuverlässigkeit) ist der Standard.

- Restring (Annular Ring): Kein Ausbrechen (Breakout) erlaubt (Tangentialität ist nicht akzeptabel).

- Plattierung: Minimum 25µm Durchschnitt in Löchern.

- Optisch: Kein freiliegendes Kupfer, keine Blasenbildung, strenge Lötstopplack-Registrierung.

- Zuverlässigkeit: Muss thermische Stresstests ohne Delamination bestehen.

F: Welche Dateien muss ich für eine DFM-Prüfung senden? A: Um ein genaues Angebot und DFM zu erhalten, senden Sie:

- Gerber-Dateien (RS-274X): Alle Kupferschichten, Lötstopplack, Bestückungsdruck, Bohrdateien.

- IPC-356 Netzliste: Wichtig für die Überprüfung der elektrischen Konnektivität anhand der Grafiken.

- Fertigungszeichnung (Fab Drawing): Spezifizierung von Material, Stackup, Impedanztabellen und Bohrtabelle.

- Readme: Anmerkung spezieller Anforderungen wie "Backdrill layers X to Y" oder "Press-fit connector holes".

F: Wie handhaben Sie das Wärmemanagement für 1000W+ KI-Server? A: Wir verwenden verschiedene Techniken:

- Dickkupfer (Heavy Copper): 2oz oder 3oz Innenlagen für die Stromverteilung.

- Thermische Vias: Dichte Anordnungen von Vias unter heißen Bauteilen, um Wärme an innere Schichten zu übertragen.

- Eingebettete Coins (Embedded Coins): Einsetzen einer massiven Kupfermünze direkt in die Leiterplatte unter der GPU/CPU (erweiterte Funktion).

F: Was ist die Vorlaufzeit (Lead Time) für die Herstellung von Inferenz-Server-PCBs? A: Die Vorlaufzeiten sind aufgrund der Materialverfügbarkeit und Komplexität länger als bei Standardplatinen.

- Standard: 15-20 Werktage.

- Quick Turn: 8-12 Werktage (wenn Material auf Lager ist).

- Hinweis: Hochgeschwindigkeitsmaterialien (Megtron, Tachyon) können eigene Beschaffungsvorlaufzeiten von 2-4 Wochen haben, wenn sie nicht auf Lager sind.

F: Warum ist die Impedanzkontrolle für diese Platinen so wichtig? A: Bei hohen Geschwindigkeiten verhält sich die Leiterbahn wie eine Übertragungsleitung.

- Wenn sich die Impedanz ändert (z. B. Leiterbahnbreite variiert), wird ein Teil des Signals zurückreflektiert.

- Diese Reflexion verursacht Rauschen (Jitter) und schließt das "Augendiagramm", wodurch 0en und 1en ununterscheidbar werden.

F: Unterstützen Sie Press-Fit-Steckverbinder für Server-Backplanes? A: Ja, Press-Fit-Steckverbinder (Einpresstechnik) sind Standard für Server-I/O.

- Die Bohrungstoleranz ist extrem eng (z. B. ±0,05 mm).

- Wir kontrollieren die fertige Lochgröße (Finished Hole Size, FHS) streng, um einen ordnungsgemäßen Halt der Pins ohne Beschädigung der Hülse sicherzustellen.

F: Was ist der Unterschied zwischen "Core"- und "Foil"-Konstruktion in Stackups? A: Dies wirkt sich auf Kosten und Registrierung aus.

- Core-Konstruktion: Verwendet ausgehärtete Laminatkerne. Bessere Dimensionsstabilität.

- Foil-Konstruktion (Folienaufbau): Verwendet mehr Prepreg. Kann billiger sein, kann aber während der Laminierung mehr Bewegung haben.

- Empfehlung: Für Serverplatinen mit vielen Lagen empfehlen wir spezifische Kernkonstruktionen, um Verzug zu minimieren.

Ressourcen für Inferenz-Server-PCB (verwandte Seiten und Tools)

Um Sie bei Ihrem Design- und Beschaffungsprozess weiter zu unterstützen, bietet APTPCB detaillierte Leitfäden zu verwandten Technologien:

- Server-Rechenzentrums-PCB: Überblick über unsere Fähigkeiten für den breiteren Rechenzentrumsmarkt.

- High Speed PCB: Tiefer Einblick in Signalintegrität, Materialien und Designregeln.

- Multilayer PCB: Verständnis von Stackups, Lamination und Registrierung für hohe Lagenzahlen.

- Megtron PCB: Besonderheiten der Panasonic-Materialfamilie, die für KI-Server unerlässlich ist.

- Backplane PCB: Für Designs mit großen passiven Interconnect-Boards.

- HDI PCB: Wenn Ihr Inferenzserver Microvias für dichtes BGA-Routing benötigt.

Inferenz-Server-PCB Glossar (Schlüsselbegriffe)

| Begriff | Definition | Kontext in Inferenzserver-Leiterplatte |

|---|---|---|

| PCIe Gen5 | Peripheral Component Interconnect Express, Generation 5. | Die Standardschnittstelle zum Anschließen von KI-Beschleunigern, läuft mit 32 GT/s. Erfordert Ultra-Low-Loss-PCB. |

| Insertion Loss (Einfügedämpfung) | Der Verlust an Signalleistung auf dem Weg entlang einer Leiterbahn. | Gemessen in dB/Zoll. Muss minimiert werden, um sicherzustellen, dass die Signale intakt beim Empfänger ankommen. |

| Backdrilling | Kontrolliertes Tiefenbohren, um den ungenutzten Teil eines durchkontaktierten Lochs (Stub) zu entfernen. | Unverzichtbar zur Reduzierung von Signalreflexionen in Hochgeschwindigkeits-Vias (>10 Gbps). |

| Df (Dissipation Factor) | Ein Maß dafür, wie viel Energie vom Isoliermaterial absorbiert wird. | Niedriger ist besser. Standard-FR4 hat ~0,02; Serverqualität ist <0,005. |

| Dk (Dielectric Constant) | Ein Maß für die Fähigkeit des Materials, elektrische Energie zu speichern. | Beeinflusst Signalaufbreitungsgeschwindigkeit und Impedanz. Stabiles Dk ist entscheidend. |

| PAM4 | Pulse Amplitude Modulation 4-level. | Ein Codierungsschema, das in Hochgeschwindigkeitsverbindungen (wie PCIe Gen6/Ethernet) verwendet wird und sehr empfindlich auf Rauschen reagiert. |

| CTE (Coefficient of Thermal Expansion) | Wie stark sich das Material beim Erhitzen ausdehnt. | Eine Fehlanpassung zwischen PCB und Komponenten verursacht Risse in Lötstellen. |

| Tg (Glass Transition Temperature) | Die Temperatur, bei der das PCB-Harz von hart zu weich übergeht. | Server-Boards benötigen hohes Tg (>170°C), um Montage und Hitze zu überstehen. |

| VIPPO | Via-in-Pad Plated Over. | Eine Technologie, bei der Vias in Pads platziert, mit Harz gefüllt und überplattiert werden. Wird für dichte BGAs verwendet. |

| Fiber Weave Effect (Glasfaser-Gewebe-Effekt) | Signalversatz (Skew), verursacht durch das Glasfasermuster im PCB-Laminat. | Kann Timing-Fehler in differenziellen Paaren verursachen. Abgemildert durch "Zickzack"-Routing oder gespreiztes Glas (Spread Glass). |

| Impedance Control (Impedanzkontrolle) | Fertigungsprozess, um sicherzustellen, dass der Leiterbahnwiderstand dem Design entspricht (z. B. 85Ω). | Entscheidend zur Vermeidung von Signalreflexionen. |

| Press-Fit (Einpresstechnik) | Eine lötfreie Verbindungsmethode, bei der nachgiebige Stifte in Leiterplattenlöcher gedrückt werden. | Standard für Serveranschlüsse (RJ45, Cages), um thermische Belastungen durch Löten zu vermeiden. |

Angebot für Inferenzserver-Leiterplatte anfordern (Design for Manufacturability (DFM) Überprüfung + Preisgestaltung)

Bereit, Ihre Inferenzserver-Leiterplatte vom Design in die Produktion zu überführen? APTPCB ist spezialisiert auf Serverplatinen mit vielen Lagen und hohen Geschwindigkeiten mit strikter Class 3 Konformität.

Senden Sie uns Ihre Daten für eine umfassende DFM-Überprüfung:

- Gerber-Dateien: Kompletter Satz einschließlich Bohrdateien.

- Stackup-Diagramm: Spezifizierung von Materialtyp (z. B. Megtron 7) und Lagenreihenfolge.

- Bohrzeichnung: Deutliche Markierung von Backdrill-Positionen und -Tiefen.

- Impedanzanforderungen: Zielwerte und spezifische Lagen.

- Volumen & Vorlaufzeit: Prototypenmenge vs. Massenproduktionsziele.

Fazit (nächste Schritte)

Die erfolgreiche Herstellung einer Inferenzserver-Leiterplatte ist eine Meisterleistung der Feinmechanik und erfordert eine perfekte Synchronisation von verlustarmen Materialien, kontrolliertem Tiefenbohren und strengen Impedanztests. Egal, ob Sie ein kompaktes 1U-Server-PCB für Edge-Analytics oder ein massives KI-Server-PCB für das Rechenzentrum bauen, der Unterschied zwischen Erfolg und Misserfolg liegt oft in den Fertigungsdetails. Indem Sie sich an strenge Designregeln halten und mit einem fähigen Hersteller zusammenarbeiten, stellen Sie sicher, dass Ihre Hardware die niedrige Latenz und den hohen Durchsatz liefert, die für moderne KI-Workloads erforderlich sind.