Die Entwicklung von Hardware für offene Funkzugangsnetze (O-RAN) erfordert die strikte Einhaltung von Standards für Signalintegrität und Wärmemanagement, wodurch ein umfassender O-RAN RU PCB-Leitfaden für Ingenieure unerlässlich ist. Die Funkeinheit (RU) in einer O-RAN-Architektur übernimmt die kritische Umwandlung zwischen digitalen Signalen und Funkwellen, wobei oft Massive MIMO (mMIMO)-Arrays und Hochleistungsverstärkung zum Einsatz kommen. Im Gegensatz zu herkömmlichen proprietären Basisstationen müssen O-RAN RUs nahtlos mit verschiedenen Distributed Units (DUs) zusammenarbeiten, was eine präzise Impedanzkontrolle und geringe passive Intermodulation (PIM) erfordert.

Dieser Leitfaden bietet umsetzbare Spezifikationen, Fertigungschecklisten und Schritte zur Fehlerbehebung, um sicherzustellen, dass Ihre O-RAN RU PCB die strengen Anforderungen der 5G NR-Bereitstellung erfüllt. APTPCB (APTPCB PCB Factory) ist spezialisiert auf die Herstellung dieser komplexen Hochfrequenzplatinen und stellt sicher, dass die Designabsicht perfekt in das physische Produkt umgesetzt wird.

Kurzantwort (30 Sekunden)

Für Ingenieure, die sofortige Anweisungen zur O-RAN RU PCB-Fertigung benötigen, sind hier die kritischen Parameter, die vor Beginn des Layouts oder der Bestellung von Prototypen gesichert werden müssen:

- Materialauswahl: Verwenden Sie für HF-Schichten verlustarme, hochfrequente Laminate (z. B. Rogers 4000-Serie oder gleichwertig). Hybrid-Lagenaufbauten, die Hochfrequenzmaterialien mit hoch-Tg FR4 kombinieren, sind Standard, um Kosten und Leistung auszugleichen.

- Lagenaufbau: Erwarten Sie 12 bis 20+ Lagen für mMIMO-Einheiten. Ein symmetrischer Aufbau ist entscheidend, um Verzug während des Reflows zu verhindern, insbesondere bei gemischten Materialien.

- PIM-Minderung: Spezifizieren Sie explizit "Low PIM"-Anforderungen. Verwenden Sie rückseitig behandelte Folien (RTF) oder Kupfer mit sehr niedrigem Profil (VLP). Vermeiden Sie HASL-Oberflächen; bevorzugen Sie Immersion Silver oder ENEPIG.

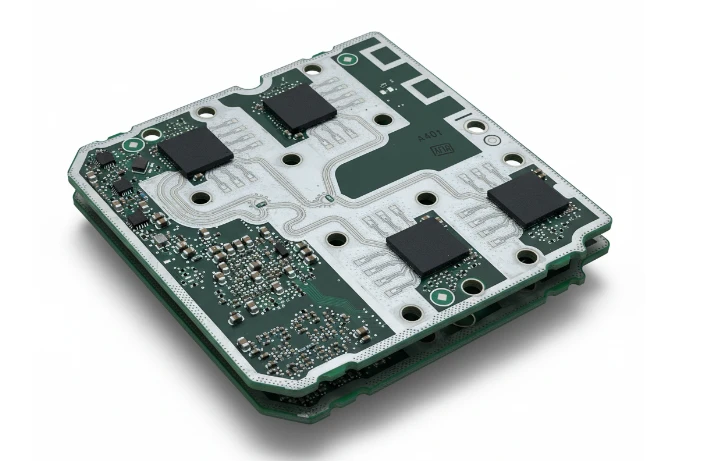

- Wärmemanagement: Leistungsverstärker (PAs) erzeugen erhebliche Wärme. Implementieren Sie Kupfer-Coin-Technologie, dickes Kupfer (2oz+) oder dichte thermische Via-Arrays, die mit leitfähigem Epoxidharz gefüllt sind.

- Impedanzkontrolle: Halten Sie 50Ω Single-Ended- und 100Ω Differentialpaare mit einer Toleranz von ±5% auf HF-Leitungen ein.

- Bohren: Backdrilling ist für Hochgeschwindigkeits-Signal-Vias (eCPRI-Schnittstellen) zwingend erforderlich, um Stub-Resonanz und Signalreflexion zu minimieren.

Die Funkeinheit (RU) PCB-Leitfaden gilt (und wann nicht)

Das Verständnis des Umfangs dieses O-RAN RU PCB-Leitfadens stellt sicher, dass Sie diese strengen Regeln nur dort anwenden, wo es notwendig ist, um Kosten und Entwicklungsaufwand zu optimieren.

Wann dieser Leitfaden strikt zu befolgen ist

- 5G Massive MIMO-Einheiten: Designs, die 32T32R- oder 64T64R-Antennenarrays umfassen, bei denen die Lagenregistrierung und das Übersprechen kritisch sind.

- Hochleistungs-Funkeinheiten: RUs, die in Sub-6GHz- oder mmWave-Bändern betrieben werden und aktive Kühlung oder eingebettete Kupfer-Coins zur Wärmeableitung erfordern.

- Mixed-Signal-Designs: Platinen, die HF-Frontends, digitale Beamforming-ASICs und optische Übertragung (eCPRI) auf einer einzigen Leiterplatte integrieren.

- Interoperabilitätstests: Wenn die Hardware die Konformitätstests der O-RAN Alliance für offene Fronthaul-Schnittstellen bestehen muss.

- Außeninstallationen: Hardware, die rauen Umgebungsbedingungen ausgesetzt ist und hohe Zuverlässigkeit (IPC Klasse 3) sowie spezifische Oberflächenschutzmaßnahmen erfordert.

Wann Standard-Leiterplattenregeln ausreichen (und dieser Leitfaden überflüssig ist)

- Nur-Digital-Einheiten (DU/CU): Obwohl Regeln für Hochgeschwindigkeits-Digitaldesign gelten, sind die spezifischen HF-Material- und PIM-Einschränkungen der RU für Distributed oder Central Units nicht relevant.

- Niederfrequenz-IoT-Gateways: Geräte, die auf älteren Bändern (2G/3G) oder einfachen Wi-Fi-Modulen arbeiten, benötigen oft keine teuren Hybrid-Stackups oder VLP-Kupfer.

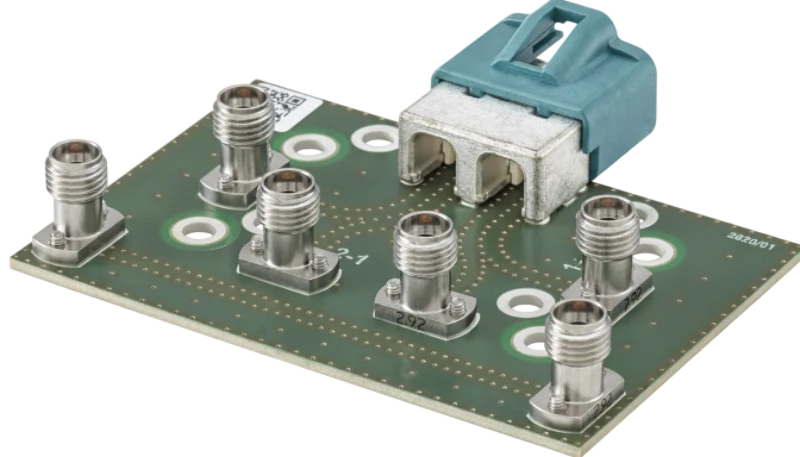

- Einfache Breakout-Boards: Testvorrichtungen oder Steckeradapter, die keine aktiven HF-Signale oder Hochgeschwindigkeits-Datenströme übertragen.

- Unterhaltungselektronik: Standard-FR4-Designs für Telefone oder Laptops haben nicht die gleichen thermischen Dichte- oder PIM-Anforderungen wie RUs der Infrastrukturklasse.

Regeln & Spezifikationen

Die folgende Tabelle beschreibt die nicht verhandelbaren Regeln für die Herstellung von O-RAN RU PCBs. Diese Werte leiten sich aus den besten Praktiken der Industrie und den Fertigungsdaten von APTPCB ab.

| Regelkategorie | Empfohlener Wert / Bereich | Warum es wichtig ist | Wie zu überprüfen | Wenn ignoriert |

|---|---|---|---|---|

| Dielektrizitätskonstante (Dk) | 3.0 – 3.5 (HF-Schichten) | Ein niedriger Dk reduziert die Signalausbreitungsverzögerung und die kapazitive Kopplung in Hochfrequenzschaltungen. | Materialdatenblatt prüfen (z.B. Rogers 4350B, Tachyon 100G). | Signal-Timing-Fehler und reduzierte effektive Bandbreite. |

| Verlustfaktor (Df) | < 0.003 @ 10GHz | Minimiert die Signaldämpfung und Wärmeentwicklung innerhalb des dielektrischen Materials. | VNA-Messung an Testcoupons. | Übermäßiger Signalverlust, wodurch die Zellabdeckung reduziert wird. |

| Kupferrauheit | VLP (Very Low Profile) oder HVLP | Raues Kupfer erhöht die Skineffektverluste und PIM bei 5G-Frequenzen. | SEM-Analyse oder Angabe des Folientyps in den Fertigungsnotizen. | Hohe Einfügedämpfung und schlechte PIM-Leistung. |

| Impedanztoleranz | ±5% (HF), ±10% (Digital) | Passt Übertragungsleitungen an Quelle/Last an, um Reflexionen (VSWR) zu verhindern. | TDR (Time Domain Reflectometry)-Tests an Coupons. | Hohes VSWR, Leistungsreflexion und potenzielle PA-Schäden. |

| Wärmeleitfähigkeit | > 0.6 W/m-K (Dielektrikum) | Stellt sicher, dass sich die Wärme von PAs seitlich zu thermischen Vias oder Kühlkörpern ausbreitet. | Thermische Simulation und Materialauswahl. | Hotspots, die zu Komponentenausfällen oder thermischem Throttling führen. |

| Via-Struktur | Blind, Buried & Backdrilled | Reduziert Signalstubs, die bei hohen Frequenzen als Antennen oder Filter wirken. | Querschnittsanalyse (Mikroschliff). | Signalresonanz, Datenkorruption auf eCPRI-Verbindungen. |

| Oberflächengüte | Tauchsilber / ENEPIG | Nickel in ENIG ist ferromagnetisch und verursacht PIM; HASL ist zu uneben für feine Raster. | RFA-Messung für Dicke und Zusammensetzung. | PIM-Fehler und schlechte Lötstellen-Zuverlässigkeit bei Fine-Pitch-BGAs. |

| Lötstopplack | LPI, spezifischer HF-Abstand | Maske über HF-Leitungen kann die Impedanz verändern und Verluste erhöhen. | Sichtprüfung und Neuberechnung der Impedanz. | Unvorhersehbare Impedanzverschiebungen und erhöhte dielektrische Verluste. |

| Lagenregistrierung | ±3 mil oder besser | Fehlausrichtung beeinflusst die Kopplung in breitseitig gekoppelten Strukturen und Striplines. | Röntgeninspektion der inneren Lagen. | Hohes Übersprechen und inkonsistente HF-Leistung zwischen Chargen. |

| Schälfestigkeit | > 0,8 N/mm | Hohe thermische Belastung während des Betriebs kann Leiterbahnen delaminieren, insbesondere bei PTFE-Materialien. | Schältest gemäß IPC-TM-650. | Leiterbahnablösung während der Montage oder des Feldbetriebs. |

| WAK (Z-Achse) | < 50 ppm/°C | Verhindert Tonnenrisse in durchkontaktierten Löchern während des Reflows und Betriebs. | TMA (Thermomechanische Analyse). | Intermittierende Unterbrechungen nach thermischer Zyklisierung. |

| Glasgewebeart | Spreizglas (z.B. 1067, 1078) | Verhindert den "Fasergewebseffekt", bei dem Differentialpaare unterschiedliche Dk-Werte aufweisen. | Mikroschliffprüfung. | Skew in Differentialpaaren, was die Signalintegrität beeinträchtigt. |

Implementierungsschritte

Die erfolgreiche Ausführung eines O-RAN RU PCB-Designs erfordert einen disziplinierten Arbeitsablauf. Befolgen Sie diese Schritte, um vom Konzept zu einer fertigungsfähigen Platine zu gelangen.

1. Den Hybrid-Lagenaufbau definieren

Beginnen Sie mit der Bestimmung der Lagenanzahl basierend auf dem BGA-Raster Ihres FPGA/ASIC und den Anforderungen an die HF-Leiterbahnführung.

- Aktion: Konsultieren Sie Ihren Fertiger, um einen Hybrid-Lagenaufbau unter Verwendung von Hochfrequenzmaterialien (wie RF Rogers Materialien) für äußere HF-Lagen und hoch-Tg FR4 für innere Digital-/Stromversorgungslagen zu definieren.

- Schlüsselparameter: Kupfergewicht ausgleichen, um Verbiegungen zu vermeiden.

- Abnahmekontrolle: Die Lagenaufbau-Simulation bestätigt, dass die Impedanzziele für alle Signallagen erreicht werden.

2. Bauteilplatzierung & HF-Isolation

Gruppieren Sie Komponenten nach Funktion: HF-Frontend, digitale Verarbeitung und Energieverwaltung.

- Aktion: Platzieren Sie Leistungsverstärker (PAs) nahe am Rand oder an Kühlkörper-Schnittstellen. Verwenden Sie Abschirmgehäuse oder Fence-Vias, um HF-Abschnitte zu isolieren.

- Schlüsselparameter: Isolationsabstand > 3x Leiterbahnbreite.

- Abnahmekontrolle: Die 3D-Layout-Überprüfung zeigt eine klare Trennung zwischen empfindlichen Empfängerpfaden (Rx) und Hochleistungs-Senderpfaden (Tx).

3. Thermisches Design & Coin-Integration

O-RAN RUs erzeugen massive Wärme. Standard-Thermovias reichen möglicherweise nicht aus.

- Aktion: Entwerfen Sie eingebettete Kupfer-Coins oder schwere Kupferflächen unter PAs. Wenn Vias verwendet werden, spezifizieren Sie eine leitfähige Epoxidharzfüllung (VIPPO).

- Schlüsselparameter: Thermischer Widerstand < 0,5 °C/W für den PCB-Pfad.

- Abnahmekontrolle: Die thermische Simulation beweist, dass die Sperrschichttemperaturen bei maximaler Last unter 105°C (oder dem spezifischen Bauteillimit) bleiben.

4. Routing & Impedanzkontrolle

Kritische HF- und eCPRI-Leitungen zuerst routen.

- Aktion: Verwenden Sie den Impedanzrechner, um Leiterbahnbreiten zu bestimmen. Vermeiden Sie 90-Grad-Biegungen; verwenden Sie für HF ein 45-Grad- oder gekrümmtes Routing.

- Schlüsselparameter: 50Ω Single-Ended, 100Ω Differential.

- Abnahmekontrolle: DRC (Design Rule Check) besteht ohne Verletzungen an kritischen Netzen.

5. PIM-Minderung im Layout

Passive Intermodulation kann die Empfängerempfindlichkeit beeinträchtigen.

- Aktion: Minimieren Sie die Anzahl der Vias in HF-Pfaden. Stellen Sie sicher, dass die Masseflächen durchgehend sind und gründlich mit Massevias verbunden sind. Vermeiden Sie spitze Winkel in der Kupferfüllung.

- Schlüsselparameter: PIM-Bewertung < -160 dBc.

- Abnahmekontrolle: Überprüfen Sie das Layout auf "schwimmende" Kupferinseln und entfernen Sie diese.

6. Backdrilling-Spezifikation

Identifizieren Sie Hochgeschwindigkeits-Vias, die eine Stub-Entfernung erfordern.

- Aktion: Markieren Sie Vias auf bestimmten Lagen für das Backdrilling in den Gerber-Dateien.

- Schlüsselparameter: Verbleibende Stub-Länge < 10 mil (0,25 mm).

- Abnahmekontrolle: Die Fertigungszeichnung gibt die Backdrill-Tiefe und den Durchmesser klar an.

7. DFM & Dateigenerierung

Vor dem Senden an die Produktion die Herstellbarkeit validieren.

- Aktion: Führen Sie eine umfassende DFM-Prüfung durch. Überprüfen Sie, ob die Seitenverhältnisse (Leiterplattendicke vs. Bohrdurchmesser) innerhalb der Leiterplattenfertigungskapazitäten liegen.

- Schlüsselparameter: Min. Bohrgröße 0,2 mm, Seitenverhältnis < 10:1 (Standard) oder 16:1 (fortgeschritten).

- Abnahmekontrolle: Saubere Gerber/ODB++-Dateien ohne Mehrdeutigkeiten.

8. Prototypenfertigung & -prüfung

Bestellen Sie eine kleine Charge zur Validierung.

- Aktion: Senden Sie Dateien an APTPCB. Fordern Sie TDR-Berichte und Materialzertifizierungen an.

- Schlüsselparameter: Lieferzeit (typischerweise 10-15 Tage für komplexe Hybridplatinen).

- Abnahmekontrolle: Physische Platinen bestehen die Sichtprüfung und erste Einschaltprüfungen.

Fehlermodi & Fehlerbehebung

Auch mit einem soliden O-RAN RU PCB-Leitfaden können während der Tests Probleme auftreten. Verwenden Sie dieses Fehlerbehebungs-Framework, um häufige Fehler zu diagnostizieren und zu beheben.

1. Hohe passive Intermodulation (PIM)

- Symptom: Reduzierte Uplink-Empfindlichkeit; Rauschpegel steigt, wenn der Sender aktiv ist.

- Ursachen: Ferromagnetische Materialien (Nickel) im Signalpfad, raue Kupferfolie, schlechte Lötstellen oder lose Abschirmung.

- Prüfungen: Überprüfen Sie, ob die Oberflächenveredelung Immersion Silver oder ENEPIG ist. Suchen Sie nach "Rostschrauben"-Effekten in Abschirmgehäusen.

- Behebung: Wechseln Sie zu nicht-magnetischen Oberflächenveredelungen. Verbessern Sie das Lotpastenvolumen an HF-Steckverbindern.

- Prävention: Verwenden Sie VLP-Kupfer und vermeiden Sie ENIG auf HF-Pads.

2. Signaldämpfung (Einfügedämpfung)

- Symptom: Schwaches Signal am Antennenanschluss; PA zieht übermäßigen Strom zur Kompensation.

- Ursachen: Falsches Dielektrikum, Lötstopplack über HF-Leitungen oder übermäßige Leiterbahnlänge.

- Prüfungen: Leiterbahnbreite und Dielektrikumsdicke im Querschnitt messen. Lötstopplacköffnung überprüfen.

- Behebung: Platine mit verlustärmerem Material (niedrigerer Df) neu fertigen. Lötstopplack von HF-Leiterbahnen entfernen.

- Prävention: Einfügedämpfung vor dem Layout genau simulieren, einschließlich Rauigkeitsfaktoren.

3. Thermische Abschaltung

- Symptom: RU schaltet nach Minuten Betrieb ab; PAs überhitzen.

- Ursachen: Unzureichende thermische Vias, Lötstellenhohlräume unter dem PA oder geringe Wärmeleitfähigkeit des Dielektrikums.

- Prüfungen: Röntgeninspektion auf Lötstellenhohlräume. Dicke der thermischen Via-Beschichtung überprüfen.

- Behebung: Anzahl der thermischen Vias erhöhen. Vakuum-Reflow verwenden, um Hohlräume zu reduzieren. Kupfer-Coins implementieren.

- Prävention: Detaillierte thermische Modellierung durchführen. Mit leitfähigem Epoxidharz gefüllte Vias verwenden (Typ VII).

4. Impedanzfehlanpassung (Hoher VSWR)

- Symptom: Signalreflexion, reduzierte Leistungsübertragung, potenzielle Beschädigung des Senders.

- Ursachen: Ätzvariationen, falsche Stackup-Höhe oder fehlende Referenzebenen.

- Prüfungen: TDR-Messung. Überprüfung auf Masseebenenlücken unter Signalleiterbahnen.

- Behebung: Komponenten des Anpassungsnetzwerks anpassen. Für zukünftige Revisionen Ätztoleranzen verschärfen.

- Prävention: Impedanz-Testcoupons auf der Leiterplatte anbringen. Die DFM-Richtlinien einhalten.

5. Delamination während des Reflow-Lötens

- Symptom: Blasenbildung oder Trennung zwischen den Schichten, insbesondere zwischen FR4- und PTFE-Materialien.

- Ursachen: Feuchtigkeitsaufnahme, CTE-Fehlanpassung oder unsachgemäßer Laminierungszyklus.

- Prüfungen: Backprotokolle überprüfen. Schnittstelle zwischen Hybridmaterialien analysieren.

- Behebung: Leiterplatten vor der Bestückung backen. Parameter des Laminierpresszyklus optimieren.

- Prävention: PCBs in feuchtigkeitskontrollierten Umgebungen lagern. Kompatible Prepregs für Hybrid-Stacks wählen.

6. Digital-HF-Übersprechen

- Symptom: Störstrahlung im HF-Spektrum, die mit digitalen Taktfrequenzen korreliert.

- Ursachen: Schlechte Isolation, gemeinsame Rückwege oder mangelnde Abschirmung.

- Prüfungen: Nahfeldsonden-Scanning zur Lokalisierung der Rauschquelle.

- Behebung: Abschirmgehäuse hinzufügen. Erdungsstich verbessern.

- Prävention: Analoge und digitale Massen physikalisch trennen und an einem einzigen Punkt verbinden (oder eine durchgehende gemeinsame Masse mit sorgfältiger Platzierung verwenden).

Designentscheidungen

Das Design einer O-RAN RU Leiterplatte beinhaltet Kompromisse. Hier erfahren Sie, wie Sie die häufigsten Entscheidungspunkte navigieren.

Hybrid- vs. Voll-Hochfrequenz-Lagenaufbau

- Hybrid (Empfohlen): Verwendet teures Rogers/Taconic-Material nur für die oberen/unteren HF-Schichten und Standard-FR4 für die inneren digitalen Schichten.

- Vorteile: Deutlich geringere Kosten, bessere mechanische Steifigkeit.

- Nachteile: Komplexer Laminierungsprozess, Potenzial für Verzug, wenn nicht ausgeglichen.

- Volle Hochfrequenz: Verwendet verlustarmes Material für alle Schichten.

- Vorteile: Beste elektrische Leistung, einfache CTE-Anpassung.

- Nachteile: Unerschwingliche Kosten für hohe Lagenzahlen, mechanisch weich (schwierig zu montieren).

Kupfer-Coin vs. Thermal-Via-Array

- Thermal-Vias:

- Vorteile: Günstig, Standardprozess.

- Nachteile: Begrenzte Wärmeübertragungsfähigkeit (ca. 50-70 W/m-K effektiv).

- Kupfer-Coin:

- Vorteile: Exzellente Wärmeübertragung (380 W/m-K), direkter Pfad von der Komponente zum Kühlkörper.

- Nachteile: Teuer, erfordert präzises Routing und Press-Fit- oder Bonding-Prozess.

- Entscheidung: Verwenden Sie Kupfer-Coins für PAs, die > 20W ableiten. Verwenden Sie Thermal-Vias für Treiber und LNA.

Auswahl der Oberflächenveredelung

- ENIG: Gut für flache Pads, enthält aber Nickel (schlecht für PIM). Für HF vermeiden.

- Immersion Silber: Exzellent für HF (geringe Verluste, kein Nickel), aber läuft leicht an. Erfordert sorgfältige Handhabung.

- ENEPIG: "Universelle" Veredelung. Gutes Drahtbonden, anständige HF-Leistung, aber teuer.

- OSP: Am günstigsten, gut für HF, aber kurze Haltbarkeit und schwierig für mehrere Reflow-Zyklen.

- Entscheidung: Immersion Silber ist der Standard für O-RAN RU PCBs aufgrund der PIM-Leistung.

Häufig gestellte Fragen

F1: Was ist der kritischste Faktor im O-RAN RU PCB-Design? Signalintegrität und PIM-Leistung sind von größter Bedeutung. Die Platine muss hohe Leistung verarbeiten, ohne das Signal zu verzerren oder Rauschen zu erzeugen, das den Empfänger "taub" macht.

F2: Warum ist Rückbohren (Backdrilling) für O-RAN-Leiterplatten notwendig? O-RAN-Einheiten verwenden oft Hochgeschwindigkeits-eCPRI-Schnittstellen (10Gbps/25Gbps). Vias, die interne Schichten verbinden, hinterlassen ungenutzte "Stubs", die Signale reflektieren. Rückbohren entfernt diese Stubs, um die Signalqualität zu erhalten.

F3: Kann ich Standard-FR4 für 5G O-RAN RUs verwenden? Im Allgemeinen nein. Standard-FR4 weist bei 5G-Frequenzen (3.5GHz und höher) hohe dielektrische Verluste und einen instabilen Dk auf, was zu übermäßigem Signalverlust und Phasenfehlern führt.

F4: Wie handhabt APTPCB die Laminierung von Hybrid-Lagenaufbauten? APTPCB verwendet optimierte Presszyklen, die die unterschiedlichen Aushärtungstemperaturen und Fließraten von FR4- und PTFE/Keramikmaterialien berücksichtigen, um eine starke Verbindung ohne Delamination zu gewährleisten.

F5: Was ist die typische Lieferzeit für eine O-RAN RU Leiterplatte? Aufgrund der Komplexität und der speziellen Materialien betragen die Lieferzeiten typischerweise 10-15 Arbeitstage für Prototypen und 3-4 Wochen für die Serienproduktion.

F6: Wie gebe ich PIM-Anforderungen in meinen Fertigungsnotizen an? Geben Sie explizit an: "Niedrige PIM-Konstruktion erforderlich. Passive Intermodulation < -160 dBc (2x43dBm Töne). Verwenden Sie VLP-Kupfer und eine nicht-magnetische Oberflächenveredelung."

F7: Was ist die beste Oberflächenveredelung zur Minimierung von PIM? Tauchsilber oder Tauchzinn sind am besten. OSP ist auch gut, aber weniger robust. Vermeiden Sie HASL und Standard-ENIG. F8: Unterstützt APTPCB eingebettete Kupfer-Coins? Ja, APTPCB unterstützt verschiedene Coin-Technologien, einschließlich T-Coins, I-Coins und U-Coins, die direkt in die Leiterplatte integriert sind, um ein überlegenes Wärmemanagement zu gewährleisten.

F9: Wie hoch ist die maximale Lagenanzahl für diese Platinen? Wir fertigen regelmäßig High-Density Interconnect (HDI)-Leiterplatten mit bis zu über 40 Lagen, obwohl die meisten O-RAN RUs im Bereich von 12-24 Lagen liegen.

F10: Wie überprüfe ich die Impedanz meines Designs vor der Bestellung? Verwenden Sie unseren Online-Impedanzrechner für erste Schätzungen, fordern Sie jedoch immer eine Lagenaufbau-Verifizierung von unseren CAM-Ingenieuren an, bevor Sie das Design finalisieren.

F11: Welche Lageranforderungen gelten für Immersion Silver-Leiterplatten? Sie müssen in vakuumversiegelten Beuteln mit Trockenmittel und Feuchtigkeitsindikatorkarten gelagert werden. Sie sollten innerhalb von 6 Monaten montiert werden, um Anlaufen zu verhindern.

F12: Können Sie Blind- und Buried-Vias für HDI-Designs verarbeiten? Ja, wir unterstützen mehrere Laminierungszyklen für Blind- und Buried-Vias, die für das Routing dichter mMIMO-Arrays unerlässlich sind.

Glossar (Schlüsselbegriffe)

| Begriff | Definition | Relevanz für O-RAN RU PCB |

|---|---|---|

| O-RAN | Open Radio Access Network (Offenes Funkzugangsnetz) | Die Architektur, die die Trennung von RU-, DU- und CU-Hardware definiert. |

| RU (Radio Unit) | Die Hardware-Komponente, die digitale Signale in HF umwandelt. | Das spezifische Gerät, das dieser PCB-Leitfaden behandelt. |

| mMIMO | Massive Multiple-Input Multiple-Output | Antennentechnologie mit vielen Sendern/Empfängern; erfordert komplexe PCBs mit hoher Lagenzahl. |

| PIM | Passive Intermodulation | Signalverzerrung, verursacht durch Nichtlinearitäten (wie magnetische Metalle) im HF-Pfad. |

| eCPRI | Enhanced Common Public Radio Interface | Die digitale Hochgeschwindigkeitsschnittstelle, die die RU mit der DU verbindet. |

| Dk (Dielektrizitätskonstante) | Ein Maß für die Fähigkeit eines Materials, elektrische Energie zu speichern. | Bestimmt Signalgeschwindigkeit und Impedanz; muss für HF niedrig und stabil sein. |

| Df (Verlustfaktor) | Ein Maß dafür, wie viel Signalenergie als Wärme im Material verloren geht. | Muss sehr niedrig sein (<0.003), um Signalverlust in 5G-Bändern zu verhindern. |

| Hybrid-Lagenaufbau | Ein PCB-Lagenaufbau, der verschiedene Materialien (z.B. FR4 + Rogers) verwendet. | Gleicht die hohen Kosten von HF-Materialien mit den strukturellen Anforderungen der Platine aus. |

| VLP-Kupfer | Very Low Profile Copper (Kupfer mit sehr niedrigem Profil) | Kupferfolie mit sehr geringer Rauheit. |

| Backdrilling | Ausbohren des ungenutzten Teils eines durchkontaktierten Lochs. | Entfernt Signalstubs, um die Signalintegrität bei hohen Geschwindigkeiten zu verbessern. |

| CTE | Wärmeausdehnungskoeffizient | Wie stark sich das Material bei Erwärmung ausdehnt. |

Fazit

Der erfolgreiche Einsatz von 5G-Infrastruktur hängt von der Qualität der Hardware der Funkeinheit ab. Indem Sie diesem O-RAN RU PCB-Leitfaden folgen, stellen Sie sicher, dass Ihre Designs nicht nur elektrisch überlegen sind – mit niedrigem PIM, präziser Impedanz und effizientem Wärmemanagement – sondern auch in großem Maßstab herstellbar sind.

Der Übergang von einem digitalen Prototyp zu einem feldbereiten HF-Kraftpaket erfordert einen Fertigungspartner, der die Nuancen von Hybridmaterialien und Hochfrequenzphysik versteht. APTPCB bringt jahrelange Erfahrung in der fortschrittlichen HF-Fertigung in Ihr Projekt ein und stellt sicher, dass Ihre O-RAN RUs in den anspruchsvollsten Netzwerken zuverlässig funktionieren.

Bereit, Ihr O-RAN-Design zu validieren? Laden Sie Ihre Gerber-Dateien noch heute für eine umfassende DFM-Überprüfung und ein genaues Angebot hoch.