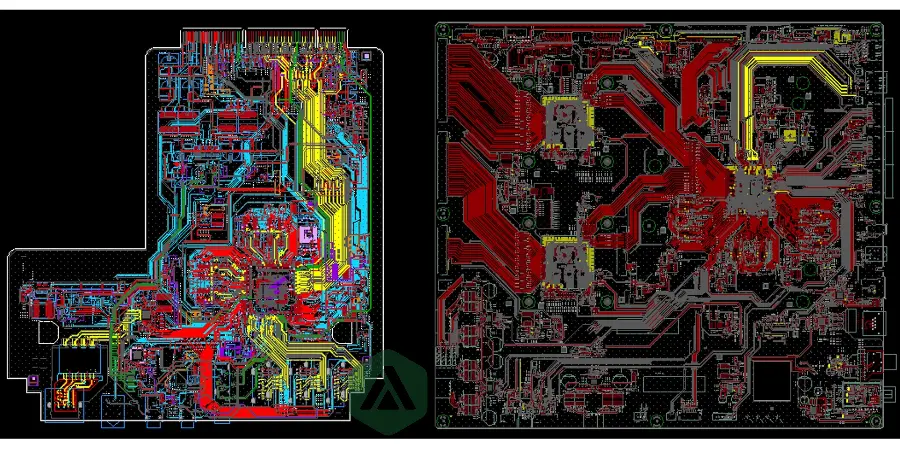

Die Optimierung der Herstellungskosten von Leiterplatten (PCB) erfordert ein ausgewogenes Verhältnis zwischen elektrischer Leistung, mechanischen Einschränkungen und Fertigungskapazitäten. Viele Ingenieure treiben unbeabsichtigt die Produktionskosten in die Höhe, indem sie engere Toleranzen oder komplexere Merkmale als nötig festlegen, oft ohne sich der spezifischen Kostentreiber im Fertigungsprozess bewusst zu sein. Wenn Sie den Zusammenhang zwischen Designentscheidungen und Fabrikabläufen verstehen, können Sie erhebliche Einsparungen erzielen und gleichzeitig eine hohe Zuverlässigkeit aufrechterhalten.

Wichtige Punkte

- Materialnutzung: Erfahren Sie, wie sich die Paneleffizienz auf den Stückpreis auswirkt und wie Sie für Standardarbeitspanelgrößen entwerfen.

- Strategie zur Ebenenanzahl: Methoden zur Reduzierung der Ebenenanzahl durch intelligenteres Routing und Komponentenplatzierung.

- Via-Technologie: Die Kostenauswirkungen von Blind-, Buried- und Microvias im Vergleich zur Standard-Through-Hole-Technologie.

- Oberflächenbeschaffenheit: Eine vergleichende Analyse von HASL, ENIG und OSP hinsichtlich Kosten im Vergleich zu Haltbarkeit und Ebenheit.

- Toleranzen: Wie die Lockerung unkritischer mechanischer und elektrischer Toleranzen die Ausschussquote senken und die Angebote senken kann.

Inhalt

- 1. Materialauswahl und Panelnutzung

- 2. Ebenenanzahl und Stapeloptimierung

- 3. Über Technologie- und Bohrbeschränkungen

- 4. Spur, Raum und Kupfergewicht

- 5. Oberflächenbeschaffenheit: Kosten und Leistung in Einklang bringen

- 6. So schätzen Sie die PCB-Kosten anhand von Gerber-Dateien ab

- 7. Mengen- und Lieferzeitstrategien

- 8. Test- und Inspektionsprotokolle

- 9. Fortgeschrittenes fertigungsgerechtes Design (DFM)

- 10. Beschaffung und Lieferantenauswahl

- Zusammenfassende Checkliste zur Kostenreduzierung

1. Materialauswahl und Panel-Nutzung

Das Rohlaminat macht einen erheblichen Teil der gesamten Leiterplattenkosten aus, insbesondere bei mehrschichtigen Leiterplatten. Die Wahl des richtigen Materials und die Sicherstellung, dass es effizient auf die Produktionsplatte des Herstellers passt, ist der erste Schritt zur kostengünstigen Leiterplattenherstellung.

Die Regel der Standardmaterialien

Regel: Halten Sie sich an den Standard FR4 (TG130-150), es sei denn, die Anwendung erfordert unbedingt Hochgeschwindigkeits- oder Hochtemperaturleistung. Warum es wichtig ist: Standard-FR4 wird in großen Mengen hergestellt, wodurch die Kosten niedrig bleiben. Spezialmaterialien wie Rogers oder High-TG FR4 (TG170+) können 2x bis 10x mehr pro Blatt kosten. So überprüfen Sie: Überprüfen Sie Ihr Datenblatt. Wenn Ihre Betriebstemperatur unter 100 °C liegt und die Signalfrequenzen unter 1–2 GHz liegen, ist Standard FR4 wahrscheinlich ausreichend. Häufiger Fallstrick: Angabe von TG180 „nur aus Sicherheitsgründen“ für ein Verbrauchergerät, das bei Raumtemperatur betrieben wird.

Effizienz der Panelauslastung

Leiterplattenhersteller fertigen die Leiterplatten nicht einzeln; Sie verarbeiten große Arbeitsplatten (normalerweise 18 x 24 Zoll, 21 x 24 Zoll oder größer). Der Prozentsatz dieses Panels, der von Ihren nutzbaren Leiterplatten bedeckt ist, bestimmt Ihren Materialabfall.

- Zielbereich: Ziel ist eine Panelauslastung von >80 %.

- Die Mathematik: Wenn Ihre Platine 50 mm x 50 mm groß ist und die Arbeitsplatte einen Abstand von 5 mm zulässt, bedeutet der Einbau eines Arrays, das nur 60 % der Platte nutzt, dass Sie für 40 % Ausschuss zahlen.

- Maßnahme: Informieren Sie sich frühzeitig bei Ihrem Hersteller über die bevorzugten Arbeitsplattengrößen. Manchmal kann eine Änderung einer Abmessung µm nur 1-2 mm eine zusätzliche Reihe oder Spalte von Brettern auf dem Paneel ermöglichen, wodurch die Stückkosten µm 15-20 % gesenkt werden.

Weitere Informationen zu Materialeigenschaften finden Sie in unserem Leitfaden zu FR4 PCB-Optionen.

2. Ebenenanzahl und Stapeloptimierung

Die Reduzierung der Layer-Anzahl ist eine der direktesten Möglichkeiten zur Kostensenkung, muss jedoch ohne Beeinträchtigung der Signalintegrität erfolgen.

Die Laminierungskosten

Jedes zusätzliche Schichtpaar führt zu einem Laminierungszyklus, mehr Prepreg-Material und einer längeren Verarbeitungszeit.

- Sprungkosten: Der Wechsel von 2 Schichten zu 4 Schichten erhöht die Kosten normalerweise µm 30–40 %. Durch den Wechsel von 4 auf 6 Schichten kommen weitere 20–30 % hinzu.

- Standardstapel: Halten Sie sich an eine gleichmäßige Anzahl von Schichten (2, 4, 6, 8). Ungerade Schichtenanzahlen (z. B. 5 Schichten) erfordern normalerweise einen nicht standardmäßigen Laminierungsprozess, der die Platte verziehen kann und aufgrund der Notwendigkeit einer besonderen Handhabung tatsächlich mehr kostet als eine 6-schichtige Platte.

Routing-Effizienz

Regel: Schöpfen Sie alle Routing-Möglichkeiten auf den äußeren Schichten aus, bevor Sie innere Schichten hinzufügen. Warum es wichtig ist: Ingenieure greifen aus Bequemlichkeitsgründen oft auf einen 6-Schichten-Stack zurück. So überprüfen Sie: Verwenden Sie Autorouter nur zur Schätzung; Manuelles Routing zeigt oft, dass ein 4-Lagen-Stapel realisierbar ist, wenn die Komponentenplatzierung optimiert ist. Häufiger Fallstrick: Verwendung eines 6-Lagen-Stapels ausschließlich für Leistungsebenen, wenn ein gegossenes Kupferpolygon auf einer Signalschicht ausreichen würde.

Sehen Sie sich unsere Richtlinien zum PCB-Aufbau an, um die Standarddicken von Dielektrika zu verstehen.

3. Über Technologie- und Bohrbeschränkungen

Bohren ist der langsamste und teuerste mechanische Prozess bei der Leiterplattenfertigung. Die Anzahl der Löcher, ihre Größe und die verwendete Technologie (mechanisch vs. Laser) treiben die Kosten erheblich in die Höhe.

Bohrergröße und Seitenverhältnis

Regel: Halten Sie die Mindestgröße der mechanischen Bohrer ≥ 0,2 mm (8 mil) und Seitenverhältnisse < 8:1 ein. Warum es wichtig ist:

- Bohrerverschleiß: Kleinere Bohrer brechen häufiger und haben eine kürzere Lebensdauer.

- Stapelung: Hersteller können 2–3 Platten stapeln, µm gleichzeitig zu bohren, wenn die Löcher >0,3 mm sind. Bei Löchern <0,2 mm müssen die Platten einzeln gebohrt werden, was die Maschinenzeit verdreifacht.

- Seitenverhältnis: Das Verhältnis der Plattendicke zum Lochdurchmesser. Wenn eine Platine 1,6 mm dick ist und das Loch 0,2 mm groß ist, beträgt das Verhältnis 8:1. Verhältnisse über 10:1 machen das Galvanisieren schwierig und erfordern fortschrittliche chemische Prozesse, die die Kosten erhöhen.

Hdi und Advanced Vias

High Density Interconnect (HDI)-Funktionen wie Blind- und Buried Vias erfordern eine sequentielle Laminierung.

- Kostenauswirkungen: Das Hinzufügen von Blind Vias kann die Platinenkosten µm 50–80 % im Vergleich zu einer standardmäßigen Durchsteckplatine erhöhen.

- Alternative: Bevor Sie sich für die HDI PCB-Technologie entscheiden, versuchen Sie, die Komponentendichte zu reduzieren oder die Platinengröße leicht zu vergrößern, um eine standardmäßige Durchsteckführung zu ermöglichen.

Lochanzahl

Regel: Minimieren Sie die Gesamtzahl der Löcher. Grenzwert: Viele Hersteller haben einen Grenzwert (z. B. 50 Löcher pro Quadratzoll oder 100.000 Löcher pro Charge), bei dem aufgrund übermäßiger Bohrerabnutzung und übermäßiger Maschinenzeit Zuschläge anfallen.

4. Spur, Leerzeichen und Kupfergewicht

Wenn die Grenzen der Ätzfähigkeiten überschritten werden, verringert sich die Ausbeute. Eine geringere Ausbeute bedeutet, dass der Hersteller mehr Platten produzieren muss, µm sicherzustellen, dass genügend gute Platten die Prüfung bestehen, und diese Kosten werden auf Sie umgelegt.

Spur-/Leerzeichentoleranzen

- Standard: 5/5 mil (0,127 mm) oder 6/6 mil (0,152 mm). Dies ist die „sichere Zone“ für die meisten Fabriken.

- Erweitert: 3/3 mil (0,076 mm) oder 4/4 mil.

- Kostentreiber: Um unter 4/4 Mil zu gehen, sind oft strengere Reinraumkontrollen und langsamere Ätzgeschwindigkeiten erforderlich. Es kann den Grundpreis µm 20-30% erhöhen.

Kupfergewicht

Regel: Verwenden Sie 1 Unze (35 µm) Kupfer, es sei denn, ein hoher Strom erfordert 2 Unzen oder mehr. Warum es wichtig ist: Schwereres Kupfer erfordert größere Abstände zwischen den Leiterbahnen, µm sauber ätzen zu können.

- Einschränkung: Für 1 Unze Kupfer beträgt der Mindestabstand normalerweise 4–5 mil. Bei 2 Unzen Kupfer steigt der minimale Platzbedarf auf 8-10 mil.

- Fallstrick: Angabe von 2 Unzen Kupfer auf allen Schichten, wenn nur die Stromschicht es benötigt. Wenn Sie einen hohen Strom benötigen, ziehen Sie Schwerkupfer-Leiterplatten-Lösungen nur dort in Betracht, wo es notwendig ist, oder verwenden Sie Sammelschienen.

5. Oberflächenbeschaffenheit: Kosten und Leistung in Einklang bringen

Die Oberflächenveredelung schützt das Kupfer vor Oxidation und gewährleistet die Lötbarkeit.

| Fertig | Kosten | Haltbarkeit | Planarität | Am besten für |

|---|---|---|---|---|

| HASL (bleihaltig) | Niedrigster | 12 Monate | Schlecht | Durchgangsloch, einfaches SMT |

| HASL (bleifrei) | Niedrig | 12 Monate | Schlecht | RoHS-Konformität, allgemeine Verwendung |

| OSP | Niedrig | 6 Monate | Ausgezeichnet | Fine-Pitch-SMT, kontrollierte Lagerung |

| ENIG | Mittel/Hoch | 12+ Monate | Ausgezeichnet | BGAs, Drahtbonden, Touchkontakte |

| Hartgold | Höchste | Jahre | Ausgezeichnet | Kantenverbinder, Verschleißfestigkeit |

Empfehlung: Verwenden Sie bleifreies HASL für allgemeine Elektronik. Führen Sie ein Upgrade auf ENIG nur durch, wenn Sie Fine-Pitch-Komponenten (BGA, QFN) haben oder eine perfekt ebene Oberfläche benötigen. Vermeiden Sie Hartgold, es sei denn, Sie verfügen über Randverbinder, die wiederholt eingesetzt/entfernt werden.

6. So schätzen Sie die PCB-Kosten anhand von Gerber-Dateien ab

Wenn Sie wissen, wie Sie die PCB-Kosten anhand von Gerber-Daten abschätzen können, können Sie Ihre Designs überprüfen, bevor Sie ein Angebot abgeben. Wenn ein CAM-Ingenieur Ihre Dateien überprüft, sucht er nach „Kostenverursachern“.

Die „Cost Adder“-Checkliste

- Nutenfräsen: Gibt es plattierte Schlitze? Diese erfordern einen zweiten Bohr-/Frässchritt.

- Kastellierte Löcher: Halbierte Löcher am Rand erfordern eine spezielle Fräsung und Handhabung.

- Kleine ringförmige Ringe: Wenn die Padgröße minus der Bohrergröße < 4 mil beträgt, ist eine hochpräzise Ausrichtung (Registrierung) erforderlich, was die Kosten erhöht.

- Abziehbare Maske: Wird zum Schutz von Löchern beim Wellenlöten verwendet. Dies ist ein manueller Bewerbungsprozess.

- Via-Füllung: Leitfähiges oder nichtleitendes Via-Füllung (POFV) ist deutlich teurer als einfaches Zelten mit Lötstopplack.

Selbstprüfung: Führen Sie Ihre Gerbers durch ein DFM-Tool oder einen Gerber Viewer, um diese Merkmale zu identifizieren. Wenn eine Funktion nicht kritisch ist, entfernen Sie sie.

7. Mengen- und Lieferzeitstrategien

Die Wirtschaftlichkeit der Leiterplattenherstellung wird stark von den Einrichtungskosten und Skaleneffekten bestimmt.

Die Einrichtungsgebührenfalle

Für jeden Auftrag fallen NRE-Kosten (Non-Recurring Engineering) an: CAM-Überprüfung, Filmerstellung, Schablonenerstellung und Maschineneinrichtung.

- Szenario: Die Bestellung von 5 Prototypen könnte 100 $ kosten (20 $/Board). Die Bestellung von 50 Stück kostet möglicherweise 200 US-Dollar (4 US-Dollar pro Brett).

- Strategie: Wenn Sie von der Konstruktion überzeugt sind, ist die Bestellung einer etwas größeren Pilotserie (z. B. 50 Einheiten) pro Einheit oft kostengünstiger als die Bestellung von 5, dann 10, dann 20.

Vorlaufzeit

Regel: Planen Sie im Voraus, µm „Quick Turn“-Prämien zu vermeiden. Bereich: Die Standardvorlaufzeit beträgt 5–7 Tage. Wenn Sie eine 24-Stunden- oder 48-Stunden-Bereitstellung beantragen, kann sich der Preis µm 100 % bis 200 % erhöhen. Logistik: Aufträge konsolidieren. Der Versand von 5 verschiedenen PCB-Designs in einem Paket spart deutlich internationale Frachtkosten.

8. Test- und Inspektionsprotokolle

Qualitätssicherung ist von entscheidender Bedeutung, aber eine übermäßige Spezifizierung der Testanforderungen führt zu unnötigen Kosten.

Elektrische Prüfung (E-Test)

- Flying Probe: Gut für Prototypen und kleine Stückzahlen. Keine Montagekosten, aber langsam pro Platine.

- Nagelbett (Befestigung): Hohe Einrichtungskosten ($200-$500+), aber sehr schnell pro Platine.

- Entscheidung: Bei Bestellungen unter 50 Quadratmetern oder kleinen Chargen ist Flying Probe Standard und normalerweise im Preis inbegriffen. Fordern Sie keine Vorrichtungstests für Prototypen an.

IPC-Klassenanforderungen

- IPC-Klasse 2: Standard für die meisten Industrie- und Unterhaltungselektronikgeräte.

- IPC-Klasse 3: Erforderlich für Luft- und Raumfahrt-, Medizin- und Lebenserhaltungssysteme.

- Kosten: Klasse 3 erfordert dichtere Ringringe, eine größere Beschichtungsdicke in Löchern und strengere Inspektionskriterien, was oft zu einer Kostensteigerung von 20–40 % führt.

- Überprüfen: Benötigt Ihr LED-Controller wirklich Zuverlässigkeit der Klasse 3? Wahrscheinlich nicht.

9. Fortgeschrittenes fertigungsgerechtes Design (DFM)

Die Umsetzung robuster DFM-Richtlinien ist das ultimative Kostensenkungsinstrument. Es verhindert den „Wartezustand“, bei dem technische Fragen (EQs) die Produktion verzögern und möglicherweise kostspielige Neukonstruktionen erzwingen.

Lötstopplackdämme

Regel: Halten Sie einen Lötstopplackdamm von mindestens 4 mil (0,1 mm) zwischen den Pads ein. Fehler: Wenn der Damm zu klein ist, muss der Hersteller die Maske in mehreren Schritten entlasten (ganz zwischen den Pads entfernen), was das Risiko von Lötbrücken während der Montage erhöht. Um den Damm aufrechtzuerhalten, benötigen sie möglicherweise LDI (Laser Direct Imaging) mit höherer Präzision, was mehr kostet.

Siebdruck-Einschränkungen

Regel: Halten Sie die Höhe des Siebdrucktextes ≥ 30 mil und die Linienbreite ≥ 5 mil ein. Warum es wichtig ist: Lesbarkeit. Dies erhöht zwar nicht immer direkt den Preis, ein unleserlicher Siebdruck kann jedoch zu Montagefehlern führen, die massive „versteckte“ Kosten verursachen.

10. Beschaffung und Lieferantenauswahl

Schließlich hängen die Kostentreiber für Leiterplatten und wie man sie reduzieren kann auch davon ab, wen Sie für die Herstellung Ihrer Leiterplatten auswählen.

- Prototyp-Shops: Optimiert für Geschwindigkeit und geringe Stückzahlen. Hoher Stückpreis, niedrige Einrichtungsgebühr.

- Massenproduktionshäuser: Für Volumen optimiert. Niedriger Stückpreis, höhere Einrichtungsgebühr.

- Hybridhersteller: Unternehmen wie APT PCB schließen diese Lücke und bieten nahtlose Übergänge von NPI Small Batch zur Massenproduktion.

Offshore vs. Inland

Während die inländische Fertigung Geschwindigkeit und IP-Sicherheit bietet, bleibt die Offshore-Fertigung (insbesondere Asien) der König der kostengünstigen Leiterplattenfertigung. Die dortige Integration der Arbeits- und Materiallieferkette ermöglicht Preise, die bei der Massenproduktion oft µm 30–50 % niedriger sind.

Zusammenfassende Checkliste zur Kostenreduzierung

Um sicherzustellen, dass Sie den besten Preis erhalten, gehen Sie diese Checkliste durch, bevor Sie Ihre Dateien einreichen:

- Panelisierung: Liegt die Panelauslastung bei >80 %?

- Material: Ist Standard FR4 TG140 spezifiziert?

- Ebenen: Kann ich dies auf 4 statt auf 6 Ebenen routen?

- Bohrer: Sind alle Löcher >0,2 mm? Gibt es weniger als 10 verschiedene Bohrergrößen?

- Spur/Abstand: Liegt das Design innerhalb der 5/5-Mil-Beschränkungen?

- Abschluss: Ist bleifreies HASL akzeptabel?

- Durchkontaktierungen: Habe ich blinde/vergrabene Durchkontaktierungen eliminiert?

- Toleranzen: Sind die Umrisstoleranzen auf +/- 0,2 mm gelockert?

- Test: Ist IPC Klasse 2 ausreichend?

- Volumen: Kann ich die Chargengröße erhöhen, µm die Einrichtungskosten zu amortisieren?

Durch die systematische Berücksichtigung dieser Faktoren können Sie eine erhebliche Reduzierung der PCB-Kosten erreichen, ohne Einbußen bei der Qualität oder Funktionalität Ihrer elektronischen Produkte hinnehmen zu müssen. Das Ziel besteht nicht nur darin, den günstigsten Hersteller zu finden, sondern auch darin, eine Platine zu entwerfen, deren Herstellung grundsätzlich wirtschaftlich ist. Für eine detaillierte Angebotsanalyse oder um zu besprechen, wie Sie Ihr spezifisches Design hinsichtlich der Kosten optimieren können, kontaktieren Sie unser Engineering-Team oder reichen Sie Ihre Dateien über unser Angebot-Portal ein.