Design-Review-Fragen für Leiterplatten: Kurzantwort (30 Sekunden)

Eine gründliche Überprüfung vor der Fertigung verhindert kostspielige Neuanläufe und Montageverzögerungen. Ein robuster Satz von Design-Review-Fragen für Leiterplatten konzentriert sich auf die Validierung von Konnektivität, Herstellbarkeit und physikalischen Einschränkungen.

- Integrität von Schaltplan zu Layout überprüfen: Sicherstellen, dass die Netzliste exakt übereinstimmt und alle Footprints den korrekten BOM-Komponenten entsprechen.

- Fertigungsbeschränkungen prüfen (DFM): Bestätigen, dass Leiterbahnbreiten, Abstände und Bohrdurchmesser den Fähigkeiten von APTPCB (APTPCB Leiterplattenfabrik) entsprechen.

- Hochgeschwindigkeitsanforderungen validieren: Impedanzprofile und Längenanpassung überprüfen, insbesondere für Schnittstellen wie das 100BASE-T1 Differenzialpaar-Design.

- Stromversorgungs-Integrität bewerten: Sicherstellen, dass Leistungsebenen ausreichend Kupfergewicht haben und Entkopplungskondensatoren nahe an den Stromversorgungs-Pins platziert sind.

- Mechanische Passform bestätigen: Bauteilhöhe im Vergleich zu Gehäusegrenzen prüfen und Befestigungslochpositionen verifizieren.

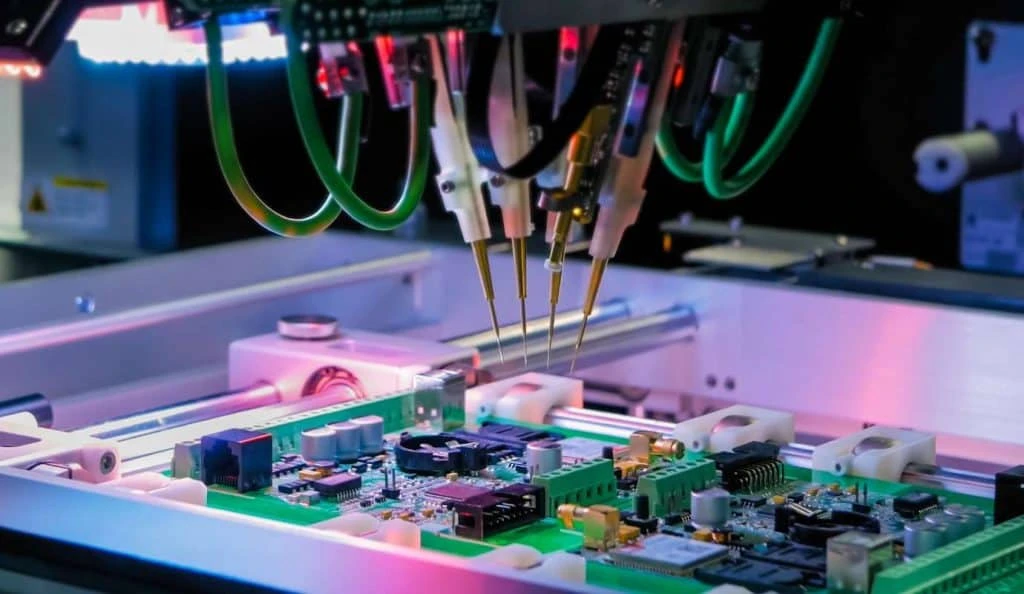

- Montage überprüfen (DFA): Ausreichenden Abstand zwischen den Komponenten für Bestückungsautomaten und Lötwerkzeuge sicherstellen.

Wann Design-Review-Fragen für Leiterplatten angewendet werden (und wann nicht)

Zu verstehen, wann eine formale Checkliste angewendet werden sollte, stellt sicher, dass technische Ressourcen effektiv genutzt werden.

Wann Design-Review-Fragen für Leiterplatten strikt anzuwenden sind:

- Neue Produkteinführung (NPI): Erstmalige Fertigungen erfordern eine umfassende Überprüfung jeder Lage und jedes Netzes.

- Hochgeschwindigkeits- oder HF-Designs: Komplexe Platinen mit 1000BASE-T1 Magnetik und Layout erfordern strenge Signalintegritätsprüfungen.

- Großserienproduktion: Kleinere Fehler in der Massenproduktion führen zu massiven Ausschusskosten; eine detaillierte Überprüfung ist zwingend erforderlich.

- Komplexe Lagenaufbauten: Designs, die HDI, Blind-/Vergrabene Vias oder Starrflex-Materialien verwenden, erfordern eine spezifische Fertigungsvalidierung.

- Sicherheitskritische Anwendungen: Automobil-, Medizin- und Luftfahrtplatinen müssen strenge Zuverlässigkeitsprüfungen bestehen.

Wann eine vollständige formale Überprüfung vereinfacht werden könnte:

- Kleinere Revisionsänderungen: Wenn sich nur eine Siebdruckbeschriftung oder ein unkritischer Widerstandswert geändert hat, kann eine vollständige Layout-Überprüfung übertrieben sein (Fokus auf die Änderungen).

- Einfache Breakout-Boards: 2-lagige Adapterplatinen mit niedriger Geschwindigkeit erfordern oft nur grundlegende Konnektivitäts- und DRC-Prüfungen.

- Steckbrett-Prototypen: Frühe Proof-of-Concept-Designs könnten Geschwindigkeit über perfektes DFM priorisieren, vorausgesetzt, sie werden von Hand bestückt.

Design-Review-Fragen: PCB-Regeln und Spezifikationen (Schlüsselparameter und Grenzwerte)

Eine strukturierte Überprüfung vergleicht das Design mit spezifischen physikalischen und elektrischen Regeln. Die folgende Tabelle listet kritische Parameter auf, die während des Überprüfungsprozesses verifiziert werden müssen.

| Regelkategorie | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Wenn ignoriert |

|---|---|---|---|---|

| Leiterbahnbreite | > 4-6 mil (Standard) | Gewährleistet Strombelastbarkeit und Herstellbarkeit. | DRC & Impedanzrechner. | Überhitzung oder offene Stromkreise während des Ätzens. |

| Leiterbahnabstand | > 4-6 mil (Standard) | Verhindert Kurzschlüsse und Übersprechen. | DRC (Design Rule Check). | Kurzschlüsse oder Signalstörungen. |

| Via-Größe | 0,2 mm - 0,3 mm (mechanische Bohrung) | Beeinflusst das Aspektverhältnis und die Zuverlässigkeit der Beschichtung. | Überprüfung der Bohrtabelle. | Bohrerbruch oder Beschichtungsfehler. |

| Ringwulst | > 4-5 mil | Stellt sicher, dass die Via-Pad beim Bohren nicht beschädigt wird. | DFM-Prüfung. | Offene Verbindungen (Ausbruch). |

| Impedanzkontrolle | ±10% des Ziels (z.B. 50Ω) | Kritisch für die Signalintegrität auf Hochgeschwindigkeitsleitungen. | Stackup-Solver / Feldsolver. | Signalreflexion und Datenkorruption. |

| Kupfer zum Rand | > 10-20 mil | Verhindert Kupferfreilegung beim Fräsen/Ritzen. | DRC / Kantenabstandsprüfung. | Kurzschlüsse zum Gehäuse oder freiliegendes Kupfer. |

| Lötstopplacksteg | > 3-4 mil | Verhindert Lötbrücken zwischen Pads. | DFM-Analyse. | Lötbrücken bei Fine-Pitch-ICs. |

| Siebdruckgröße | > 25-30 mil Höhe | Gewährleistet Lesbarkeit für Monteure. | Sichtprüfung. | Unleserlicher Text, Montagefehler. |

| Thermische Entlastung | 4 Speichen / 10-15 mil | Erleichtert das Löten auf großen Kupferflächen. | Überprüfung der Ebeneneinstellungen. | Kalte Lötstellen (Tombstoning). |

| Bohrungs-Aspektverhältnis | < 8:1 oder 10:1 | Stellt sicher, dass die Galvanisierungslösung durch das Loch fließt. | Leiterplattendicke vs. Bohrungsgröße. | Unvollständige Durchkontaktierung (offene Vias). |

| Bauteilabstand | > 10-20 mil (min) | Ermöglicht Düsenzugang für Bestückungsautomaten. | DFA (Design for Assembly) Prüfung. | Bauteile können nicht platziert oder nachbearbeitet werden. |

| Testpunkte | > 30-40 mil Pad | Erforderlich für ICT- oder Flying-Probe-Tests. | Überprüfung der Testbarkeit. | Unfähigkeit, die Platine automatisch zu testen. |

Fragen zur Designprüfung, Schritte zur PCB-Implementierung (Prozess-Checkpoints)

Ein sequenzieller Prozess stellt sicher, dass kein Aspekt des Designs übersehen wird.

Schaltplan- und Netzlistenverifizierung

- Aktion: Vergleichen Sie die Layout-Netzliste mit dem Schaltplan.

- Schlüsselparameter: 0 Fehler im Netzlistenvergleich.

- Abnahmekontrolle: Bestätigen Sie, dass alle Pins wie beabsichtigt verbunden sind und keine "nicht gerouteten Netze" verbleiben.

Mechanische Einschränkungen und Footprint-Überprüfung

- Aktion: Überlagern Sie das 3D-Modell der Leiterplatte mit der STEP-Datei des Gehäuses.

- Schlüsselparameter: Abstand > 0,5 mm (oder gemäß Spezifikation) zum Gehäuse.

- Abnahmekontrolle: Überprüfen Sie, ob die Anschlüsse mit den Aussparungen übereinstimmen und hohe Kondensatoren nicht den Deckel berühren.

Bauteilplatzierung und thermische Überprüfung

- Aktion: Überprüfen Sie die Platzierung wärmeerzeugender Bauteile relativ zu empfindlichen ICs.

- Schlüsselparameter: Sperrschichttemperatur (Tj) < Max. Nennwert.

- Abnahmekontrolle: Sicherstellen, dass die Luftstrompfade frei sind und thermische Vias unter den Power-Pads vorhanden sind.

Kritische Signalführung (Hochgeschwindigkeit/HF)

- Aktion: Überprüfung der Leitungsführung für impedanzkontrollierte Leitungen.

- Schlüsselparameter: 100BASE-T1 Differenzialpaar-Design Längenanpassung < 5 mil (oder gemäß Spezifikation).

- Abnahmekontrolle: Überprüfung kontinuierlicher Referenzebenen (keine Unterbrechungen) unter Hochgeschwindigkeitsleiterbahnen.

Überprüfung des Stromversorgungsnetzes (PDN)

- Aktion: Analyse des Spannungsabfalls und der Stromdichte auf den Stromschienen.

- Schlüsselparameter: Spannungsabfall < 3-5%.

- Abnahmekontrolle: Bestätigen, dass die Leiterbahnbreiten für den Strom ausreichend sind und Entkopplungskondensatoren nahe an den Pins platziert sind.

DFM- und DFA-Endprüfung

- Aktion: Durchführung einer herstellerspezifischen DFM-Prüfung (unter Verwendung von APTPCB-Beschränkungen).

- Schlüsselparameter: Minimale Leiterbahn-/Abstands- und Bohrungsgrößen entsprechen den "Standard"- oder "Erweiterten" Fähigkeiten.

- Abnahmekontrolle: Keine DRC-Verletzungen; Säurefallen und Splitter entfernt.

Siebdruck- und Dokumentationsprüfung

- Aktion: Überprüfung der Polaritätsmarkierungen und Referenzbezeichnungen.

- Schlüsselparameter: Text befindet sich nicht über Pads oder Vias.

- Abnahmekontrolle: Pin 1 ist für alle ICs und Steckverbinder deutlich gekennzeichnet.

Gerber- und Ausgabeerzeugung

- Aktion: Erzeugung von Gerber X2- oder ODB++-Dateien und deren Anzeige in einem Drittanbieter-Viewer.

- Schlüsselparameter: Dateiausrichtung und -format.

- Abnahmekontrolle: Lagen stimmen perfekt überein; Bohrdatei stimmt mit Bohrtabelle überein.

Fragen zur Designprüfung, Leiterplatten-Fehlerbehebung (Fehlermodi und Korrekturen)

Selbst mit einer Checkliste können Probleme übersehen werden. Hier erfahren Sie, wie Sie häufige Fehler beheben können, die während oder nach der Überprüfung festgestellt wurden.

Symptom: Hochgeschwindigkeits-Datenfehler (Paketverlust)

- Ursachen: Impedanzfehlanpassung, Stubs oder Referenzebenen-Splits.

- Prüfungen: Haben Sie den Rückweg der 1000BASE-T1 Magnetics und des Layouts überprüft? Gibt es Vias, die die Masseebene unterbrechen?

- Behebung: Neuentwurf zur Verbindung von Masseebenen oder Entfernung von Stubs.

- Vorbeugung: Verwenden Sie Simulationswerkzeuge während der Routing-Phase.

Symptom: Lötbrücken bei Fine-Pitch-ICs

- Ursachen: Unzureichender Lötstopplacksteg oder zu große Schablonenöffnung.

- Prüfungen: Ist der Lötstopplacksteg < 3 mil? Wurde die Schablonenreduzierung angewendet?

- Behebung: Schablonendesign ändern (Öffnung reduzieren); für die Leiterplatte, Abstand erhöhen, falls möglich.

- Vorbeugung: Halten Sie sich an strenge DFM-Regeln für Fine-Pitch-Bauteile.

Symptom: Platine passt nicht ins Gehäuse

- Ursachen: Versatz der Steckerplatzierung oder Verletzung der Bauteilhöhe.

- Prüfungen: Wurde eine 3D-Interferenzprüfung durchgeführt? Wurden "Keep-out"-Zonen beachtet?

- Behebung: Mechanische Modifikation des Gehäuses (falls günstiger) oder Anpassung des Leiterplattenlayouts.

- Vorbeugung: Importieren Sie mechanische STEP-Dateien vor dem Routing in das ECAD-Tool.

Symptom: Verrauschte Analogsignale

- Ursachen: Digitale Rückströme, die analoge Bereiche kreuzen (gemeinsame Masseimpedanz).

- Prüfungen: Sind analoge und digitale Massen getrennt oder ordnungsgemäß partitioniert?

- Behebung: Leiterbahnen durchtrennen und Drahtbrücke für Prototyp; Massefläche für Produktion neu gestalten.

- Vermeidung: Korrekte Flächenplanung und Rückpfadanalyse.

Symptom: Offene Vias (Intermittierende Verbindung)

- Ursachen: Zu hohes Aspektverhältnis verhindert Beschichtung; eingeschlossene Luft.

- Prüfungen: Ist das Verhältnis von Plattendicke zu Bohrdurchmesser > 10:1?

- Behebung: Größere Vias oder dünneres Plattenmaterial verwenden.

- Vermeidung: Bohrtabelle mit Herstellerfähigkeiten abgleichen.

Symptom: Tombstoning passiver Bauteile

- Ursachen: Ungleichmäßige thermische Masse auf den Pads (ein Pad auf großer Fläche, eines auf dünner Leiterbahn).

- Prüfungen: Werden thermische Entlastungen bei Flächenverbindungen verwendet?

- Behebung: Manuelle Nacharbeit; Layout ändern, um thermische Speichen hinzuzufügen.

- Vermeidung: Regeln für thermische Entlastung in der CAD-Software durchsetzen.

Wie man Design-Review-Fragen für PCBs priorisiert (Designentscheidungen und Kompromisse)

Nicht alle Design-Review-Fragen haben das gleiche Gewicht. Ihre Priorisierung hängt von der Komplexität und Anwendung der Platine ab.

1. Funktionalität vs. Herstellbarkeit Für einen Prototyp ist die Funktionalität (Konnektivität) von größter Bedeutung. Man könnte eine geringere Ausbeute oder höhere Kosten in Kauf nehmen, um ihn schnell fertigzustellen. Für die Massenproduktion werden DFM-Fragen (Ausbeute, Kosten, Testbarkeit) zur obersten Priorität.

2. Signalintegrität vs. Layoutdichte Bei Hochgeschwindigkeitsdesigns, die 100BASE-T1 Differenzialpaar-Designs umfassen, bestimmt die Signalintegrität das Layout. Sie müssen Fragen zu Impedanz und Rückpfaden gegenüber Fragen zur Minimierung der Platinengröße oder Lagenanzahl priorisieren. Wenn das Signal fehlschlägt, ist die Platine nutzlos.

3. Kosten vs. Leistung Fragen zu Lagenaufbaumaterialien (z.B. FR4 vs. Rogers) wirken sich direkt auf die Kosten aus. Wenn Ihre Design-Review-Fragen zur Leiterplatte eine marginale Signalleistung auf FR4 aufzeigen, müssen Sie entscheiden, ob die Kosten für spezialisiertes Material gerechtfertigt sind.

4. Manuelle Inspektion vs. Automatisierte Prüfungen Vertrauen Sie DRC für Abstände und Breiten, aber priorisieren Sie die manuelle Überprüfung für "Absichts"-Fragen. Ein DRC lässt eine über eine geteilte Ebene geführte Leiterbahn passieren, aber eine manuelle Überprüfung erkennt das EMI-Risiko. Konzentrieren Sie menschliche Anstrengungen auf Logik und Physik, nicht nur auf Geometrie.

Fragen zur Leiterplatten-Designprüfung FAQ (Fertigungsbeschränkungen prüfen (DFM)-Dateien)

F: Wie wirkt sich eine gründliche Designprüfung auf die Leiterplattenkosten aus? A: Sie senkt die Kosten erheblich, indem sie Neuentwicklungen verhindert. Obwohl sie im Vorfeld zusätzliche Ingenieurzeit erfordert, verhindert das Erkennen einer DFM-Verletzung (wie eine Bohrungsgröße, die ein kundenspezifisches Werkzeug erfordert) zusätzliche Herstellergebühren.

- Verhindert Ausschuss.

- Vermeidet "Advanced Technology"-Zuschläge durch Optimierung für Standard-Spezifikationen.

F: Was sind die kritischen Fragen zur Designprüfung für Hochgeschwindigkeitsschnittstellen? A: Sie müssen fragen: Wird die durchgehende Referenzebene beibehalten? Sind Differenzialpaare innerhalb der Toleranz längenangepasst?

- Überprüfen Sie insbesondere die 1000BASE-T1 Magnetics und das Layout auf Isolation und Symmetrie.

- Stellen Sie sicher, dass Via-Stubs rückgebohrt oder minimiert sind.

F: Bietet APTPCB einen DFM-Überprüfungsservice an? A: Ja, APTPCB führt bei allen Bestellungen eine DFM-Prüfung durch. Ingenieure sollten jedoch vor der Einreichung ihre eigene Überprüfung durchführen, um Wartezeiten zu minimieren.

F: Welche Dateien werden für eine ordnungsgemäße Designprüfung benötigt? A:

- Gerber-Dateien (alle Lagen).

- Bohrdateien (NC Drill).

- IPC-356 Netzliste (für den Vergleich des elektrischen Tests).

- Bestückungszeichnungen und Pick & Place-Dateien (für DFA).

F: Wie validiere ich das 100BASE-T1 Differenzialpaar-Design während der Überprüfung? A: Überprüfen Sie, ob die differentielle Impedanz 100Ω ±10% beträgt. Stellen Sie sicher, dass das Paar zusammen ohne Aufteilung um Hindernisse herum verlegt wird, und überprüfen Sie, ob die Modenkonversionsgrenzen durch die Einhaltung der Symmetrie eingehalten werden.

F: Welche Auswirkungen hat das Überspringen der Frage "Mechanische Passung"? A: Die Platine kann elektrisch perfekt, aber physisch unbrauchbar sein.

- Steckverbinder können zu weit versenkt sein.

- Befestigungslöcher stimmen möglicherweise nicht mit den Abstandshaltern überein.

- Hohe Bauteile können das Schließen des Gehäuses verhindern.

F: Was sind die Abnahmekriterien für eine Leiterplatten-Designprüfung? A:

- 0 DRC-Fehler.

- 0 nicht geroutete Netze.

- Alle DFM-Anfragen gelöst.

- Simulationsergebnisse (falls zutreffend) erfüllen die Spezifikationsmargen.

F: Wie lange dauert eine typische Designprüfung? A: Es variiert von 2 Stunden für eine einfache Mikrocontroller-Platine bis zu mehreren Tagen für ein komplexes Server-Motherboard. 10-20% der gesamten Designzeit für die Überprüfung einzuplanen, ist eine gute Faustregel.

F: Kann Software alle Fragen zur PCB-Designprüfung automatisieren? A: Nein. Software prüft Regeln (DRC), aber sie kann keine Absicht prüfen. Sie wird nicht wissen, ob Sie versehentlich die TX- und RX-Leitungen an einem UART vertauscht haben, es sei denn, Sie überprüfen die Schaltplanlogik manuell.

F: Welche Fragen sollte ich bezüglich des PCB-Tests stellen? A: Fragen Sie: Gibt es genügend Testpunkte für ICT? Gibt es einen dedizierten Massepunkt für die Sonde?

- Weitere Informationen zur Validierung der ersten Einheit finden Sie unter Erstmusterprüfung.

Glossar der PCB-Designprüfungsfragen (Schlüsselbegriffe)

| Begriff | Definition |

|---|---|

| DRC | Design Rule Check; Softwareprüfung von Abstands- und Breitenregeln. |

| DFM | Design for Manufacturability; Optimierung des Designs für das Prozessfenster der Fabrik. |

| Netlist | Eine Liste aller elektrischen Verbindungen (Netze) und Komponenten im Design. |

| Gerber | Das Standarddateiformat zur Übermittlung von PCB-Layer-Daten an die Fertigung. |

| Impedanz | Der Widerstand gegen Wechselstromfluss; entscheidend für die Signalintegrität bei hohen Geschwindigkeiten. |

| Differenzialpaar | Zwei komplementäre Signale, die zur Datenübertragung mit hoher Rauschunempfindlichkeit verwendet werden. |

| Rückweg | Der Pfad, den der Strom nimmt, um zur Quelle zurückzukehren; normalerweise auf der Masseebene. |

| Fiducial | Optische Markierungen, die von Bestückungsautomaten zur Ausrichtung der Leiterplatte verwendet werden. |

| Stackup | Die Anordnung von Kupfer- und Isolierschichten in der Leiterplatte. |

| Tombstoning | Ein Defekt, bei dem eine Komponente während des Reflow-Lötens auf einem Ende steht. |

| IPC Class | Industriestandardstufe (Klasse 2 für Standard, Klasse 3 für hohe Zuverlässigkeit). |

| BOM | Stückliste (Bill of Materials); die Liste aller zu montierenden Komponenten. |

Angebot anfordern für Design-Review-Fragen Leiterplatte (Fertigungsbeschränkungen prüfen (DFM)-Review + Preisgestaltung)

Bereit, vom Design zur Produktion überzugehen? APTPCB bietet eine umfassende DFM-Überprüfung zusammen mit Ihrem Angebot an, um sicherzustellen, dass Ihre Antworten auf die Design-Review-Fragen Leiterplatte in eine baubare Platine umgesetzt werden.

Was Sie für ein präzises Angebot und eine DFM-Prüfung senden sollten:

- Gerber-Dateien: RS-274X- oder X2-Format.

- Fertigungszeichnung: Einschließlich Lagenaufbau, Materialspezifikationen und Bohrtabelle.

- Menge & Lieferzeit: Prototypen- oder Massenproduktionsbedarf.

- Bestückungsdateien: Stückliste (BOM) und Bestückungsdaten, falls PCBA erforderlich ist.

Jetzt Angebot und DFM-Review erhalten – Wir überprüfen Ihre Dateien, um Fertigungsprobleme zu vermeiden, bevor sie auftreten.

Fazit: Design-Review-Fragen Leiterplatte nächste Schritte

Erfolgreiches Navigieren durch Design-Review-Fragen für PCBs ist das letzte Tor zwischen einem digitalen Konzept und einer physischen Realität. Durch die systematische Validierung der elektrischen Konnektivität, Fertigungsbeschränkungen und Signalintegritätsregeln – wie denen für 1000BASE-T1 Magnetics und Layout – stellen Sie ein zuverlässiges Produkt sicher. APTPCB unterstützt diesen Prozess mit fortschrittlichen Fertigungskapazitäten und strengen Qualitätskontrollen, wodurch Sie Hochleistungselektronik gleich beim ersten Mal liefern können.