Verständnis des PCB-Lagenaufbau-Designs und warum es wichtig ist

Bevor Sie über DDR-Routing, SERDES-Längenanpassung oder Via-Fan-Outs sprechen, prägt bereits eine leise Entscheidung Ihren Erfolg: Ihr PCB-Lagenaufbau. Die Reihenfolge der Lagen, die Platzierung der Ebenen und die Wahl der Dielektrika entscheiden darüber, wie einfach es ist, die Impedanz zu kontrollieren, Rückwege sauber zu halten und EMI beim ersten Mal zu bestehen.

Ein Lagenaufbau ist nicht nur „wie viele Lagen“ Sie bezahlen. Es ist die elektrische Architektur der Platine: welche Signale neben einer soliden Masse liegen, wo Stromschienen verteilt sind, wie eng Schleifen geschlossen werden können und wie sich Ihr Design verhalten wird, sobald es den Simulator verlässt und die reale Fertigungslinie erreicht.

Bei APTPCB behandeln wir das Lagenaufbau-Design als eine gemeinsame Ingenieursaufgabe, nicht als eine Last-Minute-Checkliste. Unser Team überprüft Ihre Anforderungen und schlägt PCB-Lagenaufbau-Beispiele vor, die mit realen Materialien, realen Prozessfähigkeiten und Ihren SI/PI-Zielen übereinstimmen – von einfachen 4-Lagen-Konzepten bis hin zu fortschrittlichen 64-Lagen-mehrschichtigen laminierten Strukturen.

Wichtige Überlegungen beim PCB-Lagenaufbau-Design

- Signalintegrität (SI):

Die Platzierung von Signalschichten relativ zu Referenzebenen steuert Impedanz, Reflexionen und Übersprechen. Ein gut gestalteter Lagenaufbau bietet Hochgeschwindigkeitsnetzen eine stabile, vorhersehbare Umgebung. - Power Integrity (PI): Strom- und Masseebenenpaare bilden den Kern des PDN. Ebenenabstand, Dicke und Segmentierung beeinflussen die Entkopplungsleistung, das Rail-Rauschen und das Einschwingverhalten.

- Rückwegkontrolle: Jedes Signal benötigt einen sauberen Rückweg. Stackups, die Signale nahe an intakten Masseebenen halten, reduzieren die Schleifenfläche, senken die Induktivität und minimieren EMI-Probleme.

- Materialauswahl: FR-4, hoch-Tg- und verlustarme Materialien haben jeweils unterschiedliche Dk/Df- und Verarbeitungseigenschaften. Der Lagenaufbau ist der Punkt, an dem elektrische Anforderungen auf reale Leiterplattenfertigungsprozesse treffen.

- Herstellbarkeit und Kosten: Der beste Lagenaufbau ist einer, den Sie wiederholt bauen können. Lagenanzahl, Kupfergewicht und Dielektrikumsdicke müssen innerhalb zuverlässiger Prozessfenster und eines realistischen Budgets liegen.

- Zukünftige Skalierbarkeit: Ein Lagenaufbau, der heute "gerade so" funktioniert, kann versagen, wenn Geschwindigkeiten oder Funktionalität zunehmen. Ein gutes Lagenaufbau-Design antizipiert zukünftige Schnittstellen und die Wiederverwendung über Produktvarianten hinweg.

Zuverlässige Leistung beginnt mit dem Lagenaufbau

Indem APTPCB diese Punkte frühzeitig anspricht, hilft es Ihnen, die klassische Situation zu vermeiden, in der ein Layout gut aussieht, aber SI, PI oder EMI spät im Projekt fehlschlägt. Anstatt zu raten, beginnen Sie mit validierten PCB-Lagenaufbau-Beispielen, die bereits mit Materialverfügbarkeit, Bohregeln und Qualitätszielen übereinstimmen. Dieser Ansatz verkürzt Designzyklen, reduziert die Anzahl der Board-Revisionen und bietet Ihrem Team eine stabile elektrische Grundlage, auf der aufgebaut werden kann – egal ob Sie an einem kompakten IoT-Controller oder einer mehrschichtigen Server-Backplane arbeiten.

Praktische Beispiele für PCB-Lagenaufbau von 4 bis 12 Lagen

Die meisten Entwicklungsteams entwerfen einen Lagenaufbau nicht jedes Mal von Grund auf neu. Stattdessen beginnen sie mit bewährten PCB-Lagenaufbau-Beispielen und passen diese an ihre eigenen Signale, Stromschienen und mechanischen Einschränkungen an. Eine klare Bibliothek von 4-, 6-, 8-, 10- und 12-lagigen PCB-Lagenaufbau-Beispielen spart Zeit und reduziert Risiken.

Bei APTPCB verwenden wir eine Reihe von praxiserprobten Referenz-Lagenaufbauten als Ausgangspunkte für Kundenprojekte. Dies sind keine starren Vorlagen; es sind praktische Muster, die bereits die Fertigung, Montage und den Feldeinsatz überstanden haben.

Wichtige Beispiele für PCB-Lagenaufbau (4–12 Lagen)

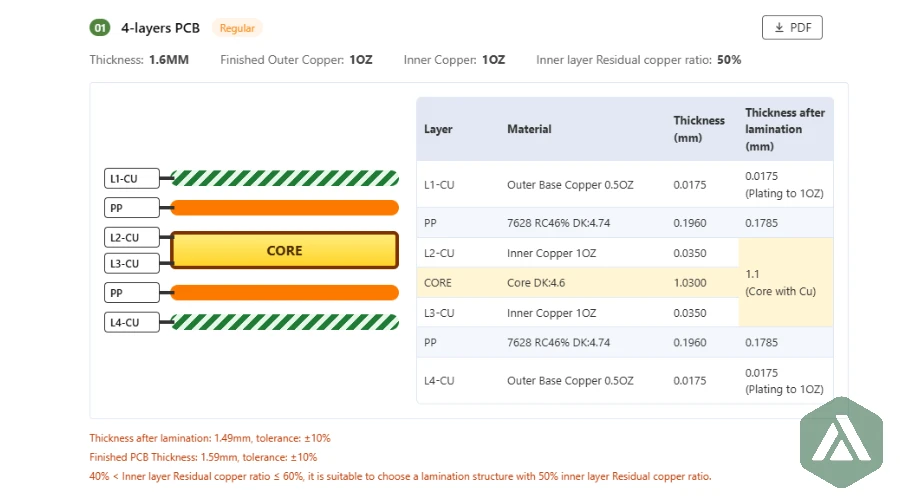

4-Lagen PCB-Lagenaufbau Beispiel – Kostengünstige Basis

Typisches 4-Lagen PCB-Lagenaufbau Beispiel:

Oberes Signal / Innere Masse / Innere Stromversorgung / Unteres Signal.

Gut für kostensensible Designs, die dennoch eine solide Massefläche und eine grundlegende kontrollierte Impedanz benötigen.

Häufig in Verbraucherprodukten und einfachen eingebetteten Systemen.6-Lagen PCB-Lagenaufbau Beispiel – Bessere Isolation und PDN

Typisches 6-Lagen PCB-Lagenaufbau Beispiel:

Oberes Signal / Innere Masse / Inneres Signal / Innere Stromversorgung / Innere Masse / Unteres Signal. Erhöht die Routing-Kapazität und verbessert die Isolation und PDN-Leistung erheblich.

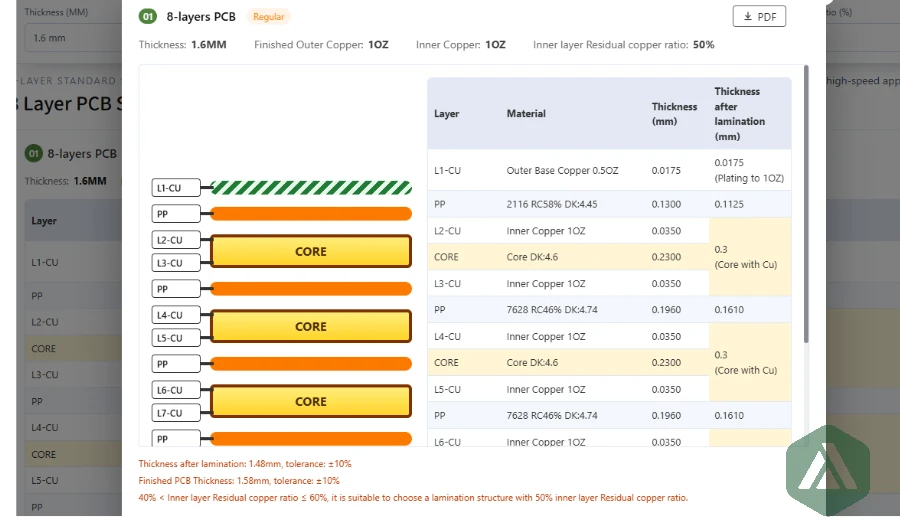

Geeignet für komplexere digitale Platinen und mittelschnelle Schnittstellen.8-Lagen-Leiterplatten-Stackup-Beispiele – Hochgeschwindigkeitsorientiert

Beliebte 8-Lagen-Leiterplatten-Stackup-Beispiele verwenden mehrere Masseebenen, zum Beispiel:

Oberes Signal / GND / Inneres Signal / PWR / GND / Inneres Signal / GND / Unteres Signal.

Hervorragend geeignet für Hochgeschwindigkeitsbusse, SERDES und dichte differentielle Paare, wo eine präzise Impedanzkontrolle und eine starke Abschirmung erforderlich sind.10-Lagen-Leiterplatten-Stackup-Beispiel – Dichtes Routing und viele Schnittstellen

Ein 10-Lagen-Leiterplatten-Stackup-Beispiel fügt typischerweise zusätzliche innere Signallagen hinzu, während mehrere Strom- und Masseebenen erhalten bleiben.

Dies ist eine solide Wahl für Hochleistungs-Computerplatinen, Netzwerkausrüstung und große FPGA-Designs mit vielen E/A-Standards.12-Lagen-Leiterplatten-Stackup-Beispiele – Mehrere Leistungsdomänen und strenge EMI

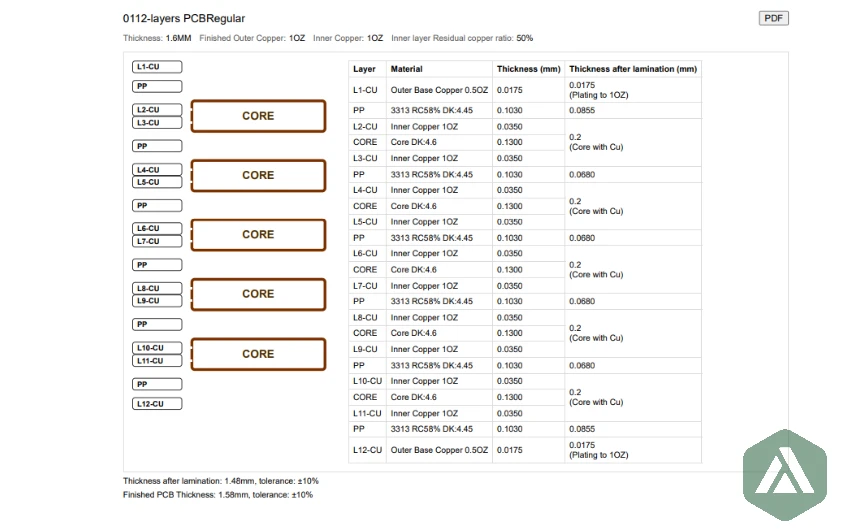

Für Platinen mit vielen Stromschienen, komplexen Bussen und strengen EMI-Grenzwerten bieten 12-Lagen-Leiterplatten-Stackup-Beispiele maximale Flexibilität.

Zusätzliche Ebenen erleichtern die Isolation rauschender Subsysteme, während zusätzliche Signallagen das Routing auch bei hoher Dichte überschaubar halten.Fortgeschrittene Leiterplatten-Stackup-Beispiele für Hochfrequenz und HF Wenn Sie sich mit sehr schnellen oder HF-Designs befassen, reichen klassische FR-4-Lagenaufbauten möglicherweise nicht aus. Wir bieten Beispiele für Hochgeschwindigkeits-Lagenaufbauten für die fortschrittliche Leiterplattenfertigung, die verlustarme Materialien, abgestimmte Dielektrika und sorgfältig gepaarte Referenzebenen einführen.

Beispiele als intelligente Ausgangspunkte nutzen

Das Ziel der Bereitstellung von PCB-Lagenaufbau-Beispielen ist nicht, ein Copy-Paste-Design zu fördern, sondern Ihnen realistische Ausgangspunkte zu geben, die bereits mit der Fertigung kompatibel sind. Sie können dann Lagenzuweisungen, Kupfergewichte oder Materialien anpassen, ohne die Grundlagen zu verletzen.

Wenn Sie Ihr Schaltbild und Ihre Vorgaben an APTPCB senden, beginnen unsere Ingenieure oft mit einem dieser Referenz-Lagenaufbauten und verfeinern ihn dann basierend auf Ihren Schnittstellen, Stromschienen und der mechanischen Kontur. Dies hält die Konversation konkret – Sie betrachten immer einen realen, baubaren Lagenaufbau, nicht nur eine theoretische Zeichnung.

Kundenspezifische PCB-Lagenaufbau-Beispiele für kontrollierte Impedanz und Hochgeschwindigkeitsdesign

Sobald Sie sich mit Multi-Gigabit-Verbindungen, HF-Abschnitten oder sehr engen Timing-Budgets befassen, reichen generische Lagenaufbauten nicht mehr aus. In diesem Stadium benötigen Sie kundenspezifische PCB-Lagenaufbau-Beispiele, die speziell für Ihre Impedanzziele, Materialien und Routing-Beschränkungen berechnet werden. Standard-FR-4 mag immer noch Teil des Bildes sein, aber jetzt denken Sie auch über Verlusttangente, Glasgewebe, Kupferrauheit und detaillierte Via-Strukturen nach. Jeder Lagenabstand und jede Dielektrikumswahl zeigt sich in Augendiagrammen, Einfügedämpfungsdiagrammen und Konformitätstests.

Schlüsselelemente von kundenspezifischen Hochgeschwindigkeits-Leiterplatten-Stackup-Beispielen

Kontrollierte Impedanzziele:

Kundenspezifische Leiterplatten-Stackup-Beispiele beginnen mit realen Impedanzzielen, wie 50 Ω Single-Ended oder 85/100 Ω Differential. Die Dielektrikumsdicke, Leiterbahnbreite und Materialien werden abgestimmt, um diese Werte mit Marge zu erreichen.Materialsysteme (FR-4, High-Tg, verlustarm):

Abhängig von Ihrer Frequenz und Kanallänge kombinieren wir Standard-FR-4 mit höherwertigen Materialien. Verlustarme Laminate, High-Tg-Kerne und Spread-Glass-Optionen werden basierend auf Ihrem Signalintegritätsbudget ausgewählt.Lagenpaarung für Signal und Referenz:

Hochgeschwindigkeits-Leiterplatten-Stackup-Beispiele halten kritische Leiterbahnen immer eng an feste Referenzebenen gekoppelt. Wir minimieren Referenzwechsel und gestalten Rückwege bewusst, insbesondere unter BGA-Fan-Outs und dichten Breakout-Bereichen.Via-Strategie und HDI-Optionen:

Durchkontaktierungen, Blind-, Buried- und Microvia-Kombinationen beeinflussen alle Impedanz und Herstellbarkeit. Kundenspezifische Stackup-Beispiele integrieren das Via-Konzept – einschließlich möglicher Rückbohrungen – sodass Routing und Signalintegrität mit den Bohrfähigkeiten übereinstimmen.Optimierung des Stromversorgungsnetzes (PDN): Abstände von Leistungs- und Masseebenen, Entkopplungsorte und Ebenenformen sind Teil der Stackup-Definition. Für rauscharme oder hochstromige Designs passen wir das PDN sowohl mit Simulationen als auch mit realen Leiterplatten-Stackup-Beispielen von ähnlichen Produkten an.

Abstimmung mit Fertigungsgrenzen:

All das oben Genannte wird durch das eingeschränkt, was zuverlässig gefertigt werden kann. Minimale Dielektrikumsdicke, Kupferverteilung und Laminierungszyklen müssen mit unseren realen Produktionslinien und Ertragszielen kompatibel sein.

Vom Konzept zur gefertigten Hochgeschwindigkeitsplatine

Wenn Sie Ihre Schnittstellenliste, Datenraten und mechanische Kontur mit APTPCB teilen, können wir ein oder mehrere kundenspezifische Leiterplatten-Stackup-Beispiele vorschlagen, die auf Ihr Produkt zugeschnitten sind. Wir verwenden Feldberechnungsdaten, Materialdatenblätter und interne Prozessfenster, um sicherzustellen, dass die Zahlen realistisch sind.

Da diese kundenspezifischen Stackups zusammen mit unserem Leiterplattenfertigungsteam erstellt werden, vermeiden Sie die klassische Lücke zwischen „simuliert“ und „baubar“. Das Ergebnis ist eine Platine, die sich im Labor wie erwartet verhält und in großem Maßstab mit stabiler Leiterplattenqualität hergestellt werden kann.

Auswahl eines Leiterplattenherstellers für komplexe Stackups bis zu 64 Lagen

Je mehr Schichten und Schnittstellen Ihr Design aufweist, desto mehr hängt der Erfolg Ihres Stackups von den tatsächlichen Fähigkeiten der Fabrik ab, die es fertigen wird. Ein grundlegendes 4-Lagen-Leiterplatten-Stackup-Design kann von vielen Lieferanten hergestellt werden – aber eine 32- oder 64-Lagen-Impedanz-kontrollierte Struktur mit HDI und gemischten dielektrischen Materialien erfordert einen Hersteller mit tiefgreifender Ingenieurserfahrung und ausgereifter Prozesskontrolle.

Sie benötigen einen Partner, der das Stackup-Design als Ingenieurdisziplin behandelt und nicht als bloßen Kostenfaktor. Das bedeutet, umsetzbares Feedback zu Machbarkeit, Risikopunkten, Materialauswahl und langfristiger Herstellbarkeit zu erhalten, bevor Sie sich zu teuren Prototypen verpflichten.

Wichtige Kriterien bei der Auswahl eines Stackup-fähigen Leiterplattenpartners

- Lagenanzahl und HDI-Erfahrung: Stellen Sie sicher, dass der Hersteller nachweislich Erfahrung mit hochlagigen und HDI-Leiterplatten hat – nicht nur mit Standard-FR-4. Fragen Sie nach deren Erfahrung mit 10-, 12-, 16-Lagen und höheren Stackup-Designs, einschließlich HDI-Aufbaustrukturen.

- Material- und Stackup-Engineering-Support: Wählen Sie ein Team, das Leiterplatten-Stackup-Designs vorschlagen und verfeinern kann – einschließlich FR-4, High-Tg, Hybridaufbauten und verlustarmen Laminaten – anstatt Ihre eingereichte Stackup-Zeichnung einfach nur zu akzeptieren oder abzulehnen.

- DFM- und NPI-Dienstleistungen: Eine frühzeitige DFM-Überprüfung (Design for Manufacturability) hilft, Risiken im Zusammenhang mit Dielektrikumdicke, Bohrbeschränkungen, Kupferbalance und Laminierungszyklen zu identifizieren. Die Plattform von APTPCB für die NPI- und Kleinserien-Leiterplattenfertigung wurde entwickelt, um Stackup-Designs zu validieren und zu optimieren, bevor sie auf die Massenproduktion skaliert werden.

- Test- und Qualitätsinfrastruktur: Impedanz-Coupons, Querschnittsanalyse, Zuverlässigkeitstests und Materialrückverfolgbarkeit sind unerlässlich bei der Validierung komplexer Stackup-Designs, insbesondere für 32-64-Lagen-Leiterplatten.

- Kommunikations- und Iterationsgeschwindigkeit: Die Stackup-Definition ist iterativ. Wählen Sie einen Partner, der schnell mit aktualisierten PCB-Stackup-Designoptionen, Materialalternativen und quantifizierten Kompromissen für Kosten, Leistung und Herstellbarkeit reagiert.

- Skalierbarkeit vom Prototyp zur Serie: Ein erfolgreiches PCB-Stackup-Design muss vom Prototyp bis zur Großserienproduktion stabil bleiben. Stellen Sie sicher, dass die Prozesse, Materialien und Laminierausrüstung der Fabrik die Konsistenz über den gesamten Produktlebenszyklus hinweg aufrechterhalten können.

PCB-Stackup-Design in produktionsreife Hardware verwandeln

APTPCB unterstützt alles von einfachen 4-Lagen-Stackup-Designs bis hin zu fortschrittlichen Aufbauten mit bis zu 64 Lagen, kontrollierter Impedanz, HDI-Microvia-Strukturen und Hybridmaterialien. Wir helfen Kunden, vom anfänglichen PCB-Stackup-Design über die NPI-Verifizierung bis zur stabilen Massenproduktion zu gelangen – ohne unerwartete Neukonstruktionen oder Materialänderungen.

Indem wir die Stackup-Entwicklung als gemeinsame Verantwortung betrachten, helfen wir Ihnen, späte SI/PI-Fehler, EMI-Probleme, Fertigungsprobleme und Ertragsverluste zu vermeiden. Das Ergebnis ist eine robuste Platinenstruktur, die:

- den elektrischen und mechanischen Anforderungen entspricht

- in bewährte Fertigungsfenster passt

- während des gesamten Produktlebenszyklus konsistent reproduziert werden kann

Wenn Sie ein neues Design planen oder ein bestehendes überprüfen möchten, senden Sie uns Ihre Lagenanzahl, Schnittstellen, Geschwindigkeitsklassen, Materialbeschränkungen und Zielperformance. Unser Ingenieurteam wird optimierte PCB-Stackup-Designoptionen vorschlagen, die Sie sofort in Ihrem Projekt verwenden können.