PCIe Gen6 Backplane-Leiterplattenprototyp: Definition, Umfang und Zielgruppe dieses Leitfadens

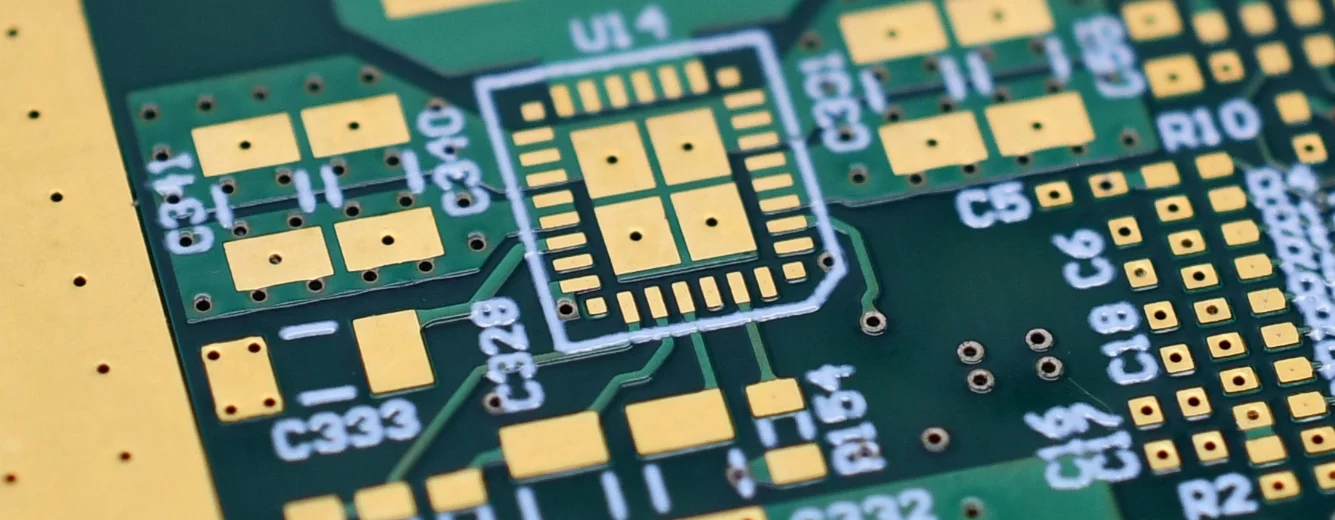

Ein PCIe Gen6 Backplane-Leiterplattenprototyp stellt die physikalische Validierung einer Hochgeschwindigkeits-Interconnect-Architektur dar, die für Datenübertragungsraten von 64 GT/s unter Verwendung von PAM4-Signalisierung ausgelegt ist. Im Gegensatz zu Standard-Leiterplatten fungieren diese Backplanes als zentrales Nervensystem für Server, Speicherarrays und Netzwerkgeräte und erfordern oft hohe Lagenzahlen (20+), Materialien mit extrem geringen Verlusten und präzises Rückbohren, um Signalstümpfe zu eliminieren. Der Übergang von der Simulation zu einem physikalischen Prototyp ist die kritischste Phase in der Hardwareentwicklung, da er bestätigt, ob die Signalintegritäts-(SI)-Modelle in einer realen Fertigungsumgebung zutreffen.

Dieser Leitfaden richtet sich an Hardware-Architekten, Signalintegritäts-Ingenieure und Einkaufsleiter, die mit der Beschaffung dieser komplexen Platinen beauftragt sind. Er geht über grundlegende Definitionen hinaus und bietet einen strukturierten Ansatz für Spezifikation, Risikominderung und Lieferantenvalidierung. Ziel ist es, Ihnen zu helfen, die engen Toleranzen zu meistern, die für die PAM4-Signalisierung erforderlich sind, und sicherzustellen, dass Ihr erster Prototypenlauf funktionale Platinen liefert, die zuverlässig getestet werden können. Bei APTPCB (APTPCB Leiterplattenfabrik) verstehen wir, dass ein Prototyp nicht nur ein Muster ist; er ist ein Beweis für technische Kompetenz. Dieses Playbook fasst Best Practices zusammen, um Ihnen zu helfen, Iterationszyklen zu minimieren und häufige Fallstricke im Zusammenhang mit der Handhabung von Hochgeschwindigkeitsmaterialien und der Mehrlagenlaminierung zu vermeiden.

Wann ein PCIe Gen6 Backplane-Leiterplattenprototyp verwendet werden sollte (und wann ein Standardansatz besser ist)

Den Umfang Ihres Projekts zu verstehen, ist der erste Schritt; zu wissen, wann man sich den Kosten und der Komplexität eines Gen6-Aufbaus widmen sollte, ist der zweite.

Setzen Sie einen PCIe Gen6 Backplane-Leiterplattenprototyp ein, wenn:

- Durchsatz ist nicht verhandelbar: Ihre Systemarchitektur erfordert 64 GT/s pro Lane, um KI/ML-Cluster, Hochfrequenz-Handelsplattformen oder Rechenzentrum-Switches der nächsten Generation zu unterstützen.

- PAM4-Signalisierung ist erforderlich: Sie wechseln von der NRZ (Non-Return-to-Zero)-Kodierung. PAM4 führt vier Spannungspegel ein, was die Rauschmarge erheblich reduziert und eine strengere Impedanzkontrolle als bei Gen5 erfordert.

- Zukunftssichere modulare Designs: Sie entwerfen ein Chassis, das für mehrere Hardware-Generationen ausgelegt ist und erfordert, dass die Backplane aktuelle Gen5-Karten unterstützt und gleichzeitig für Gen6-Upgrades bereit ist.

- Komplexe Topologie: Das Design umfasst lange Leiterbahnlängen (bis zu 20 Zoll), bei denen der Einfügungsverlust zum primären Engpass wird, was fortschrittliche Materialien und Stecker-Footprints erfordert.

Bleiben Sie bei Standard Gen4/Gen5 Backplanes, wenn:

- Kosten sind der Haupttreiber: Die für Gen6 benötigten Materialien (z.B. Megtron 7/8, Tachyon) sind deutlich teurer als Standard-FR4 oder Laminate mit mittleren Verlusten.

- Abwärtskompatibilität: Das System ist nur mit älteren Peripheriegeräten kompatibel, die keine PAM4-Signalintegrität erfordern.

- Kurze Leiterbahnlängen: Wenn der Signalpfad sehr kurz ist, können die Vorteile von Materialien mit extrem geringen Verlusten im Vergleich zu den Kosten vernachlässigbar sein.

PCIe Gen6 Backplane-Leiterplatten-Prototyp-Spezifikationen (Materialien, Lagenaufbau, Toleranzen)

Sobald Sie festgestellt haben, dass eine Gen6-Lösung erforderlich ist, müssen Sie strenge Spezifikationen festlegen, um sicherzustellen, dass der Hersteller die Anforderungen an die Signalintegrität erfüllen kann.

- Basismaterial (Laminat): Muss Materialien mit extrem geringen Verlusten verwenden. Gängige Optionen sind Panasonic Megtron 7 (oder 8), Isola Tachyon 100G oder die Rogers RO4000-Serie für Hybrid-Stacks.

- Ziel-Df (Verlustfaktor): < 0,002 @ 10 GHz.

- Ziel-Dk (Dielektrizitätskonstante): Stabil über die Frequenz (3,0 – 3,4).

- Kupferfolienrauheit: HVLP (Hyper Very Low Profile) oder VLP2 Kupfer ist zwingend erforderlich.

- Grund: Bei 32 GHz (Nyquist für 64 GT/s) ist der Skin-Effekt dominant. Raues Kupfer erhöht den Leiterverlust erheblich.

- Lagenanzahl & Dicke: Typischerweise 20 bis 40 Lagen.

- Plattendicke: Liegt oft zwischen 3,0 mm und 6,0 mm (0,120" bis 0,240").

- Aspektverhältnis: Hohe Aspektverhältnisse (bis zu 20:1 oder 25:1) für durchkontaktierte Löcher (PTH).

- Impedanzkontrolle:

- Differenzialimpedanz: 85Ω oder 100Ω (je nach Architektur).

- Toleranz: Strenger als Standard; streben Sie ±5% oder ±7% anstelle des Standard-±10% an.

- Rückbohren (kontrolliertes Tiefenbohren): Obligatorisch für alle Hochgeschwindigkeits-Via-Stubs.

- Stumpflänge: Muss < 6-8 mil (0,15mm - 0,20mm) betragen, um Resonanzprobleme zu vermeiden.

- Rückbohrdurchmesser: Typischerweise Bohrdurchmesser + 8 mil Spiel.

- Oberflächenveredelung: Immersion Silber oder ENIG (stromloses Nickel-Immersion Gold).

- Präferenz: Immersion Silber wird oft für geringere Einfügedämpfung bevorzugt, obwohl ENIG für die Haltbarkeit üblich ist.

- Via-Technologie:

- Die Verwendung von Blind- und Buried-Vias ist üblich, erhöht aber die Kosten.

- Press-Fit-Steckverbinderlöcher müssen strenge Toleranzen für die fertige Lochgröße erfüllen (typischerweise ±0,05mm).

- Glasgewebe-Stil: Spread Glass (z.B. 1067, 1078, 1086) ist erforderlich, um den Fiber Weave Effect (FWE) zu mindern, der Schiefe zwischen Differentialpaaren verursacht.

- Registrierungstoleranz: Die Schicht-zu-Schicht-Registrierung muss eng sein (±3-5 mil), um sicherzustellen, dass Rückbohrungen interne Leiterbahnen nicht durchtrennen.

- Sauberkeit: Die ionischen Kontaminationswerte müssen streng kontrolliert werden, um elektrochemische Migration (ECM) in Hochspannungs-Rechenzentrumsumgebungen zu verhindern.

PCIe Gen6 Backplane PCB Prototypenherstellungsrisiken (Grundursachen und Prävention)

Spezifikationen zu definieren ist nur die halbe Miete; zu verstehen, wo der Herstellungsprozess typischerweise versagt, ermöglicht es Ihnen, Ausfälle zu verhindern.

Signalversatz durch Fasergeflecht-Effekt

- Grundursache: Differenzialpaar-Leiterbahnen verlaufen parallel zu den Glasfaserbündeln; ein Leiter verläuft über Glas, der andere über Harz.

- Erkennung: Massives Jitter in Augendiagrammen während des Tests.

- Prävention: Spezifizieren Sie „Spread Glass“-Typen oder drehen Sie das Design auf der Leiterplatte (10-Grad-Drehung), um die Dielektrizitätskonstante auszugleichen.

Rückbohrtiefenfehler (Stumpfreste oder durchtrennte Leiterbahnen)

- Grundursache: Schwankungen in der Plattendicke oder der Z-Achsen-Genauigkeit der Bohrmaschine.

- Erkennung: TDR (Zeitbereichsreflektometrie) zeigt unerwartete Impedanzabfälle; offene Stromkreise, wenn zu tief gebohrt wird.

- Prävention: Verwenden Sie „kontrollierte Tiefenbohrung“ mit elektrischer Abtastung; stellen Sie sicher, dass der Hersteller spezifische „Stoppschichten“ oder Kupferpads hinzufügt, die die Bohrung erfassen kann.

Durchkontaktierte Löcher (PTH) Risse im Zylinder

- Grundursache: Hohes Aspektverhältnis (dicke Platte, kleines Loch) kombiniert mit thermischer Ausdehnungsfehlanpassung während des Reflow-Lötens.

- Erkennung: Intermittierende Ausfälle während des Thermozyklierens oder IST-Tests.

- Prävention: Stellen Sie sicher, dass die Kupferbeschichtungsdicke in den Löchern ausreichend ist (durchschnittlich 25 µm, mindestens 20 µm); verwenden Sie Materialien mit hohem Tg und niedrigem Z-Achsen-Wärmeausdehnungskoeffizienten (CTE).

Impedanzabweichungen aufgrund des Ätzfaktors

- Ursache: Trapezförmige Leiterbahnform nach dem Ätzen (obere Breite < untere Breite) beeinflusst die Impedanz.

- Erkennung: Querschnittsanalyse oder Coupon-Tests erfüllen die Impedanzspezifikationen nicht.

- Prävention: Der Hersteller muss eine genaue Ätzkompensation auf dem Layout durchführen; die DFM-Überprüfung muss die Anpassungen der Leiterbahnbreite bestätigen.

Pad-Kraterbildung unter Press-Fit-Steckverbindern

- Ursache: Mechanische Belastung während des Einsetzens des Steckverbinders beschädigt das Harz unter dem Kupfer-Pad.

- Erkennung: Farbstoff- und Hebeltests oder Mikroschnitte.

- Prävention: Verwenden Sie "Teardrops" auf den Pads; stellen Sie sicher, dass das Harz vollständig ausgehärtet ist; befolgen Sie die Press-Fit-Spezifikationen des Steckverbinderherstellers strikt.

Fehlausrichtung der inneren Lagen

- Ursache: Materialbewegung (Skalierung) während der Laminierung von mehr als 30 Lagen.

- Erkennung: Röntgeninspektion zeigt Fehlausrichtung; Kurzschlüsse oder Unterbrechungen in extremen Fällen.

- Prävention: Verwenden Sie Pin-Laminierungstechniken; der Hersteller muss Skalierungsfaktoren basierend auf Materialverhaltensdaten anwenden.

Wachstum von leitfähigen anodischen Filamenten (CAF)

- Ursache: Elektrochemische Migration entlang der Glasfasern zwischen den Vias.

- Erkennung: Hochspannungs-Isolationswiderstandsprüfung.

- Prävention: Verwenden Sie CAF-beständige Materialien; halten Sie einen ausreichenden Wand-zu-Wand-Abstand zwischen den Vias ein (0,8 mm - 1,0 mm Rastermaß erfordert sorgfältige Planung).

Harzmangel

- Grundursache: Dicke Kupferschichten (Leistungsebenen) verhindern, dass Harz während der Laminierung in Freiräume fließt.

- Erkennung: Sichtbare Hohlräume oder Delaminierung in Querschnitten.

- Prävention: Kupferverteilung ausgleichen; bei Bedarf Hochfluss-Prepregs verwenden.

Validierung und Abnahme des PCIe Gen6 Backplane-Leiterplattenprototyps (Tests und Abnahmekriterien)

Um sicherzustellen, dass Ihr PCIe Gen6 Backplane-Leiterplattenprototyp für die Montage und Systemintegration bereit ist, ist ein strenger Validierungsplan erforderlich.

- Impedanzprüfung (TDR):

- Ziel: Überprüfen, ob die differentielle Impedanz den 85Ω/100Ω-Zielen entspricht.

- Methode: Zeitbereichsreflektometrie an Testcoupons und tatsächlichen Leiterbahnspuren.

- Akzeptanz: Alle getesteten Leitungen innerhalb einer Toleranz von ±5% (oder vereinbarter ±7%).

- Messung der Einfügedämpfung (VNA):

- Ziel: Bestätigen, dass der Signalverlust pro Zoll das Verlustbudget für Gen6 erfüllt.

- Methode: Vektor-Netzwerkanalysator-Messung bis 32 GHz.

- Akzeptanz: Verlustkurve stimmt mit Simulation überein (z.B. < 1,0 dB/Zoll bei 16 GHz) innerhalb von 10%.

- Querschnittsanalyse (Mikroschliff):

- Ziel: Überprüfen der Lagenaufbaukonstruktion, der Beschichtungsdicke und der Bohrausrichtung.

- Methode: Zerstörende physikalische Analyse eines Coupons oder einer Ausschussplatine.

- Akzeptanz: Kupferdicke > 20µm in Löchern; keine Risse; Dielektrikumdicke stimmt mit Lagenaufbau überein.

- Backdrill-Verifizierung:

- Ziel: Sicherstellen, dass Stummel entfernt werden, ohne interne Verbindungen zu beschädigen.

- Methode: Röntgeninspektion oder Mikroschliff von rückgebohrten Vias.

- Akzeptanz: Stummellänge < 8 mil; minimaler Isolationsabstand zu internen Lagen eingehalten.

- Interconnect Stress Test (IST) oder HATS:

- Ziel: Validierung der Via-Zuverlässigkeit unter thermischer Belastung.

- Methode: Thermische Zyklen (z.B. 260°C Reflow-Simulation) gefolgt von Widerstandsüberwachung.

- Akzeptanz: Widerstandsänderung < 10% nach 6 simulierten Reflow-Zyklen.

- Press-Fit Lochtoleranzprüfung:

- Ziel: Sicherstellen, dass Steckverbinderstifte sicher passen, ohne die Platine zu beschädigen.

- Methode: Stiftlehre oder Koordinatenmessmaschine (KMM).

- Akzeptanz: Fertige Lochgröße innerhalb von ±0,05 mm der Spezifikation.

- Lötbarkeitstest:

- Ziel: Sicherstellen, dass die Oberflächenveredelung Lot ordnungsgemäß annimmt.

- Methode: IPC-J-STD-003 Benetzungsbalance-Test.

- Akzeptanz: > 95% Abdeckung; keine Entnetzung.

- Verzug- und Verdrehungsmessung:

- Ziel: Sicherstellen der Planheit der Platine für Montage und Gehäuseinstallation.

- Methode: Messung auf einer Richtplatte.

- Akzeptanz: < 0,75% (oder < 0,5% für strenge Anforderungen) über die Diagonale.

PCIe Gen6 Backplane PCB Prototypenlieferanten-Qualifizierungscheckliste (Angebotsanfrage, Audit, Rückverfolgbarkeit)

Bei der Auswahl eines Partners für einen PCIe Gen6 Backplane PCB Prototypen sind allgemeine Fähigkeiten unzureichend. Verwenden Sie diese Checkliste, um Lieferanten speziell für Hochgeschwindigkeits- und hochlagige Arbeiten zu prüfen.

Gruppe 1: Angebotsanfrage-Eingaben (Was Sie bereitstellen müssen)

- Vollständige Gerber-Dateien (RS-274X oder X2) oder ODB++.

- Detaillierte Lagenaufbauzeichnung (Angabe der Materialtypen namentlich, nicht nur "FR4").

- Bohrplan, der zwischen PTH, NPTH und Rückbohrungen unterscheidet.

- Impedanzkontrolltabelle (Lage, Leiterbahnbreite, Abstand, Referenzebene).

- Netzliste (IPC-356) zur Verifizierung des elektrischen Tests.

- Fertigungszeichnung mit Anmerkungen zu Klasse-3-Anforderungen und Toleranzen.

- Spezifikationen für Einpressverbinder (Anforderungen an die Lochgröße).

- Nutzenanforderungen (falls die Bestückung automatisiert ist).

Gruppe 2: Nachweis der Fähigkeiten (Was sie demonstrieren müssen)

- Erfahrung mit Megtron 7/8 oder Tachyon Materialien (fragen Sie nach Beispielen früherer Projekte).

- Fähigkeit, Aspektverhältnisse > 20:1 zu handhaben.

- Automatisierte Rückbohrausrüstung mit Tiefenmesstechnik.

- Laminierpressen, die Hochdruck/Vakuum für >30 Lagen verarbeiten können.

- Interne VNA/TDR-Tests bis 40 GHz.

- Laserbohrfähigkeit für Microvias (falls HDI verwendet wird).

Gruppe 3: Qualitätssystem & Rückverfolgbarkeit

- IPC-6012 Klasse 3 Qualifikation.

- UL-Zertifizierung für den vorgeschlagenen spezifischen Materiallagenaufbau.

- Automatisierte Optische Inspektion (AOI) für Innenlagen (100% Inspektion).

- Röntgenfähigkeit zur Registrierungsprüfung.

- Materialkonformitätszertifikate (CoC) vom Laminatlieferanten.

- Kalibrierungsaufzeichnungen für Impedanzprüfgeräte.

Gruppe 4: Änderungskontrolle & Lieferung

- Formaler Engineering Change Order (ECO) Prozess.

- DFM-Bericht wird vor Fertigungsbeginn bereitgestellt.

- EQ (Engineering Query) Prozess zur Behebung von Datenmehrdeutigkeiten.

- Sichere Datenverarbeitung (IP-Schutz).

- Klarer Lieferzeitplan einschließlich Materialbeschaffungszeit.

- Verpackungsstandards (vakuumversiegelt mit Trockenmittel und Feuchtigkeitsindikator).

So wählen Sie einen PCIe Gen6 Backplane PCB Prototyp (Kompromisse und Entscheidungsregeln)

Jede Designentscheidung beinhaltet einen Kompromiss. So navigieren Sie durch die widersprüchlichen Einschränkungen eines PCIe Gen6 Backplane PCB Prototyps.

- Materialkosten vs. Signalverlust:

- Regel: Wenn Ihre Leiterbahnlänge 10 Zoll überschreitet, wählen Sie Megtron 7 oder Tachyon, trotz der Kosten.

- Kompromiss: Wenn die Leiterbahnen < 5 Zoll sind, könnten Sie mit Megtron 6 oder Materialien mit mittlerem Verlust davonkommen, um 30% der Laminatkosten zu sparen, aber Sie riskieren, die SI-Margen nicht zu erfüllen.

- Lagenanzahl vs. Aspektverhältnis:

- Regel: Wenn Sie mehr Routing-Lagen benötigen, müssen Sie die Plattendicke erhöhen.

- Kompromiss: Wenn die Dicke 4 mm überschreitet, stellen Sie sicher, dass der Via-Durchmesser groß genug ist, um das Aspektverhältnis unter 20:1 zu halten. Wenn Sie Vias auf einer dicken Platine (5 mm) klein (0,2 mm) halten, wird die Zuverlässigkeit der Beschichtung fehlschlagen.

- Rückbohren vs. Sacklöcher (Blind Vias):

- Regel: Verwenden Sie Rückbohren für Standard-Steckerstifte.

- Kompromiss: Verwenden Sie Sacklöcher nur bei extremer Dichte. Sacklöcher erhöhen die Laminierungszyklen und Kosten erheblich, während das Rückbohren ein mechanischer Prozess nach der Laminierung ist, der billiger ist, aber größere Sperrzonen erfordert.

- Oberflächenveredelung: ENIG vs. Tauchsilber (Immersion Silver):

- Regel: Wenn die Einfügedämpfung die absolute Priorität hat, wählen Sie Tauchsilber.

- Kompromiss: Wenn die Platinen vor der Bestückung monatelang gelagert werden, wählen Sie ENIG für eine bessere Oxidationsbeständigkeit, wobei Sie einen leichten Verlust der Signalintegrität aufgrund der magnetischen Eigenschaften von Nickel in Kauf nehmen.

- Prototypengeschwindigkeit vs. DFM-Qualität:

- Regel: Überspringen Sie niemals die DFM-Überprüfung, um 2 Tage zu sparen.

- Kompromiss: Eine "schnelle Bearbeitung", die eine detaillierte technische Überprüfung überspringt, führt oft zu einer Ausschussplatine aufgrund übersehener Impedanz- oder Registrierungsprobleme. Planen Sie immer 2-3 Tage für EQ (Technische Fragen) ein.

PCIe Gen6 Backplane PCB Prototyp FAQ (Kosten, Lieferzeit, DFM-Dateien, Materialien, Tests)

F: Was ist der primäre Kostentreiber für einen PCIe Gen6 Backplane PCB Prototyp? A: Das Basislaminatmaterial (z.B. Megtron 7) und die Lagenanzahl sind die größten Faktoren. Hochgeschwindigkeitsmaterialien können 3-5x mehr kosten als Standard-FR4, und eine hohe Lagenanzahl erhöht den Laminierungsaufwand und das Ausbeuterisiko.

Q: Was ist die typische Lieferzeit für einen PCIe Gen6 Backplane PCB Prototypen? A: Die Standardlieferzeit beträgt 15-20 Arbeitstage. Wenn das spezifische Hochgeschwindigkeitsmaterial jedoch nicht auf Lager ist, kann die Beschaffung 2-4 Wochen zusätzlich in Anspruch nehmen; überprüfen Sie immer den Materiallagerbestand während der Angebotsphase.

Q: Welche DFM-Dateien sind für die Herstellung eines PCIe Gen6 Backplane PCB Prototypen entscheidend? A: Neben den Gerber-Dateien sind die IPC-356-Netzliste und eine detaillierte Lagenaufbau-Datei (mit angegebenen Dielektrizitätskonstanten) entscheidend. Ohne die Netzliste kann der Hersteller nicht überprüfen, ob die fertige Platine Ihrer elektrischen Logik entspricht.

Q: Kann ich Standard-FR4 für einen PCIe Gen6 Backplane PCB Prototypen verwenden, um Geld zu sparen? A: Nein. Standard-FR4 hat einen zu hohen Verlustfaktor (Df) (0,020 vs. 0,002), was die Signalintegrität von 64 GT/s PAM4-Signalen zerstören und den Prototypen für die Validierung unbrauchbar machen würde.

Q: Wie beeinflusst das Rückbohren die Kosten eines PCIe Gen6 Backplane PCB Prototypen? A: Das Rückbohren erhöht die Platinenkosten um etwa 10-15%, abhängig von der Anzahl der Löcher. Es erfordert eine separate CNC-Einrichtung und eine spezialisierte Tiefenkontrollprogrammierung.

Q: Was sind die Abnahmekriterien für die Impedanzprüfung dieser Prototypen? A: Die meisten Designs erfordern eine Toleranz von ±10 %, aber für Gen6 empfehlen wir, ±5 % oder ±7 % anzufordern. TDR-Coupons sollten auf den Leiterplattennutzen enthalten sein, um Tests ohne Beschädigung der eigentlichen Platine zu ermöglichen.

F: Muss ich "Spread Glass" (verteiltes Glasgewebe) für meinen PCIe Gen6 Backplane-Leiterplattenprototyp angeben? A: Ja. Standard-Glasgewebe erzeugt periodische Lücken, die zu Skew in Differentialpaaren führen. Die Angabe von Spread Glass (wie 1067 oder 1078) gewährleistet eine gleichmäßige dielektrische Umgebung für die Signale.

F: Welche Tests werden durchgeführt, um sicherzustellen, dass die Backplane im Feld nicht ausfällt? A: Abgesehen von elektrischen Tests wird für Prototypen ein Interconnect Stress Test (IST) empfohlen, um zu überprüfen, ob die Vias mit hohem Aspektverhältnis thermische Zyklen ohne Rissbildung im Lauf (Barrel Cracking) überstehen.

Ressourcen für PCIe Gen6 Backplane-Leiterplattenprototypen (verwandte Seiten und Tools)

Um Sie bei Ihrem Design- und Beschaffungsprozess weiter zu unterstützen, nutzen Sie diese spezifischen Ressourcen von APTPCB:

- Backplane-Leiterplattenfertigung: Ein tiefer Einblick in die spezifischen Fähigkeiten, die für großformatige Backplanes mit hoher Lagenzahl erforderlich sind.

- High-Speed-Leiterplattenfähigkeiten: Erfahren Sie mehr über die Fertigungstechniken, die zur Erhaltung der Signalintegrität für PCIe-, Ethernet- und DDR-Anwendungen eingesetzt werden.

- Panasonic Megtron Materialien: Detaillierte Spezifikationen zur Megtron-Familie, dem Industriestandard für Gen6-Anwendungen.

- Impedanzrechner: Ein Tool, das Ihnen hilft, Leiterbahnbreiten und -abstände für Ihre benötigten 85Ω- oder 100Ω-Differenzialpaare abzuschätzen.

- DFM-Richtlinien: Wesentliche Designregeln, um sicherzustellen, dass Ihre komplexe Backplane in großem Maßstab herstellbar ist.

Angebot für einen PCIe Gen6 Backplane PCB-Prototyp anfordern (DFM-Überprüfung + Preisgestaltung)

Bereit, vom Design zur Hardware überzugehen? Senden Sie Ihre Daten für eine umfassende DFM-Überprüfung und genaue Preisgestaltung. Für einen PCIe Gen6 Backplane PCB-Prototyp fügen Sie bitte Ihre Gerber-Dateien, Stackup-Details, Bohrtabelle und alle spezifischen Impedanzanforderungen bei.

Angebot und DFM-Überprüfung anfordern – Unser Ingenieurteam wird Ihren Stackup und die Materialauswahl überprüfen, um die Gen6-Konformität vor Produktionsbeginn sicherzustellen.

Fazit: Nächste Schritte für den PCIe Gen6 Backplane PCB-Prototyp

Die erfolgreiche Bereitstellung eines PCIe Gen6 Backplane PCB Prototyps erfordert mehr als nur das Senden von Dateien an eine Fertigungsstätte; es erfordert eine Partnerschaft, die sich auf Materialwissenschaft, Präzisionsbohrungen und strenge Validierung konzentriert. Durch die Einhaltung strenger Spezifikationen für verlustarme Materialien und Rückbohrungen und durch proaktives Management von Fertigungsrisiken wie Registrierung und Schräglage stellen Sie sicher, dass Ihr Prototyp genaue Daten für die Systemvalidierung liefert. APTPCB ist in der Lage, diese Komplexitäten zu bewältigen und stellt sicher, dass Ihr Übergang vom Design zur physischen Hardware nahtlos und zuverlässig ist.