Zuverlässige Signalintegrität (SI) bei 64 GT/s unter Verwendung von PAM4-Modulation erfordert die strikte Einhaltung einer Strategie für die PCIe Gen6 SI-Checkliste für die Massenproduktion. Im Gegensatz zu früheren Generationen lässt Gen6 fast keinen Spielraum für Fertigungsschwankungen. Eine geringfügige Abweichung bei der Kupferrauheit, der Dielektrikumsdicke oder der Via-Stumpflänge kann das Augendiagramm kollabieren lassen und Bitfehlerraten (BER)-Fehler verursachen.

APTPCB (APTPCB Leiterplattenfabrik) ist spezialisiert auf die Kontrolle dieser Variablen für Hochgeschwindigkeits-Digitaldesigns. Dieser Leitfaden bietet die spezifischen Parameter, Inspektionspunkte und Schritte zur Fehlerbehebung, die erforderlich sind, um ein PCIe Gen6-Design ohne Ausbeuteverluste vom Prototyp zur Großserienfertigung zu überführen.

PCIe Gen6 SI-Checkliste für die Massenproduktion: Kurzantwort (30 Sekunden)

Für Ingenieure, die sofortige Validierungskriterien benötigen, sind dies die nicht verhandelbaren Anforderungen für die Gen6-Serienproduktion.

- Materialauswahl: Es müssen Ultra-Low-Loss-Laminate (Df < 0,002 bei 32 GHz) wie Panasonic Megtron 7/8 oder Isola Tachyon 100G verwendet werden. Standard-FR4 ist nicht praktikabel.

- Kupferrauheit: HVLP (Hyper Very Low Profile) oder VLP2 Kupferfolie spezifizieren, um den Leiterverlust aufgrund des Skin-Effekts bei 32 GHz (Nyquist) zu minimieren.

- Impedanzkontrolle: Toleranz auf ±5% oder ±7% für 85Ω oder 100Ω Differentialpaare verschärfen; Standard ±10% ist oft unzureichend für PAM4-Signalisierungsspielräume.

- Via-Management: Rückbohren ist für alle durchkontaktierten Signaldurchkontaktierungen obligatorisch, um die Stumpflänge unter 6-8 mil (0,15 mm-0,20 mm) zu reduzieren.

- Fasergewebe-Effekt: Drehen Sie das Design um 10-15 Grad oder verwenden Sie Spread-Glas (z. B. 1067, 1078), um Schiefe durch die Ausrichtung des Fasergewebes zu verhindern.

- Oberflächenveredelung: Verwenden Sie Immersion Silber oder ENEPIG; vermeiden Sie HASL aufgrund ungleichmäßiger Planarität und höherer Verlustcharakteristik.

Wann die PCIe Gen6 SI-Checkliste für die Massenproduktion relevant ist (und wann nicht)

Das Verständnis, wann diese strengen Kontrollen anzuwenden sind, verhindert unnötige Kostenüberschreitungen.

Gilt für:

- KI- und Rechenzentrums-Beschleuniger: Server-Motherboards und OAM-Module, die einen Durchsatz von 64 GT/s erfordern.

- High-End-Netzwerkkarten (NICs): 400G/800G Ethernet-Adapter, die PCIe Gen6-Schnittstellen nutzen.

- NVMe-Speicher-Arrays: Enterprise-SSDs, die maximale Bandbreite liefern.

- Test- und Messgeräte: BERT-Oszilloskope und Protokollanalysatoren zur Validierung der Gen6-Konformität.

Gilt nicht für:

- PCIe Gen3/Gen4 Legacy-Geräte: Standard-FR4 und Standard-Vias sind ausreichend; Gen6-Kontrollen sind überdimensioniert.

- Peripheriegeräte mit niedriger Geschwindigkeit: USB-Controller oder Management-Schnittstellen (I2C/SPI) auf derselben Platine benötigen diese spezifischen SI-Regeln nicht.

- Kurzstrecken-Unterhaltungselektronik: Geräte, bei denen die Leiterbahnlängen < 2 Zoll betragen, könnten mit Materialien geringerer Qualität auskommen, obwohl ein Restrisiko bleibt.

- Nur Prototypenläufe: Obwohl SI wichtig ist, ist die statistische Prozesskontrolle (SPC) für die Massenproduktion noch nicht relevant.

PCIe Gen6 SI-Checkliste für die Massenproduktion: Regeln und Spezifikationen (Schlüsselparameter und Grenzwerte)

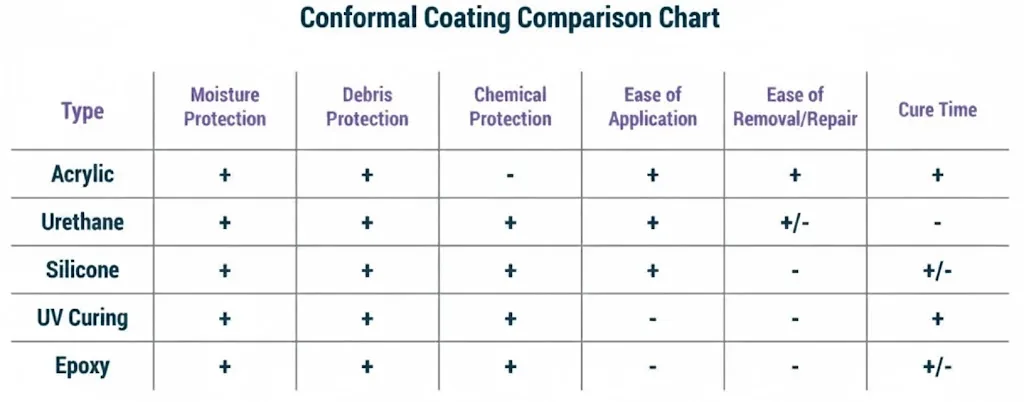

Die folgende Tabelle beschreibt die kritischen Fertigungsregeln. Diese Werte müssen explizit in den Fertigungsnotizen angegeben werden, um den Standard der PCIe Gen6 SI Checkliste für die Massenproduktion zu erfüllen.

| Regel | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Bei Missachtung |

|---|---|---|---|---|

| Differenzielle Impedanz | 85Ω oder 100Ω ±5% | PAM4-Signalisierung hat reduzierte Rauschmargen (SNR); Reflexionen müssen minimiert werden. | TDR-Coupons auf jeder Platte. | Hohe BER, Link-Training-Fehler. |

| Dielektrischer Verlust (Df) | < 0.002 @ 32 GHz | Hochfrequenzdämpfung begrenzt die Kanallänge. | IPC-TM-650 Testmethode. | Signalamplitude fällt unter die Empfängerempfindlichkeit. |

| Kupferrauheit | Rz < 2.0 µm (HVLP) | Der Skineffekt-Widerstand steigt bei 32 GHz erheblich an. | Querschnittsanalyse (SEM). | Übermäßige Einfügedämpfung. |

| Via-Stummel-Länge | < 8 mils (0.2mm) | Stummel wirken als Kerbfilter, die nahe der Nyquist-Frequenz resonieren. | Röntgeninspektion oder Mikroschliff. | Resonante Einbrüche in der Einfügedämpfung (S21). |

| Leiterbahnbreite/-abstand | Strikte Einhaltung des Feldsolvers | Erhält Kopplung und Impedanz; Fertigungs-Ätzkompensation ist entscheidend. | AOI (Automatische Optische Inspektion). | Impedanzdiskontinuität. |

| Lagenregistrierung | ± 3 mils | Fehlausrichtung beeinträchtigt die Kopplung zu Referenzebenen und Durchkontaktierungsübergängen. | Röntgenbohrverifikation. | Impedanzverschiebungen, potenzielle Kurzschlüsse. |

| Lötstopplack Dk | Niedriger Dk / Geringe Verluste | Lötstopplack über Leiterbahnen erhöht Kapazität und Verluste. | Materialdatenblatt-Zertifizierung. | Unerwarteter Impedanzabfall auf äußeren Lagen. |

| Glasgewebe-Stil | Spreizglas (1067/1078) | Verhindert periodische Belastung und Faserwebversatz. | Materialzertifizierung / Visuell. | Intra-Paar-Schiefe, Modenkonversion. |

| Plattierungsdicke | IPC Klasse 3 (min. 25µm) | Gewährleistet die Zuverlässigkeit der Durchkontaktierungen unter thermischer Belastung. | Querschnitt. | Offene Durchkontaktierungen während des Reflow-Lötens oder Betriebs. |

| Ätzfaktor | ≥ 0,8 | Trapezförmige Leiterbahnen beeinflussen Impedanzberechnungen. | Querschnitt. | Berechnete Impedanz stimmt nicht mit der gemessenen überein. |

PCIe Gen6 SI-Checkliste für die Massenproduktion: Implementierungsschritte (Prozessprüfpunkte)

Um eine PCIe Gen6 SI-Checkliste Massenproduktion erfolgreich durchzuführen, muss der Herstellungsprozess diese sequenziellen Validierungsschritte befolgen.

Lagenaufbau- & Materialprüfung

- Aktion: Bestätigen Sie die Verfügbarkeit des Laminats und die Dk/Df-Werte bei 32 GHz mit dem Lieferanten.

- Parameter: Df < 0,002.

- Prüfung: Das Konformitätszertifikat (CoC) des Lieferanten stimmt mit den angegebenen Hochgeschwindigkeits-Leiterplattenmaterialien überein.

Innenlagen-Belichtung & Ätzen

- Aktion: Ätzkompensationsfaktoren basierend auf dem Kupfergewicht anwenden, um die Ziel-Leiterbahnbreite zu erreichen.

- Parameter: Toleranz der Leiterbahnbreite ±0,5 mil.

- Überprüfung: AOI-Inspektion der Innenlagen-Signalpaare auf Verengungen oder Abstandsverletzungen.

Laminierung & Registrierung

- Aktion: Optische Ausrichtungssysteme verwenden, um Lagen zu verbinden.

- Parameter: Lagen-zu-Lagen-Registrierung < 3 mil.

- Überprüfung: Röntgenbohrziel-Verifizierung nach der Laminierung.

Bohren & Rückbohren

- Aktion: Durchgangslöcher bohren, gefolgt von tiefenkontrolliertem Rückbohren, um Stummel zu entfernen.

- Parameter: Maximaler Reststummel 8 mil.

- Überprüfung: Mikroanalyse an Testcoupons zur Überprüfung der Stummellänge.

Beschichtung & Oberflächenveredelung

- Aktion: Kupferbeschichtung auftragen, gefolgt von einer flachen Oberflächenveredelung (Tauchsilber/ENEPIG).

- Parameter: Variation der Oberflächenebenheit < 2 µm.

- Überprüfung: Sichtprüfung und Klebebandtest auf Haftung.

Impedanzprüfung (TDR)

- Aktion: Impedanz-Coupons an beiden Enden der Platte testen.

- Parameter: 85Ω ±5%.

- Überprüfung: TDR-Protokolle müssen den Status "Bestanden" für alle Differentialpaare anzeigen.

Einfügedämpfungstest (Optional/Stichprobe)

- Aktion: VNA verwenden, um S21 auf spezifischen Teststrukturen zu messen, falls erforderlich.

- Parameter: Verlust < -0,8 dB/Zoll @ 32 GHz (Beispielziel).

- Überprüfung: S-Parameter mit Simulationsmodellen vergleichen.

PCIe Gen6 SI-Checkliste für die Massenproduktion: Fehlerbehebung (Fehlermodi und Korrekturen)

Selbst mit einer robusten PCIe Gen6 SI-Checkliste können Fehler auftreten. Verwenden Sie diesen Leitfaden, um häufige Fehler in der Massenproduktion zu diagnostizieren.

Symptom: Hohe Bitfehlerrate (BER) während des Link-Trainings

- Ursache: Impedanzfehlanpassung oder übermäßiger Jitter.

- Prüfung: Überprüfen Sie die TDR-Daten auf Impedanzdiskontinuitäten > 5Ω. Prüfen Sie auf Fasergeflecht-Schiefe (Fiber Weave Skew).

- Behebung: Passen Sie die Leiterbahnbreite in CAM für den nächsten Durchlauf an; wechseln Sie zu Spread Glass.

Symptom: "Einbruch" der Einfügedämpfung (S21) um 16-20 GHz

- Ursache: Via-Stumpf-Resonanz.

- Prüfung: Überprüfen Sie die Rückbohrtiefe. Ein Stumpf, der länger als 10 mil ist, kann Resonanzen im Gen6-Frequenzband verursachen.

- Behebung: Erhöhen Sie die Einstellung der Rückbohrtiefe; stellen Sie sicher, dass der Bohrer nicht abweicht.

Symptom: Übermäßige Einfügedämpfung (Signal zu schwach)

- Ursache: Raues Kupferprofil oder falsches Dielektrikummaterial.

- Prüfung: Mikroschliff zur Überprüfung der Kupferrauheit (Rz). Bestätigen Sie, dass das richtige Laminat verwendet wurde.

- Behebung: Erzwingen Sie die Verwendung von HVLP-Kupfer; überprüfen Sie, ob der Oxidationsbehandlungsprozess das Kupfer nicht übermäßig aufraut.

Symptom: Skew zwischen P- und N-Leitungen

- Ursache: Fasergeflecht-Effekt oder ungleiche Leiterbahnlängen.

- Prüfung: Überprüfen Sie den Glasstil (1080 vs. 1067). Überprüfen Sie die Längenanpassung im Layout.

- Behebung: Drehen Sie das Design auf der Platte oder spezifizieren Sie Spread Glass-Laminate.

Symptom: Zeitweiliger Link-Abbruch

- Ursache: Zuverlässigkeit von Micro-Vias oder CAF (Conductive Anodic Filament).

- Prüfung: Thermischer Stresstest (IST). Überprüfung auf CAF-Wachstum zwischen eng beieinander liegenden Vias.

- Behebung: Vergrößerung des Via-zu-Via-Abstands; Verbesserung des Harzgehalts im Prepreg.

Symptom: Impedanzabfall im Stecker-Footprint

- Ursache: Übermäßige Kapazität an den Pads.

- Prüfung: TDR speziell im Bereich des Steckeranschlusses.

- Behebung: Referenzebenen unter den Stecker-Pads (Anti-Pads) ausschneiden, um die induktive Überhöhung zu erhöhen.

PCIe Gen6 SI-Checkliste für die Massenproduktion: Designentscheidungen und Kompromisse

Die Implementierung eines PCIe Gen6 SI-Checklisten-Massenproduktionsplans erfordert ein Gleichgewicht zwischen Leistung, Kosten und Herstellbarkeit.

Material vs. Kosten Für Gen6 ist Standard-FR4 veraltet. Die Wahl liegt zwischen "Low Loss" (z. B. Megtron 6) und "Ultra-Low Loss" (z. B. Megtron 7/8).

- Entscheidung: Wenn die Leiterbahnlänge kurz ist (< 4 Zoll), könnte Megtron 6 ausreichen. Für längere Kanäle (> 10 Zoll) müssen Sie Megtron 7 oder ein gleichwertiges Material verwenden, um das Verlustbudget einzuhalten.

Lagenanzahl vs. Übersprechen Eine höhere Lagenanzahl ermöglicht eine bessere Isolation (Masse-Signal-Masse), erhöht jedoch die Kosten und die Laminierungszyklen.

- Entscheidung: Priorisieren Sie für Gen6 die Stripline-Verlegung (innere Lagen), um elektromagnetische Felder einzudämmen. Vermeiden Sie Microstrips (äußere Lagen) für lange Strecken aufgrund von Strahlung und FEXT (Far-End Crosstalk).

Backdrilling vs. Blind-/Buried Vias Backdrilling ist günstiger als sequentielle Lamination (HDI), hinterlässt aber einen kleinen Stummel.

- Entscheidung: Verwenden Sie Rückbohrungen für Standardsteckverbinder. Verwenden Sie HDI (Blind-/Vergrabene Vias) nur, wenn die BGA-Dichte dies erzwingt, da dies die Massenproduktion von Leiterplatten erheblich verteuert.

PCIe Gen6 SI-Checkliste für die Massenproduktion – FAQ (Kosten, Lieferzeit, häufige Mängel, Abnahmekriterien, DFM-Dateien)

1. Wie stark erhöht die Massenproduktion gemäß der PCIe Gen6 SI-Checkliste die Leiterplattenkosten? Der Übergang von Gen4 (FR4-ähnlich) zu Gen6 (Megtron 7/8) erhöht die Kosten für die Rohplatine typischerweise um das 2,5- bis 4-fache, aufgrund teurer Rohmaterialien und zusätzlicher Prozessschritte wie Rückbohrungen.

2. Wie ist die Lieferzeit für Gen6-fähige Laminate? Materialien mit extrem geringem Verlust haben oft Lieferzeiten von 4-8 Wochen. APTPCB empfiehlt Lagerhaltungsvereinbarungen für die wiederkehrende Massenproduktion, um Verzögerungen zu mindern.

3. Was sind die Abnahmekriterien für die Gen6-Impedanz? Die Standardakzeptanz beträgt ±10 %, aber Gen6 erfordert oft ±5 % oder ±7 %. TDR-Coupons müssen diese strengere Grenze bestehen.

4. Benötige ich eine 100%ige TDR-Prüfung für die Massenproduktion? Ja. Für Gen6 ist statistische Stichprobenprüfung riskant. Wir empfehlen eine 100%ige TDR-Prüfung aller Hochgeschwindigkeits-Differenzpaare.

5. Welche DFM-Dateien werden für ein Gen6-Angebot benötigt? Senden Sie Gerber X2- oder ODB++-Dateien, eine detaillierte Leiterplatten-Stack-up-Zeichnung mit Angabe der Materialtypen (z. B. "Megtron 7") und eine IPC-Netzliste für den elektrischen Testvergleich.

6. Kann ich HASL-Oberflächen für PCIe Gen6 verwenden? Nein. HASL ist zu ungleichmäßig für Fine-Pitch-Komponenten und führt zu Verlusten. Verwenden Sie ENIG, ENEPIG oder Immersion Silver.

7. Wie beeinflusst die Kupferrauheit die Gen6 SI? Bei 32 GHz fließt der Strom in der äußeren Haut des Kupfers. Raues Kupfer verlängert den Signalweg, was den ohmschen Verlust erheblich erhöht. HVLP-Kupfer ist zwingend erforderlich.

8. Was ist die maximal zulässige Via-Stummel-Länge? Idealerweise null, aber praktisch < 10 mil (0,25 mm). Stummel > 15 mil können fatale Resonanzeinbrüche im Gen6-Frequenzband verursachen.

9. Ist „Spread Glass“ zwingend erforderlich? Es wird dringend empfohlen, Fasergeflecht-Schiefe zu vermeiden. Wenn Spread Glass nicht verfügbar ist, muss das Layout auf dem Panel gedreht werden, was Material verschwendet.

10. Wie überprüfe ich die Fähigkeiten des Herstellers? Fordern Sie einen „Signal Integrity Report“ von früheren Fertigungen an oder fragen Sie nach TDR-Korrelationsdaten. Prüfen Sie, ob sie über interne VNA-Testmöglichkeiten verfügen.

11. Was ist der Unterschied zwischen der PCIe Gen6 SI-Checkliste für Bestückung und Fertigung? Die Fertigung konzentriert sich auf die Leiterplatte (Impedanz, Materialien). Die Bestückung konzentriert sich auf die Qualität der Lötstellen, den korrekten Sitz der Steckverbinder und die Sicherstellung, dass Flussmittelrückstände die Oberflächenimpedanz nicht beeinflussen.

12. Warum ist der „Ätzfaktor“ in der Checkliste kritisch? Leiterbahnen sind trapezförmig, nicht rechteckig. Wenn der Hersteller für die Impedanzberechnung ein Rechteck annimmt, aber ein Trapez ätzt, ist die tatsächliche Impedanz höher als berechnet.

13. Beeinflusst die Lötstopplackfarbe die SI? Ja. Einige Pigmente (wie Schwarz) können verlustreicher oder leitfähiger sein. Grün oder Blau sind Standard; überprüfen Sie den Dk/Df der verwendeten Lötstopplacktinte.

14. Was sind die häufigsten Mängel im Design der PCIe Gen6 SI-Checkliste? Die häufigsten sind: Ignorieren von Via-Stubs, Verwendung von Standard-Kupferfolie und Nichtberücksichtigung der Dk-Änderung der harzreichen Bereiche zwischen Differentialpaaren.

Ressourcen zur PCIe Gen6 SI-Checkliste für die Massenproduktion (verwandte Seiten und Tools)

- Materialdaten: Megtron PCB-Materialien

- Herstellungsprozess: Hochgeschwindigkeits-Leiterplattenfähigkeiten

- Designrichtlinien: DFM-Richtlinien

PCIe Gen6 SI-Checkliste: Glossar (Schlüsselbegriffe)

| Begriff | Definition | Relevanz für Gen6 |

|---|---|---|

| PAM4 | Pulsamplitudenmodulation 4-stufig. | Kodiert 2 Bits pro Symbol; erfordert höheres SNR als NRZ. |

| Nyquist-Frequenz | Die Hälfte der Datenrate (32 GHz für Gen6). | Die Frequenz, bei der der fundamentale Signalverlust gemessen wird. |

| Skin-Effekt | Tendenz von Wechselstrom, nahe der Oberfläche zu fließen. | Macht die Kupferrauheit zu einem kritischen Verlustfaktor. |

| HVLP | Hyper Very Low Profile Kupfer. | Glatte Kupferfolie zur Minimierung des Skin-Effekt-Verlusts. |

| Backdrilling | Ausbohren des ungenutzten Teils einer plattierten Durchkontaktierung. | Entfernt Stubs, um Signalreflexionen/Resonanzen zu verhindern. |

| TDR | Zeitbereichsreflektometrie (Time Domain Reflectometry). | Methode zur Messung von Impedanzprofilen entlang einer Leiterbahn. |

| VNA | Vektor-Netzwerkanalysator (Vector Network Analyzer). | Instrument zur Messung von S-Parametern (Einfügedämpfung/Rückflussdämpfung). |

| Einfügedämpfung (S21) | Signalverlust, wenn es sich entlang der Leitung ausbreitet. | Die primäre Budgetbeschränkung für Gen6-Kanäle. |

| Rückflussdämpfung (S11) | Signalenergie, die zur Quelle zurückreflektiert wird. | Zeigt die Qualität der Impedanzfehlanpassung an. |

| Skew | Zeitverzögerungsdifferenz zwischen P- und N-Signalen. | Zerstört die Augenöffnung des Differenzsignals. |

| Dk (Dielektrizitätskonstante) | Maß für die Fähigkeit eines Materials, Energie zu speichern. | Bestimmt die Ausbreitungsgeschwindigkeit und Impedanz. |

| Df (Verlustfaktor) | Maß für die als Wärme im Material verlorene Energie. | Bestimmt die Signaldämpfung (Verlust). |

Angebot für PCIe Gen6 SI-Checkliste in der Massenproduktion (DFM-Überprüfung + Preisgestaltung)

APTPCB bietet eine detaillierte DFM-Analyse, um sicherzustellen, dass Ihr Hochgeschwindigkeits-Stackup und Ihre Geometrie die Anforderungen für die Massenproduktion erfüllen.

Um ein genaues Angebot und eine SI-Überprüfung zu erhalten, stellen Sie bitte Folgendes bereit:

- Gerber X2- oder ODB++-Dateien.

- Fertigungszeichnung: Muss Material (z.B. "Megtron 7 oder gleichwertig"), Impedanztabelle und Backdrill-Schichten angeben.

- Lagenaufbau-Diagramm: Lagenanzahl, Kupfergewicht und Dielektrikumsdicke.

- Volumen: Prototypenmenge vs. geschätzter Jahresverbrauch (EAU).

Fazit (nächste Schritte)

Eine erfolgreiche Skalierung auf die PCIe Gen6 SI-Checklisten-Massenproduktion erfordert einen Übergang von der Standard-Leiterplattenfertigung zu einer präzisionsgesteuerten Fertigung. Durch die Durchsetzung strenger Kontrollen bei Materialien, Kupferrauheit und Via-Geometrie können Sie die Zuverlässigkeit der 64 GT/s-Leistung gewährleisten. APTPCB ist bereit, Ihren Übergang mit fortschrittlichen technischen Fähigkeiten und strengen Qualitätskontrollen zu unterstützen.