Definition, scope, and who this guide is for

Redundant PSU Backplane Design (Design von Backplanes für redundante Netzteile) bezieht sich auf die Konstruktion und Herstellung der Leiterplatte (PCB), die als zentraler Stromverteilungsknotenpunkt in hochverfügbaren Systemen dient. Im Gegensatz zu Standard-Stromversorgungsplatinen verbinden diese Backplanes mehrere Netzteile (PSUs) – typischerweise in einer N+1- oder N+N-Konfiguration – mit der Systemlast. Sie müssen hohe Stromdichten bewältigen, Hot-Swapping (den Austausch eines Netzteils bei laufendem System) ermöglichen und kritische Signale für das Power-Management (PMBus) fehlerfrei verwalten. Die Backplane ist oft ein Single Point of Failure; wenn sie ausfällt, wird die Redundanz der Netzteile irrelevant.

Dieser Leitfaden richtet sich an Hardware-Ingenieure, Systemarchitekten und Beschaffungsleiter, die für die Beschaffung oder Konstruktion dieser kritischen Komponenten verantwortlich sind. Er geht über die grundlegende PCB-Layout-Theorie hinaus und befasst sich mit den praktischen Realitäten der Fertigung, Materialauswahl und Risikominderung. Sie finden umsetzbare Spezifikationen für Ihre Fertigungszeichnungen, eine Aufschlüsselung der Fertigungsrisiken, die spezifisch für dickes Kupfer und dicke Platinen sind, sowie eine Validierungsstrategie, um sicherzustellen, dass Ihr Redundant PSU backplane design jahrelangem 24/7-Betrieb in Rechenzentren oder Industrieumgebungen standhält.

Bei APTPCB (APTPCB PCB Factory) sehen wir viele Designs scheitern, nicht wegen elektrischer Logikfehler, sondern wegen physikalischer Fertigungseinschränkungen wie Kupferätztoleranzen, thermischer Delamination oder Steckerausrichtungsfehlern. Dieser Leitfaden schlägt die Brücke zwischen Ihrer CAD-Datei und der Fabrikhalle und stellt sicher, dass Ihre Anforderungen klar, herstellbar und verifizierbar sind.

When to use Redundant Power Supply Unit (PSU) backplane design (and when a standard approach is better)

Die Entscheidung für die Implementierung eines vollständig maßgeschneiderten Redundant PSU backplane design ist eine bedeutende Investition in Entwicklungszeit und Herstellungskosten. Daher ist es wichtig, vor dem Fortfahren zu bestätigen, dass Ihre Anwendung diese Komplexität wirklich erfordert.

Verwenden Sie ein benutzerdefiniertes Redundant PSU Backplane Design, wenn:

- Uptime is Non-Negotiable: Ihr System versorgt Server, Speicher-Arrays, medizinische Geräte oder Telekommunikationsinfrastruktur, bei denen Ausfallzeiten zu erheblichen finanziellen Verlusten oder Sicherheitsrisiken führen.

- High Current Requirements: Die Gesamtsystemlast überschreitet 50 A–100 A, was dicke Kupferschichten (3 oz bis 6 oz) oder eingebettete Stromschienen (Busbars) erfordert, die Standard-Stromverteilerplatinen von der Stange nicht bewältigen können.

- Hot-Swap Capability is Required: Sie benötigen eine präzise mechanische Ausrichtung für Blind-Mate-Steckverbinder, damit Techniker ausgefallene PSUs austauschen können, ohne das System herunterzufahren.

- Custom Form Factor: Die Stromverteilung muss in eine bestimmte Gehäusegeometrie passen, in die Standard-ATX- oder OCP-Stromverteilerplatinen (Open Compute Project) nicht passen.

- Signal Integration: Sie müssen Niederspannungs-Managementsignale (I2C, PMBus) neben Hochleistungsschienen mit strengen Anforderungen an die Störfestigkeit routen.

Bleiben Sie bei einem Standard- oder Kabelbaum-Ansatz, wenn:

- Cost is the Primary Driver: Für Unterhaltungselektronik oder nicht-kritische Desktop-Workstations ist ein Standard-Kabelbaum für ein einzelnes Netzteil deutlich billiger.

- Low Power Density: Wenn das System weniger als 20 A zieht, sind Standardkabelbäume oder einfache 1-oz-Kupfer-PCBs ausreichend und einfacher zu beschaffen.

- No Hot-Swap Needed: Wenn das System für die Wartung heruntergefahren werden kann, sind die komplexen mechanischen Toleranzen einer Backplane unnötig.

Redundant Power Supply Unit (PSU) backplane design specifications (materials, stackup, tolerances)

Die frühzeitige Definition der richtigen Spezifikationen verhindert später kostspielige technische Änderungsaufträge (ECOs). Ein robustes Redundant PSU backplane design beruht auf Materialien, die hohen thermischen Belastungen und mechanischen Lasten standhalten können.

Wichtige Spezifikationen zur Definition:

- Base Material (Laminate):

- Spezifizieren Sie High Tg FR-4 (Tg ≥ 170 °C) oder gleichwertig. Power-Backplanes erzeugen erhebliche Wärme; Standard-Tg-135°C-Materialien können im Laufe der Zeit delaminieren.

- Ziehen Sie CTI (Comparative Tracking Index) ≥ 600V (PLC 0) in Betracht, wenn Hochspannungsschienen (z. B. 48V oder 400V DC) vorhanden sind, um Kriechstrombildung zwischen den Leiterbahnen zu verhindern.

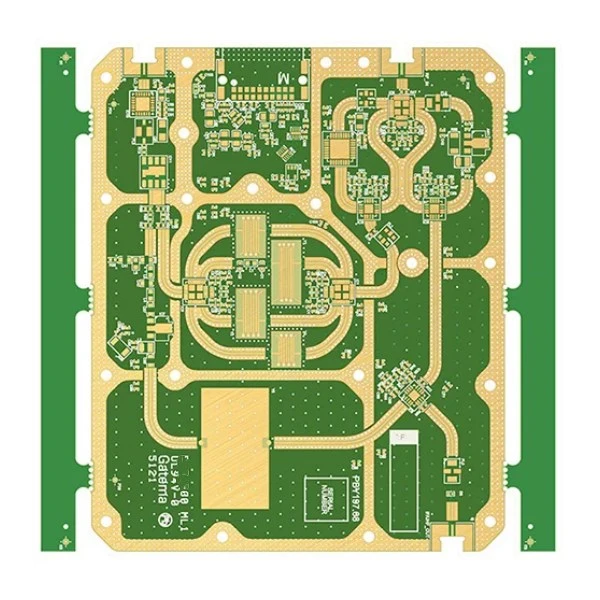

- Copper Weight:

- Definieren Sie das Kupfergewicht der inneren und äußeren Lagen explizit (z. B. 3 oz, 4 oz oder 6 oz).

- Target: Für Ströme > 50 A überprüfen Sie die Berechnungen der Leiterbahnbreite anhand der IPC-2152-Standards und nicht nur anhand einfacher IPC-2221-Formeln.

- PCB Thickness:

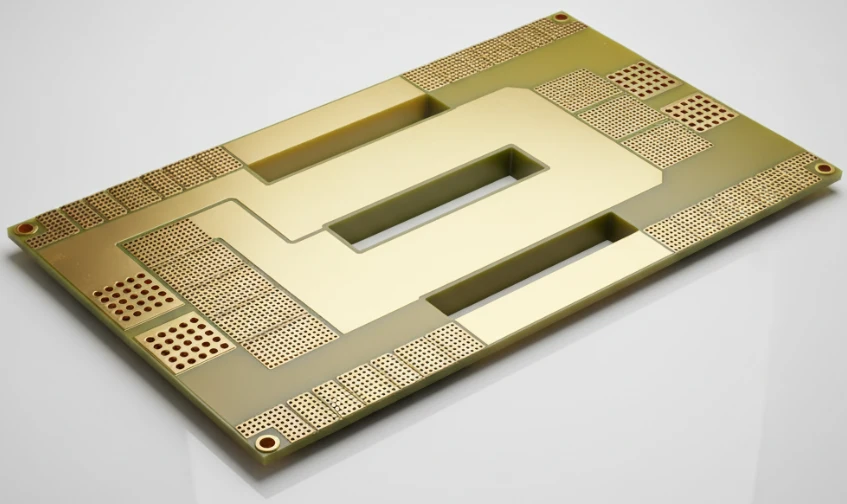

- Backplanes sind oft dicker als Standardplatinen (2,0 mm bis 6,0 mm), um mechanische Steifigkeit für schwere Steckverbinder zu gewährleisten.

- Tolerance: Spezifizieren Sie ±10 % Dickentoleranz. Für Einpresssteckverbinder (Press-fit) können engere Toleranzen (±5 %) erforderlich sein.

- Layer Count & Stackup:

- Typischer Bereich: 6 bis 14 Lagen.

- Sorgen Sie für einen symmetrischen Lagenaufbau, um ein Verziehen (Wölbung und Verwindung) zu verhindern, was für die Ausrichtung der Steckverbinder von entscheidender Bedeutung ist.

- Weisen Sie Strom und Masse spezifische Schichten zu, um die Kapazität zu maximieren und die Induktivität zu minimieren.

- Surface Finish:

- Recommended: ENIG (Electroless Nickel Immersion Gold) oder Hartgold für Randstecker/Kontaktpads.

- Vermeiden Sie HASL für Fine-Pitch-Steckverbinder oder Einpresslöcher aufgrund der ungleichmäßigen Oberflächenplanarität.

- Press-Fit Hole Tolerances:

- Wenn Sie Einpresssteckverbinder verwenden (üblich bei Backplanes), müssen Sie die Toleranzen für die fertige Lochgröße strikt angeben (oft ±0,05 mm).

- Spezifizieren Sie die Bohrergröße und die Beschichtungsdicke (normalerweise min. 25 µm Kupfer in der Hülse), um eine gasdichte Verbindung zu gewährleisten.

- Soldermask:

- Verwenden Sie hochtemperaturfesten Lötstopplack, der für mehrere Reflow-Zyklen oder Wellenlöten geeignet ist.

- Farbe: Mattgrün oder Schwarz (Matt ist besser für die automatische optische Inspektion).

- Silkscreen & Marking:

- Beschriften Sie die PSU-Steckplätze (PSU1, PSU2) und Spannungsschienen (+12V, +5V, GND) deutlich.

- Fügen Sie gegebenenfalls Hochspannungs-Warnsymbole auf dem Siebdruck ein.

- Mechanical Drills:

- Spezifizieren Sie nicht durchkontaktierte Löcher (NPTH) für Führungsstifte mit engen Toleranzen (+0,05 mm/-0,00 mm), um sicherzustellen, dass die PSUs beim Einsetzen korrekt ausgerichtet werden.

- Heavy Copper Etching:

- Berücksichtigen Sie die Regeln für minimale Leiterbahnbreite/-abstände für dickes Kupfer. Für 3-oz-Kupfer kann der Mindestabstand je nach Lieferant 8-10 mil (0,2 mm-0,25 mm) betragen.

Redundant Power Supply Unit (PSU) backplane design manufacturing risks (root causes and prevention)

Die Herstellung eines Redundant PSU backplane design birgt Risiken, die bei Standard-Low-Power-PCBs nicht vorhanden sind. Das Verständnis dieser Grundursachen hilft Ihnen, Lieferanten effektiv zu auditieren.

1. Inner Layer Misregistration

- Risk: Hohe Lagenanzahl und dickes Kupfer können dazu führen, dass sich Lagen während der Laminierung verschieben.

- Root Cause: Materialbewegung während des Hochdruck-Presszyklus.

- Prevention: Verwenden Sie Pin-Laminierungstechniken und fügen Sie spezifische Ausrichtungsziele (Coupons) in den Rand des Nutzens ein.

2. Inufficient Resin Fill (Measling/Voids)

- Risk: Hohlräume in der Isolierung zwischen dicken Kupferbahnen führen zu Kurzschlüssen oder dielektrischem Durchschlag.

- Root Cause: Standard-Prepreg-Folien enthalten möglicherweise nicht genügend Harz, um die tiefen Lücken zwischen dicken Kupferbahnen (z. B. 4-oz-Kupfer) zu füllen.

- Prevention: Spezifizieren Sie "High Resin Content" (harzreiches) Prepreg oder verwenden Sie mehrere Prepreg-Lagen, um eine vollständige Einkapselung von dicken Kupferstrukturen zu gewährleisten.

3. Plated Through Hole (PTH) Cracking

- Risk: Hülsenrisse trennen Stromversorgungsebenen oder Signale.

- Root Cause: Z-Achsen-Ausdehnung der dicken PCB während des Lötens belastet die Kupferhülse.

- Prevention: Stellen Sie sicher, dass die Beschichtungsdicke der IPC-Klasse 3 entspricht (durchschnittlich 25 µm). Verwenden Sie Materialien mit hoher Tg / niedrigem CTE (Wärmeausdehnungskoeffizient).

4. Press-Fit Connector Damage

- Risk: PCB-Risse oder beschädigte Steckerstifte bei der Montage.

- Root Cause: Falsche Lochgröße oder unzureichende PCB-Steifigkeit.

- Prevention: Strenge Kontrolle der fertigen Lochgröße (Finished Hole Size, FHS) und Verwendung einer starren Stützvorrichtung (Support Fixture) während des Einpressvorgangs.

5. Thermal Management Failure

- Risk: Lokalisierte Hotspots lassen die Platine durchbrennen.

- Root Cause: Schlechter Wärmepfad von den inneren Lagen zur Oberfläche.

- Prevention: Verwenden Sie thermische Via-Arrays und ziehen Sie die Metal Core PCB Technologie oder Embedded-Coin-Technologie in Betracht, wenn die Luftkühlung nicht ausreicht.

6. Heavy Copper Undercut

- Risk: Reduzierte Leiterbahnbreite erhöht Widerstand und Wärme.

- Root Cause: Ätzchemikalien fressen sich seitlich unter den Resist, während sie durch dickes Kupfer nach unten ätzen.

- Prevention: Wenden Sie in der CAM-Phase Ätzkompensationsfaktoren an (Leiterbahnen etwas breiter entwerfen) und überprüfen Sie die endgültige Leiterbahnbreite mit einer Querschnittsanalyse.

7. Bow and Twist

- Risk: Die Backplane ist nicht flach, was verhindert, dass die PSUs reibungslos hineingleiten.

- Root Cause: Asymmetrische Kupferverteilung (z. B. hat Schicht 1 90 % Kupfer, Schicht 2 10 %).

- Prevention: Gleichen Sie die Kupferabdeckung auf allen Schichten aus. Verwenden Sie Kupferflächen (Thieving) in leeren Bereichen.

8. CAF (Conductive Anodic Filament) Growth

- Risk: Interne Kurzschlüsse entwickeln sich über Monate des Betriebs.

- Root Cause: Elektrochemische Migration entlang von Glasfasern unter hoher Spannung und Feuchtigkeit.

- Prevention: Spezifizieren Sie "CAF-resistente" Materialien und halten Sie einen ausreichenden Abstand zwischen Hochspannungsnetzen ein.

Redundant Power Supply Unit (PSU) backplane design validation and acceptance (tests and pass criteria)

Die Validierung stellt sicher, dass das gefertigte Redundant PSU backplane design die theoretischen Leistungsgrenzen erfüllt. Verlassen Sie sich nicht nur auf die visuelle Inspektion.

1. Electrical Continuity & Isolation (100% Test)

- Objective: Stellen Sie sicher, dass keine Kurzschlüsse oder Unterbrechungen vorliegen.

- Method: Flying-Probe- oder Nadelbett-Tester.

- Criteria: 100 % bestanden. Isolationswiderstand > 100 MΩ bei 250V/500V.

2. Hi-Pot Testing (High Potential)

- Objective: Überprüfen der Spannungsfestigkeit zwischen Stromschienen und Gehäusemasse.

- Method: Anlegen von Hochspannung (z. B. 1500 V DC) für 60 Sekunden.

- Criteria: Leckstrom < 1 mA (oder nach Spezifikation); kein Durchschlag oder Lichtbogenbildung.

3. Microsection Analysis (Coupons)

- Objective: Überprüfen des internen Lagenaufbaus und der Beschichtungsqualität.

- Method: Querschnitt eines Testcoupons aus dem Produktionsnutzen.

- Criteria: Kupferdicke entspricht der Spezifikation (z. B. 3 oz ±10 %), Lochwandbeschichtung >25 µm, kein Harzrückgang oder Delamination.

4. Thermal Stress Test (Solder Float)

- Objective: Simulation des thermischen Schocks beim Löten.

- Method: Schwimmen der Probe im Lötbad (288 °C) für 10 Sekunden (IPC-TM-650).

- Criteria: Keine Blasenbildung, Delamination oder angehobene Pads.

5. Impedance Testing (TDR)

- Objective: Überprüfen der Signalintegrität für PMBus/Kommunikationsleitungen.

- Method: Time Domain Reflectometry an Testcoupons.

- Criteria: Gemessene Impedanz innerhalb von ±10 % des Designziels (z. B. 100 Ω differenziell).

6. Mechanical Fit Check (First Article)

- Objective: Sicherstellen, dass PSUs und Steckverbinder perfekt ausgerichtet sind.

- Method: Installieren Sie die tatsächlichen Anschlüsse und setzen Sie ein Dummy-Netzteil oder eine Lehre ein.

- Criteria: Reibungslose Einsteckkraft; kein Klemmen; Führungsstifte rasten vor den Steckverbindern ein.

7. Current Carrying Capability Test (Type Test)

- Objective: Validierung des Temperaturanstiegs unter Last.

- Method: Schalten Sie die Backplane mit dem maximalen Nennstrom ein und überwachen Sie die Temperatur mit einer Wärmebildkamera.

- Criteria: Temperaturanstieg < 30 °C (oder spezifizierter Grenzwert) im eingeschwungenen Zustand.

8. Ionic Contamination Test

- Objective: Sicherstellen der Sauberkeit der Platine, um Korrosion zu verhindern.

- Method: ROSE-Test (Resistivity of Solvent Extract).

- Criteria: < 1,56 µg/cm² NaCl-Äquivalent (Standard-IPC-Grenzwert).

Redundant Power Supply Unit (PSU) backplane design supplier qualification checklist (RFQ, audit, traceability)

Wenn Sie einen Partner für Redundant PSU backplane design auswählen, verwenden Sie diese Checkliste, um dessen Fähigkeiten zu überprüfen. Eine Standard-Leiterplattenfertigung kann das dicke Kupfer oder die erforderlichen strengen Toleranzen möglicherweise nicht bewältigen.

Group 1: RFQ Inputs (What you must provide)

- Gerber-Dateien (RS-274X oder X2) mit klarem Lagenaufbau.

- Fertigungszeichnung, die die IPC-Klasse (Klasse 2 oder 3) spezifiziert.

- Bohrtabelle (Drill Chart), die zwischen durchkontaktierten und nicht durchkontaktierten Löchern unterscheidet.

- Netzliste (IPC-356) zur Verifizierung des elektrischen Tests.

- "Read Me"-Datei mit detaillierten Sonderanforderungen (z. B. "Arrays nicht auskreuzen (Do not X-out arrays)", "Es gelten Einpresstoleranzen").

- Anforderungen an die Nutzenanordnung (Panelization), falls die Montage automatisiert ist.

- Kupfergewichtsangaben für jede Lage.

- Impedanzkontrolltabelle (falls zutreffend).

Group 2: Capability Proof (What the supplier must demonstrate)

- Erfahrung mit der Herstellung von Heavy Copper PCB (fragen Sie nach der maximalen Kapazität für das Kupfergewicht).

- Fähigkeit, dicke Platinen (bis zu 6 mm oder mehr) zu handhaben.

- Interne Ausrüstung für die Montage von Einpresssteckverbindern (wenn sie die Montage durchführen).

- UL-Zertifizierung (94V-0) für den spezifischen vorgeschlagenen Aufbau/Material.

- Automatische optische Inspektion (AOI), kalibriert für dicke Kupferbahnen.

- Röntgeninspektionskapazität für Multilayer-Registrierung.

Group 3: Quality System & Traceability

- ISO 9001-Zertifizierung (obligatorisch); IATF 16949 (bevorzugt für hohe Zuverlässigkeit).

- Materialrückverfolgbarkeit: Können sie die Harz-/Kupfercharge bis zur spezifischen Platine zurückverfolgen?

- Outgoing Quality Control (OQC) Berichte sind in der Lieferung enthalten.

- Querschnittsberichte für jede Charge bereitgestellt.

- Kalibrierungsaufzeichnungen für elektrische Tester.

- Handhabungsverfahren für feuchtigkeitsempfindliche Bauteile (MSD), falls eine Bestückung involviert ist.

Group 4: Change Control & Delivery

- PCN-Richtlinie (Product Change Notification): Werden Sie benachrichtigt, bevor Materialmarken gewechselt werden?

- DFM-Workflow: Liefern sie vor der Produktion einen detaillierten Engineering Query (EQ) Bericht?

- Verpackung: Vakuumversiegelt mit Trockenmittel und Feuchtigkeitsindikatorkarte.

- Kantenschutz: Verwenden sie beim Versand Schutzecken für schwere Backplanes?

- Stabilität der Vorlaufzeit für Sondermaterialien (High Tg, dickes Kupfer).

How to choose Redundant Power Supply Unit (PSU) backplane design (trade-offs and decision rules)

Im Ingenieurwesen geht es um Kompromisse. Hier erfahren Sie, wie Sie die widersprüchlichen Anforderungen im Redundant PSU backplane design navigieren.

1. Heavy Copper vs. Busbars

- If you need < 100A: Verwenden Sie Heavy Copper PCB (3 oz–4 oz). Es ist kostengünstig und integriert.

- If you need > 150A: Ziehen Sie eingebettete oder aufgeschraubte Stromschienen (Busbars) in Betracht. Das Ätzen von extrem dickem Kupfer (6 oz+) ist teuer und schränkt das Fine-Pitch-Routing für Signale ein.

2. High Tg FR-4 vs. Standard FR-4

- If operating temp is > 80°C or high layer count: Wählen Sie High Tg (170°C+). Es reduziert die Z-Achsen-Ausdehnung und Hülsenrisse.

- If low power/consumer grade: Standard-Tg (135 °C–150 °C) kann ausreichen, aber die Kosteneinsparungen sind im Vergleich zum Risiko oft vernachlässigbar.

3. Press-Fit vs. Wave Solder Connectors

- If the board is very thick (>3mm): Wählen Sie Press-Fit. Das Wellenlöten dicker Platinen ist schwierig (Probleme mit der Lochfüllung) und thermisch belastend.

- If the board is standard thickness (1.6mm): Wellenlöten ist Standard und für geringere Pin-Zahlen billiger.

4. Immersion Silver vs. ENIG

- If you prioritize shelf life and contact reliability: Wählen Sie ENIG. Es ist robust gegen Oxidation und hervorragend für Press-Fit geeignet.

- If you prioritize cost: Immersionssilber ist billiger, läuft aber leicht an, wenn es nicht richtig gehandhabt wird; allgemein nicht für hochzuverlässige Backplanes empfohlen.

5. Class 2 vs. Class 3 (IPC Standards)

- If "fail-safe" is the goal (Medical/Aerospace/Server): Wählen Sie IPC-Klasse 3. Sie erfordert eine dickere Beschichtung und strengere Fehlerkriterien.

- If standard industrial: IPC-Klasse 2 ist normalerweise ausreichend und kostet 15–20 % weniger.

Redundant Power Supply Unit (PSU) backplane design FAQ (cost, lead time, Design for Manufacturability (DFM) files, materials, testing)

Q: How does copper weight impact the cost of Redundant PSU backplane design? A: Eine Erhöhung des Kupfergewichts führt zu einem signifikanten Kostenanstieg.

- Material: Laminate aus dickem Kupfer sind teurer.

- Processing: Das Ätzen dauert länger und verbraucht Chemikalien schneller.

- Lamination: Erfordert mehr Prepreg (Harz) zum Füllen von Lücken, was zusätzliche Materialkosten verursacht.

Q: What is the typical lead time for a custom Redundant PSU backplane? A: Rechnen Sie mit 15–20 Arbeitstagen für Prototypen und 20–25 Tagen für die Produktion.

- Dickes Kupfer und High-Tg-Materialien können längere Beschaffungszyklen haben als Standard-FR-4.

- Komplexe Tests (Hi-Pot, Impedanz) verlängern den Prozess um 1–2 Tage.

Q: What DFM files are critical for Redundant PSU backplane design reviews? A: Neben Gerbers müssen Sie eine Bohrzeichnung mit strengen Toleranzen vorlegen.

- Fügen Sie eine "Lagenkarte" (Layer Map) bei, die genau zeigt, welche Lagen Stromversorgungsebenen sind.

- Stellen Sie das Datenblatt für die passenden Gegenstecker zur Verfügung, damit der CAM-Ingenieur die Pad-/Lochabmessungen überprüfen kann.

Q: Can I use standard FR-4 for a Redundant PSU backplane design? A: Es ist riskant.

- Standard-FR-4 hat eine niedrigere Tg (Glasübergangstemperatur) und einen höheren CTE (Ausdehnung).

- Unter der thermischen Belastung von redundanten Netzteilen kann Standard-FR-4 weich werden, was zu Pad-Cratering oder Hülsenrissen führt. Bevorzugen Sie immer High-Tg-Materialien.

Q: What are the acceptance criteria for press-fit connector holes? A: Die Lochtoleranz ist extrem eng, typischerweise ±0,05 mm (2 mil).

- Die Kupferbeschichtung in der Hülse muss glatt und durchgehend sein (min. 25 µm).

- Die Oberflächenbeschaffenheit (z. B. ENIG) darf den Lochdurchmesser nicht unter die Mindestspezifikation des Steckverbinderherstellers verringern.

Q: How do you test for latent defects in Redundant PSU backplane design? A: Latente Defekte (wie partieller CAF) sind im Standard-E-Test schwer zu erkennen.

- Verwenden Sie die Beschichtungsanforderungen der IPC-Klasse 3, um Robustheit zu gewährleisten.

- Führen Sie regelmäßige Zuverlässigkeitstests (thermisches Zyklieren) an Produktionsmustern durch, nicht nur an Prototypen.

Q: Why is "resin starvation" a risk in Redundant PSU backplane design? A: Dicke Kupferleiterbahnen erzeugen tiefe "Täler", die das Prepreg-Harz während der Laminierung füllen muss.

- Wenn das Prepreg nicht genügend Harzfluss aufweist, entstehen Hohlräume (Voids).

- Solution: Verwenden Sie Prepreg mit hohem Fluss oder "doppellagige" Prepreg-Schichten (Double-Ply) zwischen dicken Kupferschichten.

Q: Does APTPCB support DFM for Redundant PSU backplane design? A: Ja. Wir führen eine vollständige DFM-Prüfung der Leiterbahnbreiten, der Abstände für dickes Kupfer und der Wärmemanagementstrategien durch, bevor Metall geschnitten wird.

Resources for Redundant Power Supply Unit (PSU) backplane design (related pages and tools)

- Backplane PCB Manufacturing: Ein tiefer Einblick in die spezifischen Fertigungsprozesse für Backplanes mit hoher Lagenanzahl.

- Heavy Copper PCB Capabilities: Unverzichtbare Lektüre zum Verständnis der Designregeln und Stromtragfähigkeiten von Platinen aus dickem Kupfer.

- High Tg PCB Materials: Erfahren Sie, warum thermische Eigenschaften der wichtigste Faktor bei der Materialauswahl für Power-Platinen sind.

- DFM Guidelines: Allgemeine Design-for-Manufacturing-Regeln, um sicherzustellen, dass Ihr Backplane-Layout fabrikbereit ist.

- PCB Quality System: Verstehen Sie die Teststandards und Zertifizierungen, die Ihre Lieferkette schützen.

Request a quote for Redundant Power Supply Unit (PSU) backplane design (Design for Manufacturability (DFM) review + pricing)

Sind Sie bereit, Ihr Redundant PSU backplane design vom Konzept in die Produktion zu überführen? Wir bei APTPCB sind auf hochzuverlässige Power-Platinen spezialisiert. Senden Sie uns Ihre Daten für eine umfassende DFM-Überprüfung, bei der wir auf Probleme mit den Abständen bei dickem Kupfer, die Balance des Lagenaufbaus und die Eignung der Materialien prüfen, bevor Sie auch nur einen Cent bezahlen.

Was Sie in Ihre Angebotsanfrage aufnehmen sollten:

- Gerber Files: RS-274X oder ODB++ Format.

- Fabrication Drawing: PDF mit Angabe von Materialien (Tg), Kupfergewicht und Toleranzen.

- Volume: Prototypenmenge vs. geschätzter Jahresbedarf (EAU).

- Testing Requirements: Geben Sie an, ob Hi-Pot- oder Impedanztests erforderlich sind.

Klicken Sie hier, um ein Angebot anzufordern und erhalten Sie innerhalb von 24 Stunden eine technische Antwort.

Conclusion (next steps)

Beim erfolgreichen Redundant PSU backplane design geht es um mehr als nur das Verbinden von Pins; es geht um das Management von Wärme, mechanischer Belastung und Fertigungstoleranzen, um ein Fundament zu schaffen, das niemals versagt. Indem Sie strenge Materialspezifikationen definieren, die Risiken der Verarbeitung von dickem Kupfer verstehen und die Fähigkeiten Ihres Lieferanten anhand der bereitgestellten Checkliste validieren, können Sie sich ein zuverlässiges Stromverteilungssystem für Ihre kritische Infrastruktur sichern. Betrachten Sie die Backplane nicht als passive Komponente, sondern als das aktive Rückgrat der Zuverlässigkeitsstrategie Ihres Systems.