Hochgeschwindigkeits-Digitaldesign ist keine Nische mehr; es ist der Standard für moderne Elektronik. Da die Datenraten in den Multi-Gigabit-Bereich steigen, verschwindet der Fehlerspielraum, was eine rigorose SI-Signoff-Checkliste für Entwicklungsteams unerlässlich macht. Ohne einen strukturierten Verifizierungsprozess riskieren Designs Signalverschlechterung, Datenkorruption und kostspielige Leiterplatten-Respins.

Dieser Leitfaden dient als umfassende Ressource für Ingenieure und Projektmanager. Wir werden die kritischen Definitionen, die Erfolgsmetriken und die spezifischen Prüfpunkte durchgehen, die erforderlich sind, um ein Design vom Konzept bis zur Massenproduktion mit APTPCB (APTPCB PCB Factory) zu bringen.

Wichtige Erkenntnisse

- Definition: Ein SI (Signal Integrity) Signoff ist nicht nur eine Simulation; es ist eine umfassende Verifizierung, dass das Design die Timing-, Rausch- und elektromagnetischen Anforderungen vor der Fertigung erfüllt.

- Kritische Metriken: Erfolg wird gemessen an Impedanzkontinuität, Einfügedämpfung, Rückflussdämpfung und Augenöffnungsdiagramm.

- Der "versteckte" Faktor: Fertigungstoleranzen (Ätzen, Laminierungsdruck) beeinflussen die SI ebenso stark wie das Layout selbst.

- Co-Design: Ein effektiver Signoff erfordert

stackup and si co designvon Anfang des Projekts an, nicht erst am Ende. - Validierung: Die Simulation muss mit Messdaten (TDR/VNA) korreliert werden, um das

si channel budgetzu validieren. - Leistungsbewusstsein: Das moderne Signoff muss eine

leistungsbewusste SI-Analyseumfassen, da gleichzeitiges Schaltrauschen (SSN) Augendiagramme kollabieren lassen kann. - Ziel: Das ultimative Ziel ist eine "First Pass Success"-Platine, die in ihrer vorgesehenen Umgebung zuverlässig funktioniert.

Was eine SI-Signoff-Checkliste wirklich bedeutet (Umfang & Grenzen)

Bevor wir uns mit spezifischen Metriken befassen, müssen wir feststellen, dass ein robuster Signoff-Prozess weit über die Ausführung eines Software-Simulationstools hinausgeht.

Eine echte SI-Signoff-Checkliste ist ein Qualitätssicherungstor, das die Lücke zwischen theoretischem Design und physischer Realität schließt. Sie definiert den Umfang der erforderlichen Verifizierung, um sicherzustellen, dass elektrische Signale vom Sender zum Empfänger ohne unannehmbare Verzerrungen übertragen werden. Dieser Prozess umfasst drei unterschiedliche Grenzen: die Chipebene (IBIS/AMI-Modelle), die Package-Ebene und die Board-Ebene (Leiterbahnspuren und Vias).

Viele Ingenieure glauben fälschlicherweise, dass das Signoff abgeschlossen ist, sobald der Autorouter fertig ist oder ein grundlegender DRC (Design Rule Check) bestanden wurde. Physische Phänomene wie der Skin-Effekt, die dielektrische Verlust und der Fasergeflecht-Effekt erscheinen jedoch nicht in Standard-DRCs. Der Umfang des Signoffs muss Folgendes umfassen:

- Pre-Layout-Analyse: Definition von Randbedingungen und Stackups.

- In-Layout-Verifizierung: Echtzeitprüfung von Kopplung und Längenanpassung.

- Post-Layout-Simulation: Vollwellen-3D-Extraktion kritischer Netze.

- Fertigungskonformität: Sicherstellen, dass der Hersteller die Strukturen mit kontrollierter Impedanz innerhalb der Toleranz bauen kann.

Dieser ganzheitliche Ansatz stellt sicher, dass das aptpcb si support-Team ein Design erhält, das nicht nur theoretisch fundiert, sondern auch herstellbar ist.

Wichtige Metriken (wie man Qualität bewertet)

Sobald der Umfang definiert ist, benötigen wir spezifische quantitative Daten, um den Erfolg der Signalintegritätsstrategie zu messen.

Die folgenden Metriken sind die nicht verhandelbaren Leistungsindikatoren für Hochgeschwindigkeitsdesigns. Eine bestandene SI-Abnahme-Checkliste erfordert, dass diese Werte innerhalb der spezifischen Margen liegen, die durch den Schnittstellenstandard (z.B. PCIe, DDR, USB) definiert sind.

| Metrik | Warum es wichtig ist | Typischer Bereich oder Einflussfaktoren | Wie zu messen |

|---|---|---|---|

| Charakteristische Impedanz ($Z_0$) | Fehlanpassungen verursachen Reflexionen, reduzieren die Signalleistung und erhöhen das Rauschen. | $50\Omega$ (Single), $85\Omega$ oder $100\Omega$ (Diff). Toleranz $\pm 10%$ oder $\pm 5%$. | TDR (Time Domain Reflectometry) Simulation oder physischer Coupon-Test. |

| Einfügedämpfung (IL) | Bestimmt, wie viel Signalenergie verloren geht, wenn sie entlang der Leiterbahn wandert. | Gemessen in dB/Zoll. Abhängig von Frequenz, Dielektrikummaterial (Df) und Kupferrauheit. | S-Parameter ($S_{21}$) über VNA oder Simulation. |

| Rückflussdämpfung (RL) | Gibt an, wie viel Signal zur Quelle zurückreflektiert wird. | Sollte $<-10\text{dB}$ (oder niedriger) für die interessierende Frequenz sein. | S-Parameter ($S_{11}$). |

| Übersprechen (NEXT/FEXT) | Unerwünschte Kopplung zwischen benachbarten Leiterbahnen stört die Signalzeitgebung und Logikpegel. | $<-40\text{dB}$ ist ein gängiges Ziel. Beeinflusst durch Abstand (3W-Regel) und Referenzebenen. | 3D-Feldsolver-Simulation. |

| Augendiagramm Höhe/Breite | Visualisiert die Signalqualität und Rauschmarge am Empfänger. | Definiert durch das spezifische Protokoll (z.B. PCIe Gen5 erfordert spezifische Augenmasken). | Transiente Simulation (Bitfehlerratenanalyse). |

| Jitter (Gesamt-Jitter) | Zeitliche Abweichungen, die Daten-Latching-Fehler verursachen können. | Gemessen in Pikosekunden (ps) oder Unit Intervals (UI). Umfasst zufälligen und deterministischen Jitter. | Augendiagramm-Analyse. |

| PDN-Impedanz | Hohe Impedanz im Stromversorgungsnetzwerk (PDN) verursacht Spannungsrippel (SSN). | Die Zielimpedanz liegt üblicherweise im Milliohm ($m\Omega$)-Bereich bis zur Grenzfrequenz. | AC-Frequenz-Sweep der Leistungsebene. |

Auswahlhilfe nach Szenario (Kompromisse)

Das Verständnis dieser Metriken ermöglicht es Ingenieuren, spezifische Parameter basierend auf der einzigartigen Umgebung und den betrieblichen Einschränkungen des Designs zu priorisieren.

Verschiedene Hochgeschwindigkeitsprotokolle beanspruchen unterschiedliche Teile der SI-Signoff-Checkliste. Man kann nicht alles gleichzeitig optimieren; Kompromisse sind bezüglich Kosten, Dichte und Leistung unvermeidlich.

1. DDR-Speicherschnittstellen (DDR4/DDR5)

- Hauptaugenmerk: Timing-Skew und Setup-/Hold-Zeiten.

- Kompromiss: Sie müssen der Längenanpassung (Verzögerungsabstimmung) Vorrang vor dem absoluten Verlust einräumen.

- Anleitung: Verwenden Sie Fly-by-Topologien mit Vorsicht. Die Abnahme muss überprüfen, dass der Adress-/Befehlsbus jeden Chip zur richtigen Zeit relativ zum Takt erreicht. Eine

leistungsbewusste SI-Analyseist hier entscheidend, da Speicherbusse gleichzeitig schalten und massive transiente Ströme erzeugen.

2. SerDes-Verbindungen (PCIe, Ethernet, USB)

- Hauptaugenmerk: Einfügedämpfung und Rückflussdämpfung.

- Kompromiss: Die Längenanpassung ist weniger kritisch als die Minimierung von Via-Stubs und Impedanzdiskontinuitäten.

- Anleitung: Konzentrieren Sie sich auf das

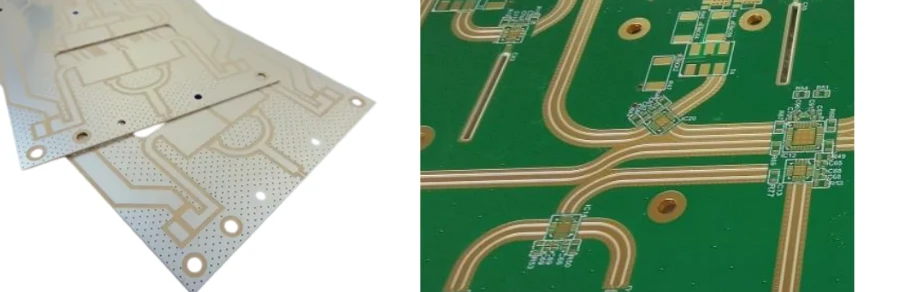

SI-Kanalbudget. Jeder Zoll Leiterbahn und jedes Via verbraucht einen Teil des zulässigen Verlusts. Möglicherweise müssen Sie verlustärmere Leiterplattenmaterialien wie Megtron 6 oder Rogers anstelle von Standard-FR-4 auswählen, um die Checkliste zu bestehen.

3. High-Density Interconnect (HDI) – Hochdichte Verbindungstechnik

- Hauptaugenmerk: Übersprechen und Stromversorgungs-Integrität.

- Kompromiss: Engere Leitungsführung erhöht das Übersprechrisiko.

- Anleitung: Bei der Verwendung von HDI-Leiterplatten-Technologie sind Microvias hervorragend für SI, da sie minimale Stubs aufweisen. Die dünnen Dielektrika erhöhen jedoch die Kapazität. Die Abnahme muss sicherstellen, dass Rückwege durch die dichten Via-Felder nicht unterbrochen werden.

4. Analog-/RF-Mixed-Signal

- Hauptaugenmerk: Isolation und Rauschuntergrenze.

- Kompromiss: Signalreinheit hat Vorrang vor Dichte.

- Anleitung: Die Checkliste muss die physische Trennung überprüfen. Schutzleiterbahnen und Via-Stitching sind erforderlich. Die Simulation sollte sich auf die Kopplung zwischen den rauschenden digitalen Abschnitten und empfindlichen analogen Eingängen konzentrieren.

5. Flex- und Starrflex-Designs

- Primärer Fokus: Impedanzkonsistenz während des Biegens.

- Kompromiss: Mechanische Flexibilität vs. elektrische Stabilität.

- Anleitung: Kreuzschraffierte Masseflächen werden oft für Flexibilität verwendet, ändern aber die Impedanzreferenz. Die Abnahme muss die spezifische Netzgeometrie berücksichtigen, die im Starrflex-Leiterplatten-Stackup verwendet wird.

6. Multi-Board-Systeme

- Primärer Fokus: Steckverbinder-Diskontinuitäten und Kabelmodelle.

- Kompromiss: Modulares Design vs. Signalkontinuität.

- Anleitung:

Multi board si correlationist entscheidend. Das Signal stoppt nicht am Rand der Leiterplatte. Das Simulationsdeck muss S-Parameter-Modelle für die Steckverbinder und die Gegenplatine enthalten, um sicherzustellen, dass der gesamte Kanal funktioniert.

Vom Design zur Fertigung (Implementierungs-Checkpoints)

Mit der ausgewählten Strategie gehen wir zur taktischen Ausführung der SI-Abnahme-Checkliste durch spezifische Designphasen über.

Dieser Abschnitt beschreibt die schrittweisen Checkpoints. Jeder Punkt enthält eine Empfehlung, das damit verbundene Risiko und die Akzeptanzmethode.

Phase 1: Pre-Layout und Stackup

- Stackup-Verifizierung

- Empfehlung: Definieren Sie Schichtanzahl, Kupfergewichte und dielektrische Materialien frühzeitig. Verwenden Sie einen Impedanzrechner, um Leiterbahnbreiten abzuschätzen.

- Risiko: Wenn sich der Lagenaufbau spät im Design ändert, sind alle Impedanzleiterbahnen falsch.

- Akzeptanz:

Stackup and si co design-Genehmigung vom Hersteller (APTPCB).

Materialauswahl

- Empfehlung: Wählen Sie Materialien basierend auf den Anforderungen an den Verlustfaktor (Df). Für >10 Gbit/s ist Standard-FR-4 wahrscheinlich unzureichend.

- Risiko: Übermäßige Signaldämpfung, die zu einem Verbindungsfehler führt.

- Akzeptanz: Überprüfung des Materialdatenblatts anhand des Verlustbudgets.

Einrichtung des Constraint-Managements

- Empfehlung: Geben Sie alle elektrischen Regeln (Skew, Topologie, Abstand) vor dem Routing in das CAD-Tool ein.

- Risiko: Manuelle Routing-Fehler, die visuell schwer zu erkennen sind.

- Akzeptanz: CAD-Constraint-Systemprüfung (keine Fehler).

Phase 2: Layout-Implementierung

Referenzebenenkontinuität

- Empfehlung: Stellen Sie sicher, dass jede Hochgeschwindigkeitsleiterbahn über einer durchgehenden Masseebene verläuft. Vermeiden Sie das Überqueren von Unterbrechungen.

- Risiko: Diskontinuität des Rückpfads erzeugt große Schleifeninduktivität, EMI und Signalreflexion.

- Akzeptanz: Visuelle Inspektion der Ebenenschichten relativ zu den Signalschichten.

Via-Optimierung & Backdrilling

- Empfehlung: Minimieren Sie die Via-Nutzung. Bei dicken Leiterplatten spezifizieren Sie Rückbohrungen, um ungenutzte Via-Stummel zu entfernen.

- Risiko: Via-Stummel wirken als Antennen und verursachen Resonanzen und starke Signaleinbrüche.

- Akzeptanz: 3D-Via-Simulation, die eine akzeptable Resonanzfrequenz zeigt.

Übersprechdämpfung (Crosstalk Mitigation)

- Empfehlung: Halten Sie einen $3W$-Abstand (Mittenabstand ist 3x Leiterbahnbreite) für kritische Netze ein.

- Risiko: Datenkorruption aufgrund von Rauschkopplung.

- Akzeptanz: Kopplungssimulation, die NEXT/FEXT innerhalb der Grenzen zeigt.

Platzierung von Entkopplungskondensatoren

- Empfehlung: Platzieren Sie Kondensatoren so nah wie möglich an den IC-Stromversorgungs-Pins, um die Schleifeninduktivität zu minimieren.

- Risiko: Spannungsabfall, der IC-Resets oder Logikfehler verursacht.

- Akzeptanz: PDN-Analyse-Simulation.

Phase 3: Post-Layout und Sign-off

Full-Wave-Extraktion

- Empfehlung: Extrahieren Sie S-Parameter für die kritischsten Netze (z.B. PCIe-Lanes, DDR-Datengruppen).

- Risiko: 2D-Approximationen übersehen 3D-Effekte wie Via-Kopplung.

- Akzeptanz: Vergleich der S-Parameter mit der Schnittstellenspezifikationsmaske.

IBIS-AMI-Simulation

- Empfehlung: Führen Sie Kanalsimulationen mit vom Hersteller bereitgestellten IBIS-AMI-Modellen für Tx und Rx durch.

- Risiko: Passive S-Parameter sehen gut aus, aber der aktive Silizium kann den Kanal nicht treiben.

- Akzeptanz: Die Augenöffnungsbreite erfüllt die Höhen-/Breitenanforderungen bei einer spezifischen BER (z.B. $10^{-12}$).

- Analyse der Fertigungstoleranzen

- Empfehlung: Eckfälle simulieren (z.B. Impedanz +10%, Dielektrikumsdicke -10%).

- Risiko: Das Design funktioniert in der nominalen Simulation, versagt aber in der Massenproduktion.

- Akzeptanz: Monte-Carlo-Analyse oder Bestehen der Eckfälle.

Häufige Fehler (und der richtige Ansatz)

Selbst mit einer robusten Checkliste können sich subtile Fehler einschleichen, wenn das Entwicklungsteam die Fertigungsrealitäten übersieht.

Den Rückweg ignorieren:

- Fehler: Eine Hochgeschwindigkeitsleitung über eine Trennung in der Masseebene zu führen oder Referenzschichten ohne ein Stitching-Via zu wechseln.

- Korrektur: Visualisieren Sie immer den Stromkreis. Der Rückstrom folgt dem Pfad des geringsten Induktivität (direkt unter dem Signal). Wenn Sie die Schichten wechseln, platzieren Sie ein Masse-Via neben dem Signal-Via.

Datenblätter übermäßig vertrauen:

- Fehler: Die "Marketing"-Dk/Df-Werte aus einem Laminat-Datenblatt verwenden.

- Korrektur: Verwenden Sie die Werte für die spezifische Frequenz und den Harzgehalt des verwendeten Prepregs. Fragen Sie APTPCB nach den spezifischen Materialparametern für Ihren Lagenaufbau.

Via-Stubs vernachlässigen:

- Fehler: Ein Signal von Schicht 1 zu Schicht 3 auf einer 20-Lagen-Platine zu führen und den Rest des Vias plattiert zu lassen.

- Korrektur: Verwenden Sie Blind-/Buried-Vias oder geben Sie Backdrilling an. Ein langer Stub ist ein Killer für Signale über 5 Gbit/s.

Fokus nur auf die Leiterplatte:

- Fehler: Das PCB-Layout perfektionieren, aber den Stecker und das Kabel ignorieren.

- Korrektur: Führen Sie eine

Multi-Board-SI-Korrelationdurch. Der Kanal umfasst alles zwischen dem Sender-Die und dem Empfänger-Die.

Den Fasergeflecht-Effekt vergessen:

- Fehler: Differenzielle Paare parallel zum Glasgewebe des PCB-Materials routen.

- Korrektur: Routen Sie in einem leichten Winkel (Zickzack-Routing) oder verwenden Sie "Spread Glass"-Materialien, um Skew zu verhindern, bei dem ein Bein des Paares über Glas und das andere über Harz verläuft.

Power Integrity überspringen:

- Fehler: Annehmen, dass eine durchgehende Ebene ausreicht.

- Korrektur: Führen Sie eine

Power-Aware-SI-Analysedurch. Rauschen auf der Stromschiene koppelt in das Signal ein und schließt das Augendiagramm (SSN).

Häufig gestellte Fragen (FAQ)

Um diese potenziellen Fallstricke weiter zu verdeutlichen, finden Sie hier Antworten auf die häufigsten Fragen zur Überprüfung der Signalintegrität.

F: Bei welcher Frequenz benötige ich eine formale SI-Abnahme-Checkliste? A: Im Allgemeinen werden SI-Effekte signifikant, wenn die Anstiegszeit Ihres Signals weniger als 1 ns beträgt oder die Frequenzen 500 MHz überschreiten. Für Schnittstellen wie DDR3/4, PCIe oder Gigabit Ethernet ist dies obligatorisch.

F: Kann APTPCB bei der Impedanzberechnung helfen? A: Ja. Wir bieten detaillierte Unterstützung beim Lagenaufbau und haben einen Online-Impedanzrechner, der Ihnen hilft, die Leiterbahnbreiten vor Beginn des Layouts abzuschätzen.

F: Was ist der Unterschied zwischen Pre-Layout- und Post-Layout-Simulation? A: Pre-Layout dient der Exploration (Definition von Regeln, Lagenaufbau und Topologie). Post-Layout dient der Verifikation (Überprüfung des tatsächlich gerouteten Kupfers anhand dieser Regeln).

F: Wie wirkt sich das Rückbohren auf die Kosten aus? A: Das Rückbohren fügt einen Prozessschritt hinzu, was die Kosten leicht erhöht. Bei Hochgeschwindigkeits-Leiterplatten-Designs ist es jedoch oft günstiger als die Verwendung teurer HDI-Aufbautechnologien, um die gleiche Signalqualität zu erreichen.

F: Welche Daten muss ich für eine SI-Überprüfung senden? A: Sie müssen in der Regel die ODB++- oder Gerber-Dateien, die IPC-356-Netzliste, den gewünschten Lagenaufbau und ein Dokument mit den Frequenzzielen und Impedanzanforderungen bereitstellen.

F: Warum stimmt meine Simulation nicht mit der Labormessung überein? A: Abweichungen resultieren oft aus ungenauen Materialmodellen (Dk/Df), dem Ignorieren von Steckermodellen oder der Nichtberücksichtigung von Fertigungsätzungstoleranzen (trapezförmige Leiterbahnformen).

F: Was ist "Power Aware" SI? A: Es ist ein Simulationsmodus, der die Schwankungen in den Versorgungsspannungsschienen berücksichtigt, während Signale schalten. Die Standard-SI-Simulation geht von einer idealen, perfekten Stromversorgung aus, was unrealistisch ist.

F: Benötige ich eine 3D-Simulation für jedes Netz? A: Nein. Die 3D-Simulation ist zeitaufwändig. Verwenden Sie sie nur für kritische Hochgeschwindigkeitsnetze, Vias und komplexe Geometrien. Standard-2D-Solver sind für Steuersignale mit geringerer Geschwindigkeit ausreichend.

Glossar (Schlüsselbegriffe)

Zur Klarheit für alle Teams definieren wir die in diesem Leitfaden verwendete technische Terminologie.

| Begriff | Definition |

|---|---|

| Dämpfung | Die Reduzierung der Signalamplitude, während es sich durch das Medium bewegt (Verlust). |

| Backdrilling | Ein Fertigungsprozess zur Entfernung des ungenutzten Teils (Stumpf) eines durchkontaktierten Vias. |

| BER (Bitfehlerrate) | Die Anzahl der Bitfehler pro Zeiteinheit. Ein übliches Ziel ist $10^{-12}$. |

| Übersprechen | Elektromagnetische Kopplung zwischen zwei benachbarten Signalen (Nahnebensprechen NEXT, Fernnebensprechen FEXT). |

| Dk (Dielektrizitätskonstante) | Ein Maß für die Fähigkeit eines Materials, elektrische Energie zu speichern. Beeinflusst die Ausbreitungsgeschwindigkeit und Impedanz. |

| Df (Verlustfaktor) | Ein Maß für die als Wärme im dielektrischen Material verlorene Energie. Beeinflusst die Einfügedämpfung. |

| Augendiagramm | Eine Oszilloskopanzeige, bei der ein digitales Signal wiederholt abgetastet wird, um die Signalqualität zu zeigen. |

| IBIS-Modell | Input/Output Buffer Information Specification. Ein Verhaltensmodell des Puffers der Komponente. |

| Impedanz ($Z_0$) | Der Widerstand gegen den Stromfluss in einer Übertragungsleitung. Muss angepasst werden, um Reflexionen zu verhindern. |

| ISI (Intersymbolinterferenz) | Verzerrung eines Signals, bei der ein Symbol nachfolgende Symbole stört (verursacht durch Verlust/Dispersion). |

| Jitter | Die Abweichung von der wahren Periodizität eines angenommenen periodischen Signals (Timing-Rauschen). |

| PDN (Stromversorgungsnetzwerk) | Das komplette System zur Stromversorgung, einschließlich VRMs, Ebenen, Kondensatoren und Vias. |

| Skew | Die Zeitdifferenz zwischen zwei Signalen (z.B. zwischen Takt und Daten, oder P und N eines Differenzpaares). |

| Skin-Effekt | Die Tendenz von Hochfrequenzstrom, nur auf der äußeren Oberfläche des Leiters zu fließen. |

| Stub | Ein offenes Ende einer Übertragungsleitung (oft ein Via), das Reflexionen verursacht. |

| TDR (Zeitbereichsreflektometrie) | Eine Messtechnik zur Bestimmung des Impedanzprofils einer Leiterbahn. |

Fazit (nächste Schritte)

Ein zuverlässiges Hochgeschwindigkeitsdesign zu erreichen, ist ein systematischer Prozess, kein Ratespiel. Durch die Einhaltung einer umfassenden SI-Abnahme-Checkliste stellen Sie sicher, dass jeder Aspekt des Signalpfades – vom Silizium-Die bis zur Gewebestruktur des PCB-Materials – berücksichtigt wird. Dies reduziert das Risiko, dass teure Prototypen im Labor fehlschlagen, und beschleunigt Ihre Markteinführungszeit.

Der Schlüssel zum Erfolg liegt in der frühen Zusammenarbeit. Warten Sie nicht, bis das Layout fertig ist, um über Signalintegrität nachzudenken. Beginnen Sie sofort mit dem Stackup- und SI-Co-Design.

Bereit, Ihr Design in Produktion zu geben? Um sicherzustellen, dass Ihre Hochgeschwindigkeitsplatine genau wie simuliert gefertigt wird, stellen Sie APTPCB während der Angebotsphase Folgendes zur Verfügung:

- Gerber/ODB++-Dateien: Das vollständige physische Layout.

- Lagenaufbau-Definition: Einschließlich spezifischer Materialanforderungen (z. B. Rogers, Megtron oder High-Tg FR4).

- Impedanztabelle: Auflistung der Zielimpedanz, Leiterbahnbreiten und Referenzlagen.

- SI-Anforderungen: Spezifische Testanforderungen wie TDR-Berichte oder Rückbohrpositionen.

Kontaktieren Sie APTPCB noch heute, um Ihr Design zu überprüfen und sicherzustellen, dass Ihr nächstes Hochgeschwindigkeitsprojekt auf Anhieb erfolgreich ist.