Die Siliziumkarbid (SiC)-Technologie hat die Leistungselektronik mit schnelleren Schaltgeschwindigkeiten und höherer Effizienz revolutioniert, aber diese Vorteile bringen erhebliche Layout-Herausforderungen mit sich. Die Implementierung korrekter Best Practices für SiC-Inverter-Gate-Treiber-PCBs ist der einzige Weg, um katastrophale Ausfälle durch parasitäre Induktivität, Überschwingen und elektromagnetische Interferenzen (EMI) zu verhindern. Im Gegensatz zu herkömmlichen IGBTs schalten SiC-MOSFETs mit extrem hohen dV/dt-Raten, was bedeutet, dass selbst wenige Nanohenry Streuinduktivität Spannungsüberschwingungen verursachen können, die das Bauteil zerstören oder das Gate-Signal verfälschen.

Bei APTPCB (APTPCB PCB Factory) sehen wir viele Designs scheitern, nicht wegen des Schaltplans, sondern weil das physikalische Layout die einzigartige Physik von Wide-Bandgap-Halbleitern ignorierte. Dieser Leitfaden bietet eine umfassende Checkliste, Spezifikationsbereiche und Schritte zur Fehlerbehebung, um sicherzustellen, dass Ihr SiC-Inverter-Gate-Treiber-PCB-Design robust, herstellbar und zuverlässig ist.

Kurzantwort (30 Sekunden)

Für Ingenieure, die sofortige Anweisungen zu Best Practices für SiC-Inverter-Gate-Treiber-PCBs benötigen, konzentrieren Sie sich vor allem auf die Minimierung der Schleifenfläche.

- Gate-Schleifeninduktivität minimieren: Platzieren Sie den Gate-Treiber so nah wie physisch möglich am SiC-MOSFET. Die gesamte Leiterbahnlänge sollte idealerweise unter 20 mm liegen.

- Kelvin-Source-Verbindungen verwenden: Trennen Sie immer den Stromversorgungspfad vom Gate-Treiber-Rückpfad, um zu verhindern, dass eine gemeinsame Source-Induktivität das Schalten verlangsamt oder Fehlauslösungen verursacht.

- Entkopplungskondensatoren optimieren: Platzieren Sie Keramikkondensatoren mit niedrigem ESL (C0G/NP0) direkt an den Versorgungsanschlüssen des Treibers.

- CMTI (Gleichtakt-Transientenfestigkeit) kontrollieren: Stellen Sie sicher, dass die Isolationsbarriere (Optokoppler oder digitaler Isolator) eine CMTI-Bewertung von >100 kV/µs aufweist und minimieren Sie die Kopplungskapazität über den Isolationsspalt.

- Lagenaufbau-Strategie: Verwenden Sie einen 4- oder 6-Lagen-Aufbau mit einer durchgehenden Massefläche direkt neben der Signalschicht, um vor Rauschen abzuschirmen.

- Luft- und Kriechstrecken für Hochspannung: SiC-Wechselrichter arbeiten oft bei 800V+; stellen Sie sicher, dass Kriech- und Luftstrecken die IEC 60664-1-Standards erfüllen (typischerweise >8mm für verstärkte Isolation).

Wann Best Practices für SiC-Inverter-Gate-Treiber-PCBs angewendet werden sollten (und wann nicht)

Zu verstehen, wann diese strengen Standards strikt angewendet werden sollten, hilft, Kosten und Leistung auszugleichen.

Wann diese Best Practices strikt angewendet werden sollten:

- Hochspannungs-EV-Antriebsstränge: Systeme, die mit 400V- oder 800V-Batteriearchitekturen betrieben werden, bei denen dV/dt 50 V/ns überschreitet.

- Hochfrequenzschaltung: Wandler, die über 50 kHz laufen, wo Schaltverluste dominieren und parasitäre Resonanzen wahrscheinlicher sind.

- Designs mit hoher Leistungsdichte: Kompakte Wechselrichter, bei denen Wärmemanagement und Bauteilnähe das Risiko von Übersprechen erhöhen.

- Sicherheitskritische Anwendungen: Automotive-Traktionswechselrichter oder Industrierobotik, bei denen ein Gate-Fehlzündung zu Hardware-Zerstörung oder Sicherheitsrisiken führen könnte.

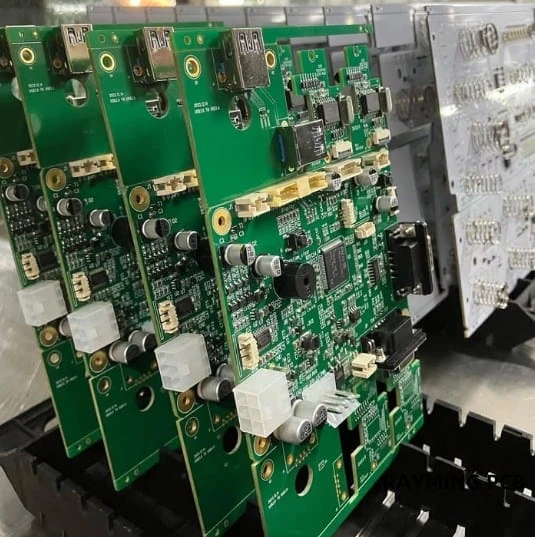

- SiC-Inverter-Gate-Treiber-Leiterplattenbestückung: Wenn der Bestückungsprozess empfindliche Bare Dies oder dicht gepackte oberflächenmontierte Komponenten umfasst, die eine präzise Lötpastenkontrolle erfordern.

Wann Standard-Leiterplattenpraktiken ausreichen könnten (und diese Regeln übertrieben sind):

- Niederspannungs-Silizium-MOSFETs: Wenn Sie Standard-24V- oder 48V-Silizium-FETs mit langsamen Schaltgeschwindigkeiten verwenden, sind Standard-Layout-Regeln in der Regel ausreichend.

- Niederfrequenz-IGBT-Antriebe: Ältere Motorantriebe, die bei <5 kHz schalten, sind weniger empfindlich gegenüber parasitärer Induktivität im Vergleich zu SiC.

- Kostensensible Unterhaltungselektronik: Leistungsarme Adapter, bei denen Effizienzgewinne durch SiC die erhöhten Leiterplattenherstellungskosten für spezialisierte Materialien nicht rechtfertigen.

- Prototypenbau auf Steckplatinen: Obwohl nicht für die Leistung empfohlen, erfordert das anfängliche Logiktesten bei niedriger Spannung keine Impedanzkontrolle (obwohl es die reale Leistung nicht widerspiegelt).

Regeln & Spezifikationen

Im Kontext der Anwendung müssen spezifische parametrische Regeln definiert werden, um den Layout-Prozess zu leiten. Die folgende Tabelle skizziert die kritischen Spezifikationen für Best Practices bei SiC-Inverter-Gate-Treiber-Leiterplatten.

| Regel | Empfohlener Wert/Bereich | Warum es wichtig ist | Wie zu überprüfen | Wenn ignoriert |

|---|---|---|---|---|

| Gate-Leiterbahnlänge | < 20 mm (Max) | Reduziert parasitäre Induktivität ($L_g$), die Klingeln verursacht. | Im CAD-Layout-Tool messen. | Gate-Oszillation, potenzielle MOSFET-Zerstörung. |

| Gate-Leiterbahnbreite | > 20 mil (0,5 mm) | Senkt Widerstand und Induktivität; bewältigt Spitzenströme (oft >5A). | Leiterbahnbreitenbeschränkungen prüfen. | Langsames Schalten, überhitzende Leiterbahnen. |

| Gate-Schleifenfläche | Minimieren (Enge Kopplung) | Große Schleifen wirken als Antennen für EMI und erhöhen die Induktivität. | Sichtprüfung; überlappende Leiterbahnen auf benachbarten Lagen führen. | Hohe EMI, falsches Einschalten (Miller-Effekt). |

| Kriechstrecke der Isolation | > 8 mm (für 800V-Systeme) | Verhindert Überschläge über die Isolationsbarriere. | DRC (Design Rule Check) im CAD. | Dielektrischer Durchschlag, Sicherheitsversagen. |

| CMTI-Bewertung | > 100 kV/µs | SiC-Schalter sind schnell; Bauteile mit niedrigem CMTI werden während der Übergänge Störungen aufweisen. | Komponentendatenblatt prüfen. | Verlust der Gate-Steuerung während des Schaltens. |

| Abstand des Entkopplungskondensators | < 2 mm vom Pin | Liefert sofortigen Strom zum Schalten; stabilisiert VDD. | Visuelle Platzierungsprüfung. | VDD-Einbruch, unregelmäßiges Treiberverhalten. |

| Via-Induktivität | Minimieren (Mehrere Vias verwenden) | Einzelne Vias fügen ~1nH hinzu; mehrere Vias parallel reduzieren dies. | Vias auf Hochstrompfaden zählen. | Erhöhte Pfadimpedanz, Überschwingen. |

| Desat-Leiterbahnabstand | > 0,5 mm Trennung | Die Desaturationserkennung ist empfindlich gegenüber Rauschkopplung. | DRC-Abstandsregeln. | Falsche Fehlerabschaltung. |

| Massefläche | Solide, Ununterbrochen | Bietet Rückweg und Abschirmung. | Gerber-Dateien auf Unterbrechungen überprüfen. | Masseprellen, Verlust der Signalintegrität. |

| Kupfergewicht | 2 oz oder höher | Bewältigt hohe Dauerströme und unterstützt die Wärmeableitung. | In den Fertigungsnotizen angeben. | Thermische Hotspots, Leiterbahnverschmelzung. |

| Material-Tg | > 170°C (Hohe Tg) | SiC wird heiß; Standard-FR4 kann delaminieren. | Materialdatenblatt prüfen (z.B. Isola 370HR). | Leiterplattendelamination, Durchkontaktierungsrisse. |

| Symmetrie | Anpassung Hoch-/Niedrigseite | Asymmetrie verursacht Zeitversatz und ungleichmäßige Belastung. | Leiterbahnlängen für H-Brücke messen. | Durchschussrisiko, ungleichmäßige thermische Belastung. |

Implementierungsschritte

Sobald die Spezifikationen verstanden sind, muss das Design methodisch umgesetzt werden. Hier ist der Schritt-für-Schritt-Workflow zur Implementierung der Best Practices für SiC-Inverter-Gate-Treiber-Leiterplatten.

- Strategie zur Bauteilplatzierung

- Aktion: Platzieren Sie zuerst die SiC-MOSFETs und die Gate-Treiber-ICs.

- Schlüsselparameter: Abstand < 20mm.

- Abnahmekontrolle: Überprüfen Sie, ob der Treiberausgangspin direkt dem MOSFET-Gate-Pin gegenüberliegt, um mäandernde Leiterbahnen zu vermeiden.

- Kelvin-Source-Routing

- Aktion: Führen Sie die Gate-Rückleitung direkt zum Source-Pin des MOSFETs, getrennt von der Hauptmasseebene.

- Schlüsselparameter: Der Kelvin-Verbindungspunkt muss am Pad liegen.

- Abnahmekontrolle: Stellen Sie sicher, dass die "Power Source" und die "Driver Source" keinen gemeinsamen Pfad bis zum MOSFET-Pin teilen.

- Gate-Schleifen-Optimierung

- Aktion: Führen Sie die Gate- und Rückleiterbahnen auf benachbarten Lagen (z.B. Lage 1 und Lage 2) exakt übereinander.

- Schlüsselparameter: Schleifeninduktivität < 10 nH.

- Abnahmekontrolle: Verwenden Sie einen PCB-Viewer oder ein 3D-Tool, um die Schleifenfläche zu visualisieren; sie sollte wie eine Linie und nicht wie ein Kreis aussehen.

- Minimierung der Leistungsschleife

- Aktion: Platzieren Sie den DC-Zwischenkreis-Kondensator so nah wie möglich an der Halbbrücke, um die Kommutierungsschleife zu minimieren.

- Schlüsselparameter: Businduktivität < 20 nH.

- Abnahmekontrolle: Überprüfen Sie, dass sich die positiven und negativen Busplatten stark überlappen, um Magnetfelder aufzuheben.

- Design der Isolationsbarriere

- Aktion: Erstellen Sie eine klare „Keep-out“-Zone unter den Isolationskomponenten (Optokoppler/Transformatoren). Entfernen Sie in dieser Zone jegliches Innenlagenkupfer.

- Schlüsselparameter: Kriechstrecke > 8mm (systemabhängig).

- Abnahmekontrolle: Führen Sie eine Hochspannungs-DRC durch, um sicherzustellen, dass kein Kupfer den Isolationsabstand verletzt.

- Layout des Entkopplungskondensators

- Aktion: Platzieren Sie C0G/NP0-Keramikkondensatoren unmittelbar an den VDD/VEE-Pins des Treibers.

- Schlüsselparameter: Leiterbahnlänge zum Kondensator < 2mm.

- Abnahmekontrolle: Stellen Sie sicher, dass die Vias, die Kondensatoren mit Masse verbinden, verdoppelt oder verdreifacht werden, um die Induktivität zu reduzieren.

- Thermische Via-Verbindung (Stitching)

- Aktion: Platzieren Sie Arrays von thermischen Vias unter den freiliegenden Pads des Treibers und der MOSFETs.

- Schlüsselparameter: Via-Durchmesser 0.3mm, Rastermaß 0.6mm.

- Abnahmekontrolle: Überprüfen Sie, ob die Lötstopplacköffnung die Wärmeableitung ermöglicht, aber das Aufsteigen von Lot verhindert (Tenting oder Plugging kann erforderlich sein).

- DFM-Überprüfung für die Montage

- Aktion: Überprüfen Sie den Komponentenabstand für die automatisierte Bestückung, insbesondere bei Leiterplatten mit hoher Kupferauflage.

- Schlüsselparameter: Min. Komponentenabstand.

- Abnahmekontrolle: Konsultieren Sie die DFM-Richtlinien, um sicherzustellen, dass das Design in Serie herstellbar ist.

Fehlermodi & Fehlerbehebung

Auch bei einem rigorosen Designprozess können während der Tests Probleme auftreten. Die Fehlerbehebung bei den Best Practices für SiC-Inverter-Gate-Treiber-PCBs erfordert die Identifizierung spezifischer Symptome, die auf Layoutfehler hinweisen.

Symptom: Übermäßiges Überschwingen der Gate-Spannung

- Ursache: Hohe parasitäre Induktivität in der Gate-Schleife.

- Prüfung: Messen Sie die Länge der Leiterbahn vom Treiber zum Gate. Überprüfen Sie auf Vias im Gate-Pfad.

- Behebung: Leiterbahnen kürzen; Vias wenn möglich entfernen. Eine Ferritperle hinzufügen oder den Gate-Widerstand ($R_g$) leicht erhöhen (Kompromiss mit der Schaltgeschwindigkeit).

- Prävention: Verwenden Sie Stripline-Routing oder Microstrip mit einer unmittelbar darunter liegenden Massefläche.

Symptom: Falsches Einschalten (Miller-Effekt)

- Ursache: Hohe dV/dt-Kopplung durch die Miller-Kapazität ($C_{gd}$) erhöht die Gate-Spannung.

- Prüfung: Suchen Sie nach Spannungsspitzen am Gate des AUS-Geräts, wenn das EIN-Gerät schaltet.

- Behebung: Implementieren Sie eine aktive Miller-Klemme oder verwenden Sie eine negative Ausschaltspannung (z. B. -5V).

Prävention: Halten Sie die Impedanz des Gate-Abschaltpfads extrem niedrig.

Symptom: Treiber-Latch-Up oder Reset

- Ursache: Verletzung der Gleichtakt-Transientenimmunität (CMTI) oder Masserückprall.

- Prüfung: Überprüfen Sie die Isolationsfestigkeit des Treibers. Überprüfen Sie die Massenpotenzialdifferenz zwischen Logik- und Leistungsseite.

- Behebung: Gleichtaktdrosseln hinzufügen; Isolationskapazität verbessern.

- Prävention: Gate-Treiber mit CMTI > 100 kV/µs auswählen.

Symptom: MOSFET-Überhitzung (Statisch)

- Ursache: Gate-Spannung erreicht keine volle Sättigung (z.B. 15V oder 18V) oder schlechter Wärmepfad.

- Prüfung: $V_{gs}$ am Pin messen. Thermische Durchkontaktierungs-Kontinuität prüfen.

- Behebung: Leiterbahnbreite für die Stromversorgung des Treibers erhöhen; Kühlkörperbefestigung verbessern.

- Prävention: Dickes Kupfer (2oz+) und hochleistungsfähige thermische Substrate verwenden.

Symptom: EMI/EMV-Testfehler

- Ursache: Große Leistungskommutierungsschleifen wirken als Antennen.

- Prüfung: Analysieren Sie die physikalische Fläche der DC+ zu DC- Schleife einschließlich des Schalters.

- Behebung: Snubber-Schaltungen (RC oder RCD) hinzufügen; Abschirmung verbessern.

- Prävention: Laminares Busbar-Design oder überlappende PCB-Leistungsebenen.

Symptom: Dielektrischer Durchschlag (Lichtbogenbildung)

- Ursache: Unzureichende Kriech-/Luftstrecke für die Betriebshöhe oder den Verschmutzungsgrad.

- Prüfung: Überprüfen Sie die Leiterplatte auf Kohlespuren oder Verbrennungen über Isolationsspalten.

Behebung: Fräsen von Schlitzen (Ausschnitten) in der Leiterplatte, um den Kriechweg zu vergrößern.

Prävention: Befolgen Sie beim Layout strikt die Tabellen der IEC 60664-1.

Designentscheidungen

Die Fehlersuche führt oft zu grundlegenden Designentscheidungen zurück, die früh im Projekt getroffen wurden.

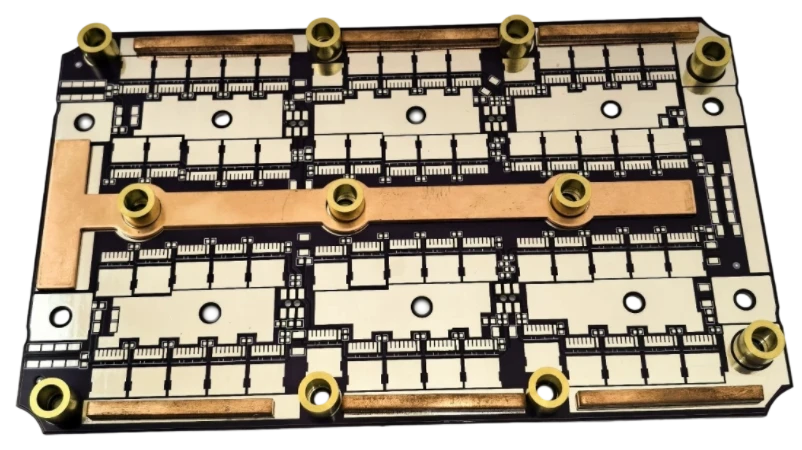

Auswahl des Lagenaufbaus Für SiC-Wechselrichter ist eine Standard-2-Lagen-Platine aufgrund der Notwendigkeit geringer Induktivität selten ausreichend.

- 4-Lagen-Aufbau: Signal / Masse / Leistung / Signal. Dies ist das empfohlene Minimum. Die interne Masseebene wirkt als Abschirmung und reduziert die Schleifeninduktivität für Leiterbahnen auf der obersten Lage.

- 6-Lagen-Aufbau: Ermöglicht dedizierte Abschirmlagen und eine bessere Isolation zwischen Hochspannungs- und Niederspannungslogik.

Materialauswahl Standard-FR4 (Tg 130-140°C) ist möglicherweise nicht für die thermische Zyklisierung von Hochleistungs-SiC-Anwendungen geeignet.

- Hoher Tg FR4: Materialien wie Isola 370HR (Tg 180°C) werden für die Zuverlässigkeit empfohlen.

- Schweres Kupfer: Die Verwendung von 2oz, 3oz oder sogar 4oz Kupfer hilft bei der Wärmeverteilung und reduziert den Widerstand von Hochstrombahnen.

Gate-Treiber-Topologie

- Isoliert vs. Nicht-isoliert: Hochspannungs-Wechselrichter erfordern ausnahmslos eine galvanische Trennung (optisch, kapazitiv oder magnetisch).

- Bipolare Versorgung: Die Verwendung von +15V/-5V ist eine Standard-Designentscheidung, um ein falsches Einschalten zu verhindern, was spezifische Layout-Überlegungen für die Stromversorgung auf der Leiterplatte erfordert.

Häufig gestellte Fragen (FAQ)

F: Was ist die kritischste Regel für das Layout von SiC-Gate-Treibern? A: Die Minimierung der Gate-Schleifeninduktivität ist am kritischsten.

- Leiterbahnen kurz halten (<20mm).

- Gate- und Rückleiterbahnen parallel und eng beieinander führen.

- Vias im Gate-Pfad vermeiden.

F: Benötige ich wirklich eine negative Gate-Spannung für SiC? A: Obwohl einige SiC-FETs bei 0V ausgeschaltet betrieben werden können, wird eine negative Spannung (-3V bis -5V) dringend empfohlen.

- Sie bietet eine Sicherheitsmarge gegen das Einschalten durch den Miller-Effekt.

- Sie beschleunigt die Ausschaltzeiten.

F: Kann ich Standard-FR4 für SiC-Inverter-PCBs verwenden? A: Das hängt von Temperatur und Spannung ab.

- Für Prototypen oder geringere Leistung ist Standard-FR4 in Ordnung.

- Für hohe Leistungsdichte oder Automotive-Anwendungen High-Tg-Materialien verwenden, um thermisches Versagen zu verhindern.

F: Wie berechne ich den erforderlichen Kriechweg? A: Beziehen Sie sich auf Normen wie IEC 60664-1.

- Bestimmen Sie die Betriebsspannung (z.B. 800V).

- Bestimmen Sie den Verschmutzungsgrad (üblicherweise 2 für versiegelt, 3 für offen).

- Wählen Sie die Materialgruppe (CTI-Wert).

F: Warum ist CMTI für SiC wichtig? A: SiC-Schalter haben sehr schnelle Spannungsflanken (hohes dV/dt).

- Treiber mit niedrigem CMTI interpretieren dieses Rauschen als Signal.

- Dies verursacht Glitches oder Synchronisationsverlust.

F: Wie beeinflusst die Leiterbahnbreite den Gate-Treiber? A: Dünne Leiterbahnen haben eine höhere Induktivität und Widerstand.

- Dies begrenzt den Spitzenstrom, den der Treiber liefern/ziehen kann.

- Es verlangsamt das Schalten und erhöht die Schaltverluste.

F: Sollte ich eine Ferritperle am Gate verwenden? A: Eine Ferritperle kann hochfrequentes Klingeln unterdrücken.

- Es fügt bei hohen Frequenzen Widerstand hinzu, ohne den DC-Antrieb zu beeinflussen.

- Platzieren Sie es nahe am Gate-Pin.

F: Was ist der Vorteil von Kelvin-Source-Verbindungen? A: Es umgeht die gemeinsame Source-Induktivität.

- Die Gate-Schleife sieht den Spannungsabfall, der durch den Hauptlaststrom verursacht wird, nicht.

- Dies führt zu saubererem, schnellerem Schalten.

F: Wie überprüfe ich die Impedanzkontrolle auf Gate-Leiterbahnen? A: Verwenden Sie während des Designs einen Impedanzrechner.

- Definieren Sie den Lagenaufbau und die Dielektrizitätskonstante.

- Passen Sie die Leiterbahnbreite an die Zielimpedanz an (obwohl die Minimierung der Induktivität bei kurzen Läufen normalerweise Vorrang vor der Impedanzanpassung hat).

F: Wie lange ist die Lieferzeit für die Herstellung von SiC-tauglichen PCBs? A: Dies variiert je nach Komplexität und Materialverfügbarkeit.

- Standard High-Tg-Leiterplatten: 3-5 Tage.

- Schwerkupfer oder spezialisierte Substrate: 7-10 Tage.

Verwandte Seiten & Tools

Um Sie bei den Best Practices für SiC-Inverter-Gate-Treiber-PCBs weiter zu unterstützen, nutzen Sie diese Ressourcen:

- PCB-Impedanzrechner: Unerlässlich zur Berechnung von Leiterbahnbreite und -abstand zur Verwaltung von Induktivität und Impedanz.

- DFM-Richtlinien: Stellen Sie sicher, dass Ihr Layout die Fertigungsbeschränkungen erfüllt, um kostspielige Neukonstruktionen zu vermeiden.

- Angebot einholen: Bereit zur Fertigung? Laden Sie Ihre Gerber-Dateien für eine schnelle Kostenschätzung hoch.

Glossar (Schlüsselbegriffe)

| Begriff | Definition | Relevanz für SiC-PCB |

|---|---|---|

| :--- | :--- | :--- |

| SiC (Siliziumkarbid) | Ein Halbleitermaterial mit großer Bandlücke, das höhere Spannungen und schnelleres Schalten als Silizium ermöglicht. | Die Kerntechnologie, die spezielle PCB-Layout-Regeln erfordert. |

| dV/dt | Die Änderungsrate der Spannung in Bezug auf die Zeit. | Hohes dV/dt in SiC erzeugt Rauschen und erfordert Treiber mit hohem CMTI. |

| Parasitäre Induktivität | Unerwünschte Induktivität, die in Leiterbahnspuren und Bauteilanschlüssen inhärent ist. | Der Hauptfeind des schnellen Schaltens; verursacht Schwingungen und Überschwingen. |

| Miller-Effekt | Ein Phänomen, bei dem die Kapazität ($C_{gd}$) Spannung an das Gate koppelt und es potenziell einschaltet. | Erfordert eine negative Gate-Ansteuerung oder Miller-Klemmen im PCB-Design. |

| Kelvin-Verbindung | Eine 4-Leiter-Messtechnik, die beim PCB-Routing angewendet wird, um Strom- und Messpfade zu trennen. | Entscheidend für die Isolierung des Gate-Rückpfads von Hochstrom-Leistungspfaden. |

| CMTI | Gleichtakt-Transientenfestigkeit; die Fähigkeit eines Isolators, schnelle transiente Störungen zu unterdrücken. | Muss hoch sein (>100 kV/µs), um eine Treiberkorruption zu verhindern. |

| Entsättigung (Desat) | Eine Schutzmethode, die erkennt, ob der MOSFET in einem Kurzschlusszustand ist. | Erfordert eine sorgfältige Verlegung der Detektionsspuren, um Fehlauslösungen zu vermeiden. |

| Schleifenfläche | Die physikalische Fläche, die von einem Strompfad und seinem Rückweg umschlossen wird. | Muss minimiert werden, um EMI und Induktivität zu reduzieren. |

| Kriechstrecke | Der kürzeste Abstand zwischen zwei leitenden Teilen entlang der Oberfläche der Isolierung. | Entscheidend für die Hochspannungs-Sicherheitsisolation. |

| Luftstrecke | Der kürzeste Abstand zwischen zwei leitenden Teilen durch die Luft. | Verhindert Lichtbögen in Hochspannungsdesigns. |

| Gate-Widerstand ($R_g$) | Ein Widerstand, der in Reihe mit dem Gate geschaltet wird, um die Schaltgeschwindigkeit zu steuern und Schwingungen zu dämpfen. | Platzierung und Wertauswahl sind wichtige Abstimmungsparameter. |

| C0G/NP0 | Ein Typ von Keramikkondensator-Dielektrikum mit hoher Stabilität. | Empfohlen für Entkopplung und Timing in rauen thermischen Umgebungen. |

Fazit

Die Implementierung bewährter Verfahren für SiC-Inverter-Gate-Treiber-PCBs ist nicht nur das Abhaken einer Checkliste; es geht darum, die Physik der Hochgeschwindigkeits- und Hochspannungs-Schaltung zu respektieren. Durch die Minimierung der Schleifeninduktivität, die Gewährleistung einer robusten Isolation und die Auswahl der richtigen Materialien können Sie das volle Effizienzpotenzial der Siliziumkarbid-Technologie ausschöpfen, ohne die Zuverlässigkeit zu beeinträchtigen.

Egal, ob Sie einen neuen EV-Traktionswechselrichter prototypisieren oder eine industrielle Stromversorgung optimieren, das Layout ist die Grundlage Ihres Erfolgs. APTPCB ist auf die Herstellung von Hochleistungs-PCBs spezialisiert, die diesen strengen Anforderungen gerecht werden. Wenn Sie Ihr Design fertig haben oder Beratung bei der Materialauswahl für Ihr nächstes SiC-Projekt benötigen, kontaktieren Sie uns für eine Fertigungsbewertung.