Das Schablonendesign für Surface Mount Technology (SMT) ist der technische Prozess zur Festlegung von Aperturgeometrien, Foliendicke und Materialeigenschaften, um das genaue Volumen der auf eine Leiterplatte (PCB) aufgetragenen Lotpaste zu steuern. Dieser kritische Fertigungsschritt entscheidet über den Erfolg des Lötprozesses, denn etwa 60% bis 70% aller SMT-Bestückungsfehler entstehen durch falsche Druckparameter. Ein belastbares Design bringt die physikalischen Grenzen der Schablonenfolie mit den Benetzungsanforderungen elektronischer Bauteile in Einklang.

Zentrale Erkenntnisse

- Hauptfunktion: Die Schablone ist ein Werkzeug zur Volumenkontrolle; das aufgetragene Pastenvolumen entspricht der Aperturfläche multipliziert mit der Foliendicke.

- Kritische Kennzahl (Area Ratio): Das Area Ratio (AR) muss bei Standardprozessen ≥ 0,66 sein, damit sich die Paste aus der Schablone löst und nicht an den Wänden haften bleibt.

- Kritische Kennzahl (Aspect Ratio): Das Aspect Ratio (Breite/Dicke) muss ≥ 1,5 sein, um Verstopfungen zu vermeiden.

- Häufiges Missverständnis: Ein Verhältnis von Apertur zu Pad von 1:1 ist nur selten korrekt; die meisten Designs benötigen eine globale Reduzierung von 10% bis 20%, um Brückenbildung und Lotkugeln zu verhindern.

- Validierungstipp: Nutzen Sie Daten aus der Lotpasteninspektion (SPI), um während der First Article Inspection (FAI) zu prüfen, dass die Transfereffizienz über 80% liegt.

- Materialwahl: Edelstahl (SUS304) ist Industriestandard, aber Fine-Pitch-Designs (< 0,5mm) erfordern feinkörnigen Stahl oder elektrogeformte Nickelfolien.

- Entscheidungsregel: Wenn das Bauteilraster ≤ 0,4mm beträgt, müssen Sie eine Nanobeschichtung oder eine flussmittelabweisende Oberflächenbehandlung einsetzen, um die Druckschärfe zu erhalten.

Inhalt

- Was es wirklich bedeutet (Umfang und Grenzen)

- Wichtige Kennzahlen (wie man es bewertet)

- Wie man auswählt (Auswahlhilfe nach Szenario)

- Umsetzungsprüfpunkte (vom Design bis zur Fertigung)

- Häufige Fehler (und der richtige Ansatz)

- FAQ (Kosten, Lieferzeit, Materialien, Tests, Abnahmekriterien)

- Glossar (wichtige Begriffe)

- Fazit (nächste Schritte)

Was es wirklich bedeutet (Umfang und Grenzen)

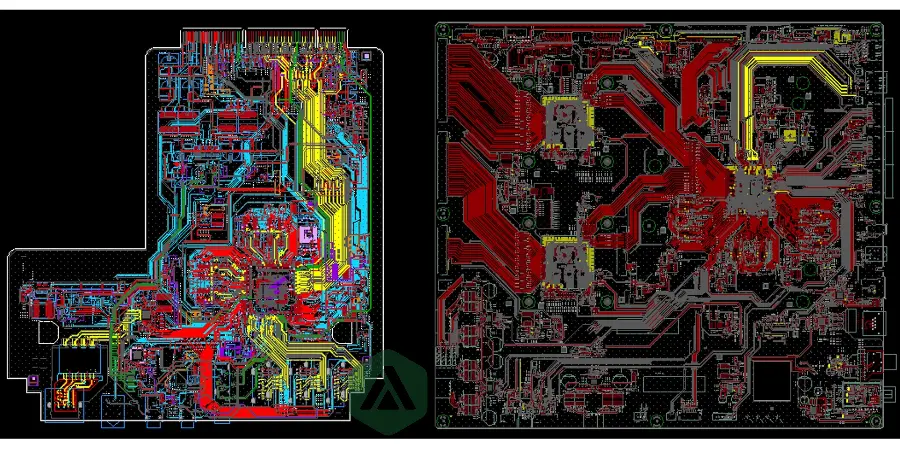

Ein SMT-Schablonendesign-Tutorial umfasst weit mehr als das Schneiden von Löchern in Metall. Es definiert das Zusammenspiel zwischen PCB-Pad, der Rheologie der Lotpaste und der Mechanik der Rakel. Zum Umfang des Schablonendesigns gehören die Auswahl der Aufspannmethode (gerahmt oder rahmenlos), der Fertigungstechnologie (Laserzuschnitt oder Elektroformung) sowie die spezifischen Aperturanpassungen für anspruchsvolle Bauteile wie Quad Flat No-leads (QFNs) oder Ball Grid Arrays (BGAs).

Die Grenzen dieses Prozesses werden durch die Fertigungsfähigkeit definiert. Ein Standard-Laser hat beispielsweise einen Strahldurchmesser von ungefähr 20µm bis 40µm. Diese physikalische Grenze bestimmt den minimalen Eckradius einer Apertur. Wenn ein Design schärfere Ecken verlangt, als der Laser schneiden kann, leidet die Pastenfreigabe. Außerdem muss das Design nachgelagerte Prozesse berücksichtigen. Wenn die Leiterplatte eine Mischbestückung erfordert, muss das Schablonendesign mit dem Selektivlöten-Design oder dem Leitfaden für Wellenlötvorrichtungen abgestimmt sein, damit keine Paste spätere Maskierung oder Vorrichtungen stört.

Ein korrektes Design stellt die „Transfereffizienz“ sicher, also den prozentualen Anteil des Pastenvolumens, der tatsächlich von der Apertur auf das Pad übertragen wird. Ein theoretisches Volumen von 100% wird selten erreicht; ein gut ausgelegter Prozess zielt auf eine Volumenübertragung von 80% bis 110%. Alles unter 70% führt typischerweise zu unzureichenden Lötstellen (Opens), während alles über 120% Kurzschlussrisiken durch Brückenbildung erzeugt.

Wichtige Kennzahlen (wie man es bewertet)

Um eine Fertigung mit hoher Ausbeute sicherzustellen, müssen Ingenieure bestimmte geometrische und prozessbezogene Kennzahlen bewerten. Diese Werte entscheiden darüber, ob eine Schablone physisch funktioniert oder direkt an der Linie scheitert.

Geometrie- und Designgrenzen

Die folgende Tabelle zeigt die harten Grenzen der Schablonengeometrie. Werden sie verletzt, ist in der Regel eine Änderung der Foliendicke oder der Aperturgröße erforderlich.

| Kennzahl | Standardgrenze | Grenze für hohe Zuverlässigkeit | Warum sie wichtig ist | Wie geprüft wird |

|---|---|---|---|---|

| Area Ratio (AR) | $\ge 0.66$ | $\ge 0.70$ | Bestimmt, ob die Paste aus der Apertur freikommt. | Berechnung: $Fläche / (Umfang \times Dicke)$. |

| Aspect Ratio | $\ge 1.5$ | $\ge 1.6$ | Verhindert, dass Paste in der Apertur stecken bleibt. | Berechnung: $Aperturbreite / Foliendicke$. |

| Wandrauheit | $< 5 \mu m$ | $< 3 \mu m$ | Raue Wände halten Paste zurück und senken die Transfereffizienz. | Mikroskopische Prüfung oder Profilometer. |

| Positionsgenauigkeit | $\pm 15 \mu m$ | $\pm 10 \mu m$ | Sorgt dafür, dass die Apertur exakt mit dem PCB-Pad ausgerichtet ist. | CMM-Scan (Koordinatenmessmaschine). |

| Folienspannung | $> 35 N/cm$ | $> 40 N/cm$ | Verhindert „Coining“ oder Verschmieren beim Ablösen. | Spannungsmessung an 5 Punkten. |

| Fiducial-Kontrast | Hoch | Hoch | Die Maschinenvision muss Ausrichtungsmarken sofort erkennen. | Sichtprüfung; Kontrolle der Dunkelheit bei Halbätzung. |

Prozess- und Leistungskennzahlen

Sobald die Schablone in der Druckmaschine ist, definieren diese Kennzahlen den Erfolg.

| Kennzahl | Akzeptabler Bereich | Kritischer Grenzwert | Warum sie wichtig ist | Wie geprüft wird |

|---|---|---|---|---|

| Transfereffizienz | 80% – 120% | $< 70%$ | Niedrige Effizienz verursacht Opens, hohe Effizienz erzeugt Shorts. | SPI-Inspektion (Volumenmessung). |

| Wischfrequenz | Alle 3–5 Drucke | Jeder Druck | Häufiges Reinigen reduziert den Durchsatz und weist auf schlechte Freigabe hin. | Zykluszeit und Druckfehler überwachen. |

| Pastenhöhe | Foliendicke $\pm 15%$ | $\pm 25%$ | Konstante Höhe belegt konstanten Druck und konstante Freigabe. | SPI-Höhenkarte. |

| Stegbreite | $\ge 150 \mu m$ | $< 100 \mu m$ | Dünne Stege zwischen Aperturen brechen leicht. | Design Rule Check (DRC) auf Gerberdaten. |

Wie man auswählt (Auswahlhilfe nach Szenario)

Die Auswahl der richtigen Schablonenparameter ist eine Reihe von Wenn-Dann-Entscheidungen auf Basis von Bauteildichte und PCB-Technologie. Verwenden Sie diese 10 Regeln als Leitfaden für Ihre Konfiguration.

- Wenn das kleinste Bauteilraster < 0,5mm ist (z. B. Fine-Pitch-BGA oder QFN), wählen Sie eine Foliendicke von 100µm (4 mil) oder 120µm (5 mil), um passende Area Ratios sicherzustellen.

- Wenn das Design Standard-1206/0805-Passive und ICs mit 1,27mm Raster enthält, wählen Sie eine Standardfolie von 127µm (5 mil) oder 150µm (6 mil) für robuste Lötstellen.

- Wenn das PCB große Steckverbinder mit hohem Volumenbedarf und Fine-Pitch-BGAs mit geringem Volumenbedarf kombiniert, wählen Sie eine Step-Stencil-Lösung (step-down für Fine Pitch oder step-up für Steckverbinder).

- Wenn das Bauteil ein QFN mit großem mittigem Massepad ist, wählen Sie ein Window-Pane-Aperturdesign mit 50% bis 80% Flächenabdeckung, um Aufschwimmen und Voids zu vermeiden.

- Wenn Sie eine Hochvolumenfertigung (> 50.000 Zyklen) fahren, wählen Sie eine Nanobeschichtung, um die Pastenfreigabe zu verbessern und die Unterseitenreinigung seltener zu machen.

- Wenn die Aperturbreite unter 0,25mm liegt, wählen Sie Elektropolieren als Nachbearbeitung, um die Aperturwände zu glätten und die Transfereffizienz zu steigern.

- Wenn Sie Prototypen fertigen und die Kosten minimieren müssen, wählen Sie ein rahmenloses System (nur Folie), das mit einem universellen Spannrahmen kompatibel ist (z. B. VectorGuard).

- Wenn die Leiterplatte 0201- oder 01005-Bauteile verwendet, wählen Sie Home Plate- oder Inverted Home Plate-Aperturformen, um Lotkugeln an den Bauteilflanken zu reduzieren.

- Wenn das PCB nachfolgend wellengelötet werden muss, wählen Sie Aperturreduzierungen, die Paste von Durchkontaktierungen fernhalten, damit die Lösung mit dem Leitfaden für Wellenlötvorrichtungen kompatibel bleibt.

- Wenn die Lebensdauer der Schablone 100.000 Drucke überschreiten muss, wählen Sie SUS304-H (High Tension) statt Standard-Edelstahl, um die Registriergenauigkeit über lange Laufzeit zu halten.

Umsetzungsprüfpunkte (vom Design bis zur Fertigung)

Folgen Sie diesem 10-Schritte-Ablauf, um von einem PCB-Layout zu einer serienreifen Schablone zu gelangen. Jeder Schritt enthält eine konkrete Abnahmeprüfung.

Pastenlage exportieren (Gerber/ODB++)

- Aktion: Erzeugen Sie die Pastenmaskenlage aus dem ECAD-System. Stellen Sie sicher, dass sie anfangs 1:1 den Kupferpads entspricht.

- Abnahmeprüfung: Prüfen Sie Dateiendung und stellen Sie sicher, dass keine nicht zur Paste gehörenden Elemente wie Board-Outline auf der Pastenlage liegen.

Globale Reduzierung anwenden

- Aktion: Wenden Sie eine globale Reduzierung von 10% bis 15% nach Fläche oder 0,05mm pro Seite an. Das kompensiert das Fließen der Paste beim Reflow.

- Abnahmeprüfung: Messen Sie ein Standard-0603-Pad; die Apertur muss kleiner als das Kupferpad sein.

Area Ratios (AR) berechnen

- Aktion: Führen Sie ein Skript oder eine manuelle Prüfung für die kleinsten Aperturen gegen die gewählte Foliendicke aus.

- Abnahmeprüfung: Alle AR-Werte müssen ≥ 0,66 sein. Wenn nicht, Foliendicke reduzieren oder Apertur vergrößern, sofern der Abstand es zulässt.

QFN-/Thermalpads optimieren

- Aktion: Segmentieren Sie große Thermalpads in ein Gitter (Window Pane). Die Stegbreite zwischen den Segmenten sollte ≥ 0,2mm sein.

- Abnahmeprüfung: Die gesamte Pastenabdeckung auf dem Thermalpad liegt zwischen 50% und 80%.

Für Fine Pitch anpassen (BGA/0201)

- Aktion: Ändern Sie die Aperturform bei BGAs zu „Squircle“ (Quadrat mit gerundeten Ecken) oder Kreisen. Für 0201 werden spezielle Reduzierungen angewendet, um Tombstoning zu vermeiden.

- Abnahmeprüfung: Der BGA-Aperturdurchmesser ist ≤ Pad-Durchmesser.

Fiducial-Marken platzieren

- Aktion: Fügen Sie halbgeätzte oder durchgeschnittene Fiducials hinzu. Diese müssen exakt zu den Fiducial-Positionen des PCB passen.

- Abnahmeprüfung: Es sind mindestens 3 Fiducials vorhanden (2 global, 1 lokal für Fine Pitch) und klar definiert.

Foliendicke und Material festlegen

- Aktion: Finalisieren Sie die Dicke (z. B. 127µm) basierend auf der AR-Prüfung. Geben Sie die Edelstahlgüte an.

- Abnahmeprüfung: Die gewählte Dicke ist in der Fertigungszeichnung aufgeführt.

Rahmen und Beschriftung definieren

- Aktion: Wählen Sie die Rahmengröße (z. B. 29" x 29") und fügen Sie Identifikationstext (Teilenummer, Dicke, Datum) am Schablonenrand hinzu.

- Abnahmeprüfung: Der Text befindet sich auf der Rakelseite, ist lesbar und stört den Druckbereich nicht.

Fertigung (Laserzuschnitt und Nachbearbeitung)

- Aktion: Senden Sie die Daten an einen PCB-Schablonenhersteller. Fordern Sie bei Bedarf Elektropolitur an.

- Abnahmeprüfung: Der Hersteller bestätigt Datenintegrität und die Fähigkeit, die geforderten Toleranzen zu schneiden.

Wareneingangsprüfung (IQC)

- Aktion: Nach Erhalt Spannung messen und kritische Aperturen prüfen.

- Abnahmeprüfung: Spannung > 35 N/cm; die Aperturgrößen stimmen innerhalb von ± 9µm mit den Gerberdaten überein.

Häufige Fehler (und der richtige Ansatz)

Selbst erfahrene Ingenieure tappen in diese Fallen. So lassen sie sich erkennen und korrigieren.

Fehler: 1:1-Skalierung der Apertur

- Auswirkung: Zu viel Lotpaste führt zu Brückenbildung und Lotkugeln, insbesondere bei Fine-Pitch-ICs.

- Korrektur: Wenden Sie eine globale Reduzierung von 10-20% nach Fläche an.

- Prüfung: Kontrollieren Sie im CAM-Viewer, dass die Apertur sichtbar kleiner als das Kupferpad ist.

Fehler: Aspect Ratio bei 0201 ignoriert

- Auswirkung: Paste verstopft die Apertur und wird nicht freigegeben, was Opens verursacht.

- Korrektur: Reduzieren Sie die Foliendicke auf 100µm oder vergrößern Sie die Apertur leicht, wenn der Abstand es zulässt.

- Prüfung: Berechnen Sie AR; stellen Sie sicher, dass der Wert > 0,66 ist.

Fehler: Übermäßige Reduzierung bei bleifreier Paste

- Auswirkung: Bleifreie Legierungen (SAC305) benetzen und verlaufen nicht so gut wie SnPb. Zu starke Reduzierung führt zu freiliegenden Kupferkanten.

- Korrektur: Verwenden Sie für bleifreie Prozesse auf großen Pads eine konservative Reduzierung (1:1 oder 5% Reduzierung).

- Prüfung: Kontrollieren Sie Reflow-Lötstellen auf vollständige Padabdeckung.

Fehler: Fehlende Freistellung für Lötstoppmaske

- Auswirkung: Wenn die Schablone auf dicker Lötstoppmaske oder Beschriftung aufliegt, entsteht ein „Dichtungsspalt“, der Pastenverschmierung verursacht.

- Korrektur: Stellen Sie sicher, dass der Schablonenbereich frei von erhabenen Markierungen ist, oder nutzen Sie eine Stufenfreistellung (geätzte Tasche) auf der PCB-Seite der Schablone.

- Prüfung: Prüfen Sie die PCB-Topografie gegen das Schablonenlayout.

Fehler: Falsche Step-Stencil-Konfiguration

- Auswirkung: Die Rakelklinge wird beschädigt oder druckt ungleichmäßig, wenn die „Stufe“ zu steil ist oder zu nah an Aperturen liegt.

- Korrektur: Halten Sie einen Keep-out-Abstand von 3mm bis 5mm rund um die Stufenkante ein.

- Prüfung: Messen Sie den Abstand von der Stufenkante zur nächstgelegenen Apertur.

Fehler: Klebeschablonen vernachlässigen

- Auswirkung: Für doppelseitiges Reflow oder Wellenlöten müssen Bauteile geklebt werden. Wird dafür ein Pastenschablonendesign verwendet, ist die Haftung unzureichend.

- Korrektur: Verwenden Sie spezielle Klebeaperturdesigns, häufig Schlüsselloch oder Doppelpunkte, mit größerer Höhe.

- Prüfung: Führen Sie vor dem Löten einen Scherversuch an den geklebten Bauteilen durch.

Fehler: Invertierte Lagen

- Auswirkung: Die Schablone wird gespiegelt geschnitten.

- Korrektur: Eindeutig beschriften

Glossar (wichtige Begriffe)

| Begriff | Bedeutung | Warum es in der Praxis wichtig ist |

|---|---|---|

| DFM | Design for Manufacturability: Layoutregeln, die Fehler reduzieren. | Verhindert Nacharbeit, Verzögerungen und versteckte Kosten. |

| AOI | Automatische optische Inspektion zur Erkennung von Löt- und Bestückungsfehlern. | Verbessert die Abdeckung und erkennt frühe Ausreißer. |

| ICT | In-Circuit-Test, der Netze auf Opens, Shorts und Werte prüft. | Schneller Strukturtest für Serienfertigung. |

| FCT | Functional Circuit Test, bei dem die Baugruppe eingeschaltet und funktional geprüft wird. | Validiert das reale Verhalten unter Last. |

| Flying Probe | Elektrischer Test ohne Fixture mit beweglichen Sonden auf Pads. | Gut für Prototypen sowie kleine und mittlere Stückzahlen. |

| Netlist | Verbindungsdefinition zum Vergleich von Design und gefertigtem PCB. | Erkennt Opens und Shorts vor der Montage. |

| Stackup | Lagenaufbau mit Kernen, Prepregs, Kupfergewichten und Dicke. | Bestimmt Impedanz, Verzug und Zuverlässigkeit. |

| Impedanz | Kontrolliertes Leiterbahnverhalten für Hochgeschwindigkeits- oder RF-Signale, z. B. 50Ω. | Vermeidet Reflexionen und Probleme der Signalintegrität. |

| ENIG | Oberfläche aus chemisch Nickel und Immersionsgold. | Vereint Lötbarkeit und Planarität; Nickeldicke im Blick behalten. |

| OSP | Organisches Oberflächenfinish zur Lötbarkeitserhaltung. | Kostengünstig, aber empfindlich bei Handhabung und mehreren Reflows. |

FAQ zum SMT-Schablonendesign-Tutorial

Was ist smt stencil design tutorial (in einem Satz)?

Es ist ein praxisnaher Satz aus Anforderungen und Prüfschritten, der definiert, wie das Produkt gebaut, verifiziert und abgenommen wird.

- Umfang und Grenzen klären.

- Pass-/Fail-Kriterien definieren.

- DFM und Testabdeckung aufeinander abstimmen.

Was kostet smt stencil design tutorial typischerweise?

Die Kosten hängen von Lagenzahl, Materialien, Oberfläche, Testmethode und dem Aufwand der technischen Prüfung ab.

- Mengen und Stackup früh bereitstellen.

- Impedanz, Via-in-Pad und Mikrovias klar angeben.

- Vor der Angebotserstellung DFM-Hinweise anfordern.

Wodurch wird die Lieferzeit für smt stencil design tutorial bestimmt?

Die Lieferzeit wird von Datenvollständigkeit, Materialverfügbarkeit und Test- bzw. Inspektionsanforderungen bestimmt.

- Fehlende Bohr- oder Stackup-Daten vermeiden.

- Materialsubstitutionen bestätigen.

- Panelisierung früh festlegen.

Welche Dateien sollte ich für smt stencil design tutorial senden?

Senden Sie Gerber/ODB++, NC-Drill-Daten, Stackup-Hinweise, Fertigungszeichnung und Testanforderungen.

- Version und Datum angeben.

- Impedanzziele und Toleranzen bereitstellen.

- Bei PCBA eine Stückliste beifügen.

Wie definiere ich Abnahmekriterien für smt stencil design tutorial?

Verwenden Sie messbare Kriterien, die an IPC-Klasse, elektrische Testabdeckung und funktionale Validierung gebunden sind.

- IPC-Klasse festlegen.

- E-Test bzw. Netlist spezifizieren.

- Funktionale Testfälle auflisten.

Welche Oberflächenbeschichtung ist für smt stencil design tutorial am besten?

Die Wahl hängt von Pitch- und Planaritätsanforderungen, Kostenzielen und Zuverlässigkeitsanforderungen ab.

- ENIG für Fine Pitch und BGA.

- OSP für kostensensitive Aufbauten.

- HASL bei sehr feinem Pitch vermeiden.

Wie viele Testpunkte brauche ich für smt stencil design tutorial?

Genug, um die Teststrategie aus Flying Probe, ICT oder FCT mit ausreichend Reserve zu unterstützen.

- Früh im Layout einplanen.

- Zugang von hohen Bauteilen fernhalten.

- Größe der Sondenpads dokumentieren.

Was sind die häufigsten Ausfälle bei smt stencil design tutorial?

Datenprobleme, unzureichende Testabdeckung und unkontrollierte Prozessgrenzen sind die häufigsten Ursachen.

- Auf Ringbreite und Registrierung achten.

- Lötstoppmaskenöffnungen kontrollieren.

- Impedanz und Verzug prüfen.

Fazit

smt stencil design tutorial lässt sich am einfachsten richtig umsetzen, wenn Sie Spezifikation und Verifikationsplan früh definieren und anschließend mit DFM und Testabdeckung absichern.

Nutzen Sie die oben stehenden Regeln, Prüfpunkte und Muster zur Fehlerbehebung, um Iterationsschleifen zu verkürzen und die Ausbeute bei steigenden Stückzahlen zu schützen.

Wenn Sie bei einer Randbedingung unsicher sind, validieren Sie sie mit einer kleinen Pilotserie, bevor Sie die Produktionsfreigabe festschreiben.