Wichtige Erkenntnisse

- Begriffsrahmen: Das PCB-Layout einer Dreiphasen-Invertersteuerung umfasst die physische Anordnung von Gate-Treibern, Mikrocontrollern und Messschaltungen bei gleichzeitig strikter Isolation zur Hochspannungs-Leistungsstufe.

- Kritische Kennzahl: Die Schleifeninduktivitaet im Gate-Ansteuerpfad ist der wichtigste Einzelfaktor fuer Schalteffizienz und elektromagnetische Stoerungen (EMI).

- Isolation ist Pflicht: Korrekte Kriech- und Luftstrecken zwischen Hochspannungsseite (DC-Link/IGBTs) und Niederspannungsseite (MCU/DSP) sind fuer die Sicherheit unverzichtbar.

- Thermisches Management: Auch Steuerplatinen brauchen thermische Strategien, insbesondere fuer Gate-Treiber-ICs mit grossen kapazitiven Lasten.

- Validierung: Simulation allein reicht nicht aus; Double-Pulse-Tests und Thermografie muessen das Layout physisch bestaetigen.

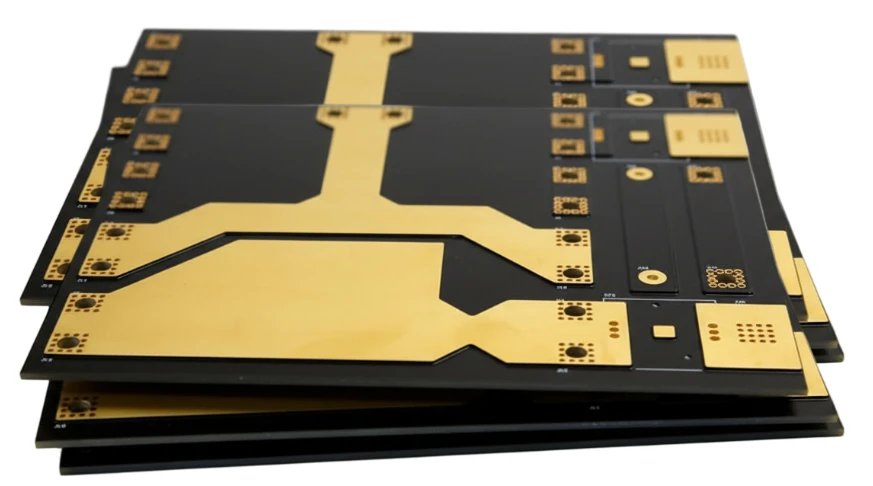

- Fertigungsreife: Design for Manufacturing (DFM) muss schwere Kupferaufbauten und stackup-symmetrische Lagenaufbauten beruecksichtigen, um Verzug zu vermeiden.

Was „Dreiphasen-Invertersteuerungs-PCB“ bedeutet (Umfang und Grenzen)

Der Begriff PCB-Layout fuer Dreiphasen-Invertersteuerungen beschreibt die spezielle Ingenieuraufgabe, die Leiterplatte zu entwerfen, welche das Schalten eines dreiphasigen Leistungsinverters steuert. Waehrend die Leistungsstufe den eigentlichen Strom verarbeitet, oft in Groessenordnungen von Hunderten Ampere, ist das Steuerlayout Gehirn und Nervensystem des Systems. Es wandelt digitale Logik, also PWM-Signale, in reale Gate-Ansteuerspannungen um und liest gleichzeitig analoge Rueckmeldungen zu Strom, Spannung und Temperatur ein.

Diese Layoutaufgabe ist deshalb besonders, weil sie an der Schnittstelle zwischen empfindlichen Digitalsignalen und aggressiven Hochspannungs-Schaltvorgaengen liegt. Ein schlechtes Layout fuehrt nicht nur zu einer nicht funktionierenden Platine. Es verursacht haeufig katastrophale Ausfaelle der Leistungsmodule durch Fehlansteuerung oder Spannungsspitzen.

Bei APTPCB (APTPCB PCB Factory) sehen wir regelmaessig Designs, die in der Simulation sauber arbeiten, in der Praxis aber an parasitaeren Induktivitaeten im PCB-Layout scheitern. Dieser Leitfaden betrachtet das Layout vom Ausgang des Mikrocontrollers (MCU), ueber die Isolationsbarriere, weiter zum Gate-Treiber und schliesslich bis zur Anbindung der Leistungsschalter wie IGBTs, MOSFETs oder SiC-/GaN-Bauteile.

Kennzahlen, die wirklich zaehlen (wie Qualitaet bewertet wird)

Ob ein PCB-Layout fuer Dreiphasen-Invertersteuerungen robust ist, zeigt sich an konkreten physikalischen und elektrischen Parametern. Diese Metriken markieren den Unterschied zwischen einem Prototypen und einer serienreifen Leiterplatte.

| Kennzahl | Warum sie wichtig ist | Typischer Bereich oder Einflussfaktoren | Wie man misst |

|---|---|---|---|

| Gate-Loop-Induktivitaet | Hohe Induktivitaet verursacht Klingeln, Ueberschwingen und langsamere Schaltvorgaenge. | Ziel: < 10 nH. Beeinflusst durch Leiterbahnlaenge und Naehe des Rueckstrompfads. | Q3D-Extractor-Simulation oder Beobachtung des V_ds-Ueberschwingens. |

| Common Mode Transient Immunity (CMTI) | Zeigt, ob der Isolator schnelle Spannungsanstiege (dV/dt) ohne Datenfehler uebersteht. | > 50 kV/µs fuer Si; > 100 kV/µs fuer SiC/GaN. | Pulsgenerator-Tests ueber die Isolationsbarriere. |

| Kriechstrecke | Verhindert elektrische Nachverfolgung ueber die PCB-Oberflaeche bei Feuchte und Verschmutzung. | Spannungsabhaengig, z. B. 8 mm bei 400-V-Systemen und Verschmutzungsgrad 2. | Physische Messung mit Messschieber oder CAD-Regelpruefung. |

| Luftstrecke | Verhindert Luftdurchschlag zwischen Hoch- und Niederspannungsnetzen. | Festgelegt durch IPC-2221 oder IEC 60664-1. | CAD-Design-Rule-Check (DRC). |

| Thermischer Widerstand (Rth) | Stellt sicher, dass Gate-Treiber und Regler bei hochfrequentem Schalten nicht ueberhitzen. | Abhaengig von Kupferdicke und thermischen Vias. | Thermografiekamera unter Last. |

| Signal-Rausch-Abstand (SNR) | Entscheidend fuer die Strommessrueckfuehrung zu ADC-Leitungen; Rauschen erzeugt Drehmomentwelligkeit im Motor. | Ziel: > 60 dB. Beeinflusst durch Trennung der Masseflaechen. | Oszilloskopanalyse der analogen Rueckfuehrleitungen. |

Designentscheidungen je nach Szenario (Zielkonflikte)

Verschiedene Anwendungen verlangen sehr unterschiedliche Ansaetze fuer das Design einer Dreiphasen-Invertersteuerungs-PCB. Nachfolgend stehen typische Szenarien und die jeweiligen Zielkonflikte.

1. Niederspannungs-Motorantriebe (12V - 48V)

- Kontext: Akkugeräte, E-Bikes, Robotik.

- Zielkonflikt: Platz ist die wichtigste Restriktion.

- Empfehlung: Leistung und Steuerung lassen sich oft auf einer einzigen Leiterplatte kombinieren. Nutzen Sie Heavy Copper PCB-Technologie, um hohe Stroeme auf kleiner Flaeche zu tragen. Die Isolationsanforderungen sind geringer, sodass Bauteile enger platziert werden koennen.

2. Industrielle AC-Antriebe (400V - 690V)

- Kontext: Fabrikautomation, Pumpen, Ventilatoren.

- Zielkonflikt: Zuverlaessigkeit und Sicherheit sind wichtiger als Baugroesse.

- Empfehlung: Strikte Einhaltung von IEC 61800-5-1. Nutzen Sie eine separate Steuerplatine, getrennt von der Leistungsstufe und verbunden ueber Steckerleisten oder Press-Fit-Pins. Breite Kriechstreckenschlitze sollten priorisiert werden.

3. Traktionsinverter fuer E-Fahrzeuge (hohe Leistungsdichte)

- Kontext: Hauptantrieb in Elektrofahrzeugen.

- Zielkonflikt: Hohe Vibration und extreme Temperaturwechsel.

- Empfehlung: Verwenden Sie Automotive-Materialien. Das Layout muss hohe dV/dt-Werte tragen, besonders bei SiC. Haeufig sind High Thermal PCB-Substrate oder Metallkern-Designs fuer die Treiberstufe noetig, damit die Waerme in das Kuehlsystem abgefuehrt wird.

4. Solarwechselrichter (netzgekoppelt)

- Kontext: PV-Energiewandlung.

- Zielkonflikt: Effizienz und lange Lebensdauer von ueber 20 Jahren.

- Empfehlung: Verluste in der Gate-Ansteuerung minimieren, um den Gesamtwirkungsgrad zu steigern. Das Layout muss hohe DC-Busspannungen bis 1500 V beruecksichtigen und braucht entsprechend breite Isolationsbarrieren sowie moeglicherweise Schutzlack.

5. Hochfrequenz-GaN-/SiC-Treiber

- Kontext: Servernetzteile, kompakte Ladegeraete.

- Zielkonflikt: Extrem hohe Schaltgeschwindigkeit gegenueber EMI.

- Empfehlung: Die Schleifeninduktivitaet muss praktisch null sein. Der Treiber muss physisch so nah wie moeglich am Schalter sitzen. Hauefig sind HDI-Techniken erforderlich, um Treiber direkt unter oder ueber dem Schalter zu platzieren.

6. Kostensensitive Haushaltsgeraete

- Kontext: Waschmaschinen, HVAC-Systeme.

- Zielkonflikt: Kosten gegen Performance.

- Empfehlung: Ein- oder zweilagige Leiterplatten sind zur Kostensenkung ueblich. Das erschwert Rueckstrompfade stark. Entwickler muessen Sternmasse-Konzepte sehr sauber umsetzen, um Stoerungskopplung auch ohne vollflaechige Ground-Planes zu begrenzen.

Implementierungs-Checkpoints (vom Design zur Fertigung)

Der Weg vom Schaltplan zur realen Leiterplatte verlangt einen disziplinierten Ablauf. Nutzen Sie diese Checkliste, um sicherzustellen, dass Ihr PCB-Layout fuer Dreiphasen-Invertersteuerungen bei APTPCB produktionsbereit ist.

Stackup-Definition:

- Empfehlung: Fuer Industrieinverter mindestens 4 Lagen verwenden (Signal-Ground-Power-Signal).

- Risiko: Zweilagige Leiterplatten fallen wegen unterbrochener Rueckstrompfade oft bei EMI-Tests durch.

- Akzeptanz: Impedanzprofile und Lagensymmetrie verifizieren.

Platzierung der Gate-Treiber:

- Empfehlung: Treiber innerhalb von 10 mm zu den Pins des Leistungsmoduls oder zu den MOSFET-Gates platzieren.

- Risiko: Lange Leiterbahnen wirken wie Antennen und erhoehen die Induktivitaet.

- Akzeptanz: Abstand visuell pruefen.

Kelvin-Anschluss fuer die Strommessung:

- Empfehlung: Differentielle Paare fuer Strommessshunts eng beieinander fuehren.

- Risiko: Eingekoppeltes Schaltstoerrauschen im Feedback-Loop fuehrt zu Reglerinstabilitaet.

- Akzeptanz: Differentielle Fuehrung im CAD ueberpruefen.

Breite der Isolationsbarriere:

- Empfehlung: Unter Optokopplern oder digitalen Isolatoren bei Spannungen ueber 400 V einen mechanischen Schlitz fraesen.

- Risiko: Carbonisierung der Leiterplatte ueber die Zeit mit anschliessendem Kurzschluss.

- Akzeptanz: Gerberdaten auf Fraeslayer pruefen.

Routing der Desaturation-Protection:

- Empfehlung: Die DESAT-Leitung kurz halten und von Knoten mit hohem dV/dt fernfuehren.

- Risiko: Falschausloesung des Kurzschlussschutzes.

- Akzeptanz: Stoerungskopplung am DESAT-Pin in der Simulation pruefen.

Trennung der Ground-Planes:

- Empfehlung: AGND, DGND und PGND klar trennen und nur an einem definierten Punkt, etwa per Net Tie, verbinden.

- Risiko: Masseschleifen koppeln Leistungstoerungen in die MCU ein.

- Akzeptanz: Ground-Netze im CAD hervorheben und Trennung pruefen.

Versorgungsentkopplung:

- Empfehlung: Low-ESR-Kondensatoren direkt an den Versorgungspins des Gate-Treibers platzieren.

- Risiko: Spannungseinbruch waehrend des Gate-Ladestrom-Spikes.

- Akzeptanz: Verifizieren, dass Kondensatoren wenn moeglich auf derselben Lage wie der IC liegen.

DFM-Review:

- Empfehlung: Daten vor der Bestellung fuer einen DFM Guideline-Check einreichen.

- Risiko: Nicht fertigbare Bohrtreffer oder Acid Traps.

- Akzeptanz: Freigabereport des Lieferanten.

Haeufige Fehler (und wie es richtig gemacht wird)

Auch erfahrene Ingenieure machen Fehler beim PCB-Design fuer Dreiphasen-Invertersteuerungen. Dies sind die Probleme, die wir am haeufigsten sehen.

- Fehler: Gate-Drive-Leitungen werden durch Vias gefuehrt.

- Korrektur: Vias erhoehen die Induktivitaet um etwa 1,2 nH pro Via. Den hochstromigen Gate-Lade- und Entladepfad nach Moeglichkeit auf der Top-Lage ohne Lagenwechsel fuehren.

- Fehler: Der Miller-Clamp-Pfad wird ignoriert.

- Korrektur: Der Pfad, der Fehleinschalten durch den Miller-Effekt verhindert, ist genauso kritisch wie der Einschaltpfad. Daher kurz und breit auslegen.

- Fehler: Der Temperatursensor sitzt weit weg vom Hotspot.

- Korrektur: NTC-/PTC-Sensoren muessen thermisch an das IGBT-/MOSFET-Gehäuse oder an die heisseste Stelle der Leiterplatte gekoppelt sein, nicht nur irgendwo in der Naehe.

- Fehler: Kupferbalance wird uebersehen.

- Korrektur: Grosse Kupferflaechen auf einer Seite und spaerliche Leiterbahnen auf der anderen Seite verziehen die Platine im Reflow. Kupfer-Patterning oder Thieving nutzen, um die Lagen auszugleichen.

- Fehler: Empfindliche Signale werden unter dem Leistungsmodul geroutet.

- Korrektur: ADC- oder Kommunikationsleitungen niemals direkt unter schaltenden Leistungshalbleitern verlegen. Kapazitive Kopplung injiziert dort Stoerungen.

- Fehler: Unzureichende Siebdruckkennzeichnung.

- Korrektur: Hochspannungsbereiche klar markieren. Das ist eine Sicherheitsanforderung fuer Montage- und Testpersonal.

FAQ

F: Wie viele Lagen sind fuer eine Dreiphasen-Invertersteuerungs-PCB sinnvoll? A: Fuer einfache Niederspannungsantriebe koennen 2 Lagen ausreichen. Bei industriellen 400-V-plus-Antrieben sind 4 Lagen Standard, um solide Ground-Planes bereitzustellen. Komplexe EV-Inverter verwenden oft 6 oder mehr Lagen.

F: Sollte unter dem Isolationstransformator oder Isolationskoppler eine Ground-Plane liegen? A: Auf keinen Fall. Unter den Isolationsbarriere-Bauteilen muss auf allen Lagen Kupfer entfernt werden, damit Kriech- und Luftstrecken eingehalten werden.

F: Welches Kupfergewicht sollte ich spezifizieren? A: Fuer reine Steuersignale reicht 1 oz (35µm) normalerweise aus. Wenn die Leiterplatte jedoch auch Hauptstrom fuehrt, koennen Industrial Control PCB-Standards mit 2 oz oder 3 oz Kupfer erforderlich sein.

F: Wie reduziere ich EMI im Layout? A: Die Schleifenflaeche aller Pfade mit hohem di/dt moeglichst klein halten, insbesondere Gate-Drive-Loops und DC-Link-Loops. Fuer die Steuerlogik eine durchgehende Ground-Plane nutzen. Wenn die Effizienzvorgaben es zulassen, koennen Gate-Widerstaende die Flanken verlangsamen.

F: Kann ich FR4 fuer Hochspannungsinverter verwenden? A: Ja, Standard-FR4 eignet sich fuer die meisten industriellen Inverter bis 1000 V, sofern das Layout die Kriechstreckenregeln einhaelt. Bei sehr hohen Dauertemperaturen ueber 130°C ist High-Tg-FR4 empfehlenswert.

F: Wie teste ich das Layout am besten vor dem Volllastbetrieb? A: Zuerst einen Double-Pulse-Test bei niedrigeren Spannungen durchfuehren. So lassen sich Schaltverhalten und Gate-Drive-Ringing pruefen, ohne die gesamte Leistungsstufe zu riskieren.

Verwandte Seiten und Tools

- Heavy Copper PCB: Wichtig fuer Inverter, bei denen die Steuerplatine zugleich nennenswerte Leistungsverteilung traegt.

- Industrial Control PCB: Spezifische Fertigungsmoeglichkeiten fuer robuste und hochzuverlaessige Industrieantriebselektronik.

- DFM Guidelines: Pruefen Sie Ihr Layout vor Abgabe gegen Fertigungsrestriktionen.

- Power & Energy PCB: Loesungen fuer Solar-, Wind- und netzgekoppelte Inverteranwendungen.

Glossar (wichtige Begriffe)

| Begriff | Definition |

|---|---|

| DC Link | Die Gleichspannungsquelle beziehungsweise Kondensatorbank, die den Inverter speist. |

| IGBT | Insulated Gate Bipolar Transistor. Ein gaengiger Leistungsschalter fuer Hochspannungsinverter. |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor. Ueblich bei Inverteranwendungen mit niedrigerer Spannung oder hoeherer Frequenz. |

| Gate Driver | Ein IC, das Logiksignale kleiner Leistung zu hochstromigen Impulsen verstaerkt, um IGBT- oder MOSFET-Gates anzusteuern. |

| Dead Time | Eine kurze Pause zwischen dem Abschalten des einen und dem Einschalten des anderen Transistors im selben Zweig, um Kurzschluesse zu vermeiden. |

| PWM | Pulse Width Modulation. Verfahren zur Kodierung analoger Signalpegel in digitale Impulse. |

| dV/dt | Die Aenderungsrate der Spannung. Hohes dV/dt kann Stoerungskopplung ueber Isolationsbarrieren ausloesen. |

| dI/dt | Die Aenderungsrate des Stroms. Hohes dI/dt erzeugt Spannungsspitzen ueber parasitaeren Induktivitaeten. |

| Kelvin-Anschluss | Vierleiter-Messmethode zur Spannungsmessung ueber einem Bauteil, etwa einem Shunt, ohne den Spannungsabfall der stromfuehrenden Leitungen mitzumessen. |

| Kriechstrecke | Der kuerzeste Weg zwischen zwei leitfaehigen Teilen entlang der Oberflaeche der Isolation. |

| Luftstrecke | Der kuerzeste Abstand zwischen zwei leitfaehigen Teilen durch die Luft. |

| EMI | Electromagnetic Interference. Stoerrauschen aus Schaltvorgaengen, das andere Elektronik beeinflusst. |

| EMC | Electromagnetic Compatibility. Die Faehigkeit eines Geraets, ohne Stoerung anderer Elektronik und ohne Beeintraechtigung durch EMI zu arbeiten. |

Fazit (naechste Schritte)

Das Beherrschen des PCB-Layouts fuer Dreiphasen-Invertersteuerungen ist eine Balance aus Elektrotechnik, Sicherheitsnormen und realen Fertigungsgrenzen. Ein gutes Layout schuetzt das empfindliche digitale Gehirn vor der Kraft der Leistungselektronik und sichert damit Effizienz sowie Zuverlaessigkeit.

Wenn Sie vom Design zum Prototyp uebergehen wollen, unterstuetzt APTPCB Sie dabei. Fuer ein praezises Angebot und ein umfassendes DFM-Review sollten Sie bitte Folgendes bereitstellen:

- Gerber-Dateien im RS-274X-Format.

- Stackup-Details wie Kupfergewicht und Dielektrikdicke.

- Materialspezifikationen wie Tg-Bewertung und CTI-Wert fuer Hochspannung.

- Spezielle Anforderungen wie Fraesen fuer Isolationsschlitze, schwere Kupferaufbauten oder bestimmte Loetstoppmaskenfarben fuer besseren Kontrast.

Wenn diese Angaben klar vorliegen, verlaeuft die Fertigung schneller und wir koennen eine Leiterplatte liefern, die den harten Anforderungen der Leistungselektronik gerecht wird.