Die Einführung der Via-in-Pad-Technologie (VIP) ist oft keine Kür, sondern eine zwingende Folge hoher Bauteildichte, insbesondere wenn Ball-Grid-Array-(BGA-)Pitches unter 0,5 mm fallen. Diese Technik nutzt die Leiterplattenfläche optimal aus und verbessert das Wärmemanagement, bringt aber zusätzliche Schritte beim Füllen und Beschichten mit sich, die ohne enge Prozessführung die Bestückungsausbeute gefährden. Dieser Leitfaden zeigt Einkaufs- und Entwicklungsteams, welche Spezifikationen, Risikomaßnahmen und Abnahmekriterien nötig sind, um zuverlässige VIP-Platinen ohne Fertigungsverzug zu beschaffen.

Highlights

- Kernnutzen: Ermöglicht das Routing für Fine-Pitch-BGAs (< 0,5 mm) und reduziert die Induktivität.

- Kritische Spezifikation: Die Dicke der Deckplattierung muss kontrolliert werden, typischerweise 12 bis 15 µm, damit die Oberfläche plan bleibt.

- Hauptrisiko: "Dimpling" oder Hohlräume in der Via-Füllung, die während der Montage zu Ausfällen der Lötverbindung führen.

- Validierung: Erfordert IPC-Class-3-konforme Mikroschliffe, um Wrap Plating und Füllintegrität zu prüfen.

Wichtige Erkenntnisse

- Kernnutzen: Ermöglicht das Routing für Fine-Pitch-BGAs (< 0,5 mm) und reduziert die Induktivität.

- Kritische Spezifikation: Die Dicke der Deckplattierung muss kontrolliert werden, typischerweise 12 bis 15 µm, damit die Oberfläche plan bleibt.

- Hauptrisiko: "Dimpling" oder Hohlräume in der Via-Füllung, die während der Montage zu Ausfällen der Lötverbindung führen.

- Validierung: Erfordert IPC-Class-3-konforme Mikroschliffe, um Wrap Plating und Füllintegrität zu prüfen.

- Einsatzbereich, Entscheidungskontext und Erfolgskriterien

- Fertigungskapazitäten und Bestelllogistik

- Spezifikationen, die vorab festgelegt werden müssen

Inhalt

- Einsatzbereich, Entscheidungskontext und Erfolgskriterien

- Fertigungskapazitäten und Bestelllogistik

- Spezifikationen, die vorab festgelegt werden müssen

- Wesentliche Risiken

- Validierung und Abnahme

- Checkliste zur Lieferantenqualifizierung

- Auswahlkriterien und Entscheidungsregeln

- FAQ

Einsatzbereich, Entscheidungskontext und Erfolgskriterien

Bei der Via-in-Pad-Fertigung wird ein metallisiertes Durchgangsloch (PTH) direkt in die Anschlussfläche eines Bauteils gesetzt, anschließend mit Epoxid gefüllt und überplattiert ("capped"), sodass eine plane, lötbare Oberfläche entsteht. Dieses Verfahren wird häufig als VIPPO (Via-in-Pad Plated Over) bezeichnet und unterscheidet sich klar von herkömmlich tented Vias.

Wann VIP eingesetzt werden sollte

Typischerweise wird VIP erforderlich, wenn:

- BGA-Pitch: Der Pitch des Bauteils 0,5 mm oder kleiner ist und für ein Dog-Bone-Fanout nicht genug Platz bleibt.

- Thermische Anforderungen: Leistungsstarke Bauteile direkte Wärmewege zu Innenlagen benötigen, also thermische Vias.

- Hochgeschwindigkeitssignale: Kurze Stubs und geringe Induktivität für die Signalintegrität entscheidend sind.

Erfolgskriterien

Ein VIP-Projekt ist nur dann erfolgreich, wenn die gefertigten Leiterplatten drei messbare Ziele erfüllen:

- Oberflächenplanarität: Die "Dimple"-Vertiefung über dem gefüllten Via darf 15 µm (Klasse 3) bzw. 25 µm (Klasse 2) nicht überschreiten, damit unter BGAs keine Hohlstellen entstehen.

- Integrität der Plattierung: Die Deckplattierung darf sich beim Reflow bei 260°C nicht von der darunterliegenden Via-Metallisierung oder dem Füllmaterial lösen.

- Vollständigkeit der Füllung: Hohlräume im Epoxidfüllstoff müssen unter 5 % des Via-Volumens bleiben, damit weder Ausgasung noch "Popcorning" auftreten.

Grenzfälle, in denen VIP ungeeignet ist

- Kostendruck: VIP erhöht die Kosten der nackten Leiterplatte wegen zusätzlicher Bohr-, Beschichtungs- und Planarisierungsschritte um 15 bis 25 %. Wenn Standard-Dog-Bone-Routing funktioniert, sollte man VIP vermeiden.

- Bauteile mit großem Pitch: Bei Pitchs > 0,65 mm reichen offene Standard-Vias meist aus und bergen weniger Risiko.

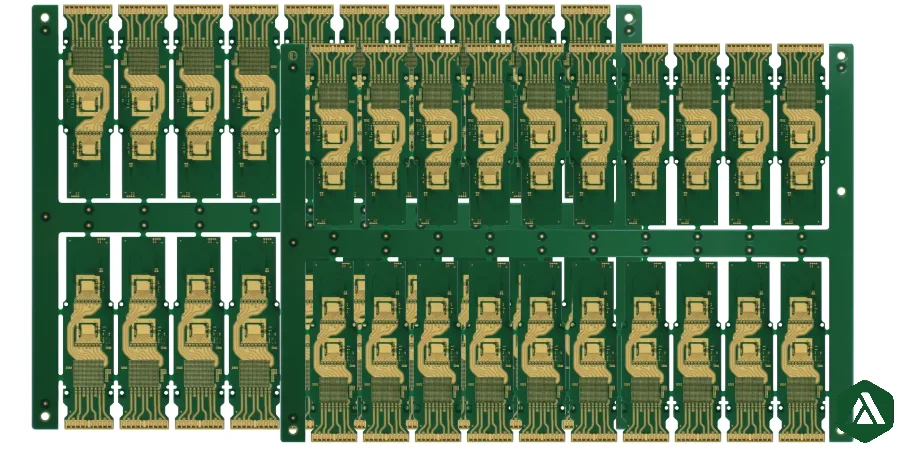

Fertigungskapazitäten und Bestelllogistik

Bevor das Design final freigegeben wird, muss geprüft werden, ob die Fähigkeiten des Herstellers zur geforderten Integrationsdichte passen. Via-in-Pad-Fertigung setzt spezielle Vakuumfüllanlagen und Ausrüstung zur Planarisierung voraus.

Überblick über typische Fähigkeiten

Die folgende Tabelle zeigt Standard- und fortgeschrittene Fähigkeiten für die VIP-Produktion.

| Parameter | Standardfähigkeit | Erweiterte Fähigkeit | Hinweise |

|---|---|---|---|

| Min. mechanischer Bohrdurchmesser | 0,20 mm (8 mil) | 0,15 mm (6 mil) | Kleinere Bohrer erschweren die Metallisierung. |

| Max. Aspect Ratio | 8:1 | 10:1 | Verhältnis von Plattendicke zu Bohrdurchmesser. |

| Pad-Durchmesser außen | Bohrung + 0,25 mm | Bohrung + 0,20 mm | Kritisch für ausreichenden Annular Ring. |

| Füllmaterial | Nichtleitendes Epoxid | Leitfähige Paste / Kupferpaste | Für CTE-Anpassung ist nichtleitendes Material meist besser. |

| Dicke der Deckplattierung | 12 µm | > 25 µm | Dickere Deckschichten verbessern die Ebenheit, kosten aber Zeit. |

| Dimple-Tiefe | < 25 µm | < 15 µm | Entscheidend für Fine-Pitch-BGA-Montage. |

| Wrap Plating | Klasse 2 (> 12 µm) | Klasse 3 (> 25 µm) | Zentral für die Zuverlässigkeit der Verbindung. |

| Lagenzahl | 4 bis 12 Lagen | 14 bis 30+ Lagen | Höhere Lagenzahlen erfordern strengere Registrierung. |

| Oberflächenfinish | ENIG, OSP | ENEPIG, Hartgold | ENIG ist Standard für plane Pads. |

| Blind/Buried Vias | Unterstützt | Gestapelte Microvias | VIP wird oft mit HDI-Strukturen kombiniert. |

Lieferzeit und MOQ

VIP fügt Prozessschritte wie Füllen, Backen, Planarisieren und Überplattieren hinzu, was die übliche Lieferzeit verlängert.

| Auftragsart | Typische Lieferzeit | MOQ | Haupttreiber |

|---|---|---|---|

| Prototyp (NPI) | 5 bis 8 Tage | 5 Panels | Zusätzliche Beschichtungszyklen und Aushärtezeiten verhindern echten 24h-Quick-Turn. |

| Kleinserie | 10 bis 12 Tage | 10 bis 50 Panels | Einrichtung der Vakuumfüllung und Verifikation per Schliffbild. |

| Serienproduktion | 15 bis 20 Tage | > 50 m² | Losgrößenoptimierung und Kapazitätsplanung. |

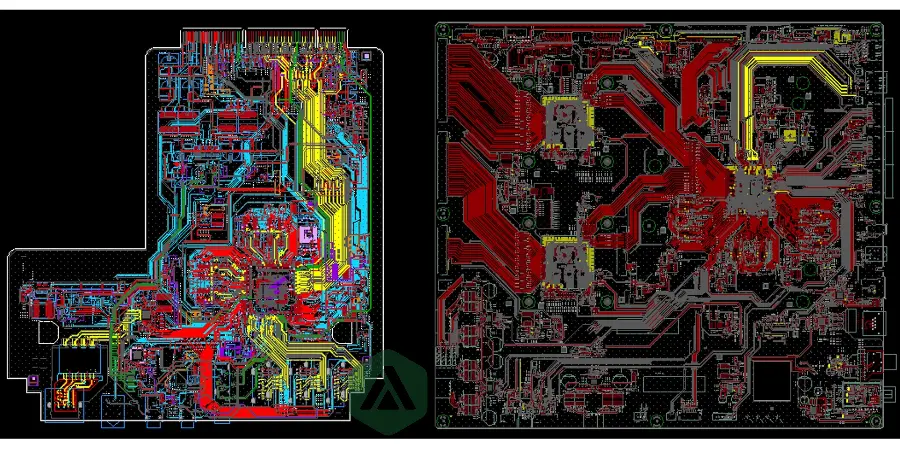

Spezifikationen, die vorab festgelegt werden müssen

Unklare Datenpakete sind die häufigste Ursache für VIP-Fehler. Die Via-Struktur muss in den Fertigungshinweisen und Gerber-Daten ausdrücklich definiert werden. Verlassen Sie sich nicht darauf, dass der Hersteller errät, welche Vias gefüllt werden sollen.

Tabelle der kritischen Parameter

Diese Werte gehören in die Fertigungszeichnung:

| Parameter | Empfohlener Bereich | Warum das wichtig ist |

|---|---|---|

| Via-Typ | IPC-4761 Type VII | Definiert gefüllte und überplattierte Vias, also VIPPO. |

| Bohrdurchmesser | 0,15 mm bis 0,25 mm | Große Vias (> 0,3 mm) lassen sich schwer ohne Einsacken oder Dimpling füllen. |

| Füllmaterial | Nichtleitendes Epoxid, z. B. Taiyo THP-100 | Passt im CTE besser zu FR4 als leitfähige Pasten und reduziert Spannungen. |

| Wrap Plating | Min. 25 µm (Klasse 3) | Verhindert Risse im Via-Knie bei thermischer Ausdehnung. |

| Deckplattierung | 12 µm bis 15 µm | Liefert genug Kupfer für das Löten, ohne Strukturen zu überplattieren. |

| Annular Ring | Min. 0,076 mm (3 mil) | Fängt Bohrversatz auf und ist wichtig für IPC-Klasse-2-Konformität. |

| Clearance | 0,15 mm | Abstand vom Via-Pad zum nächsten Kupfermerkmal. |

| Lötstoppmaske | LPI (Liquid Photoimageable) | Darf nicht in das überplattierte Pad hineinragen, also 1:1-Öffnung oder definierter Abstand. |

Detaillierte Anforderungsliste

- Dateikennzeichnung: Erstellen Sie eine separate Bohrdatei oder einen eigenen Layer nur für VIP-Bohrungen. Benennen Sie diese Datei eindeutig, zum Beispiel

Drill_VIP_Filled.drl. - Grenze für Aspect Ratio: Halten Sie das Verhältnis von Plattendicke zu Bohrdurchmesser unter 10:1. Oberhalb von 10:1 wird es schwierig, die Barrelmitte vollständig zu metallisieren und ohne Hohlräume zu füllen.

- Etch Compensation Planning: Geben Sie das fertige Kupfergewicht ausdrücklich an. Der Hersteller muss Etch Compensation Planning anwenden, meist mit einer Vergrößerung der Strukturen um 12 bis 25 µm, um die zusätzlichen Ätzzyklen des VIP-Prozesses auszugleichen.

- Material-Tg: Verwenden Sie High-Tg-Materialien mit Tg > 170°C für VIP-Leiterplatten. Die zusätzlichen thermischen Belastungen beim Einbrennen des Füllmaterials beanspruchen das Laminat.

- Planaritätsspezifikation: Fordern Sie explizit: "Pad flatness to be within 0.001 inch (25 µm) across the BGA array."

Wesentliche Risiken

Via-in-Pad-Fertigung bringt Fehlermodi mit sich, die bei Standard-PCBs nicht auftreten. Wer diese Risiken versteht, kann den Prozess des Lieferanten deutlich wirksamer auditieren.

1. Dimpling (der "Divot"-Effekt)

- Ursache: Das Epoxid schrumpft beim Aushärten oder bei der Planarisierung wird zu viel Kupfer von der Deckschicht abgetragen.

- Numerischer Grenzwert: Eine Tiefe von > 25 µm ist für die meisten Fine-Pitch-BGAs ein Ausfallkriterium.

- Früherkennung: 3D-Profilometrie oder Mikroschliffe an Testcoupons.

- Prävention: Zweistufige Füllprozesse verwenden, die Planarisierung sauber kalibrieren und eine Mindestdicke der Deckplattierung vorgeben.

2. Hohlräume in der Via-Füllung

- Ursache: Luft wird beim Füllprozess im Barrel eingeschlossen, oft wegen hoher Aspect Ratio oder ungeeignetem Vakuumdruck.

- Numerischer Grenzwert: Hohlräume > 5 % des Via-Volumens oder jede Leerstelle, die bis an die Barrelwand reicht.

- Früherkennung: Röntgenprüfung der Produktionspanels, 2D oder 3D.

- Prävention: Bei Aspect Ratios > 6:1 Vakuumfülltechnik fordern, nicht Siebdruck.

3. Ablösung des Wrap Plating

- Ursache: Schlechte Haftung zwischen dem initialen chemischen Kupfer und der nachfolgenden Umplattierung oder thermischer Schock.

- Numerischer Grenzwert: 0 % Ablösung bei 1000facher Vergrößerung zulässig.

- Früherkennung: Thermal-Stress-Test, etwa Solder Float, anschließend Mikroschliff.

- Prävention: Sicherstellen, dass der Lieferant vor dem Beschichten ordnungsgemäß desmear und Oberflächenaktivierung durchführt.

4. Barrel Cracks (Eckrisse)

- Ursache: CTE-Mismatch zwischen Epoxidfüllung (CTE ~30 bis 60 ppm) und Kupferbarrel (CTE ~17 ppm) während des Reflow-Prozesses.

- Numerischer Grenzwert: Keine Risse, die sich um mehr als 10 % durch die Plattierungswand erstrecken.

- Früherkennung: Interconnect Stress Testing (IST) oder Coupon-Tests mit thermischem Zyklus.

- Prävention: Nichtleitende Füllung mit besser passendem CTE einsetzen statt leitfähiger Füllung, die hier thermisch oft sogar ungünstiger ist.

Validierung und Abnahme

Die Qualität von Via-in-Pad lässt sich nicht durch eine einfache Sichtprüfung absichern. Notwendig sind klar vorgegebene zerstörende und zerstörungsfreie Prüfungen.

Tabelle der Abnahmekriterien

| Prüfpunkt | Methode | Abnahmekriterium | Stichprobenrate |

|---|---|---|---|

| Mikroschliff (Querschliff) | IPC-TM-650 2.1.1 | Wrap Plating > 25 µm (Klasse 3), keine Ablösung, Deckplattierung > 12 µm | 1 pro Los / Panel |

| Lötbarkeit | J-STD-003 | 95 % Benetzung, keine Entnetzung auf überplattierten Pads | 2 Coupons pro Los |

| Planaritätsprüfung | Laserprofilometrie / Mikroskop | Dimple-Tiefe < 25 µm oder < 15 µm, falls so spezifiziert | 5 Messpunkte pro Panel |

| Hohlraumprüfung | Röntgen | Keine Hohlräume > 5 % Volumen, keine Hohlräume im Lochzentrum | AQL 1.0 |

| Thermal Stress | IPC-TM-650 2.6.8 | Keine Ablösungen, Blasen oder Barrel-Risse nach 6x Reflow-Simulation | 1 Coupon pro Los |

| Oberflächenprüfung | AOI Data Analytics | Automatischer Nachweis von Deckschichtpräsenz und konstantem Paddurchmesser | 100 % der Panels |

Die Rolle von AOI Data Analytics

Moderne Hersteller nutzen AOI Data Analytics nicht nur zum Erkennen von Kurzschlüssen und Unterbrechungen, sondern auch zur Messung der Gleichmäßigkeit überplattierter Paddurchmesser. Wenn die Planarisierung zu aggressiv ist, kann sich der Annular Ring des gecappten Vias verkleinern. Diese Daten helfen dabei, eine Drift des Loses außerhalb der Toleranz frühzeitig zu erkennen.

Checkliste zur Lieferantenqualifizierung

Wenn Sie einen Lieferanten für die Via-in-Pad-Fertigung freigeben, sollte diese Checkliste sicherstellen, dass Equipment und Prozessfähigkeit wirklich vorhanden sind.

Ausrüstung und Prozess

- Vakuumfüllanlage: Gibt es eine dedizierte Vakuumfüllmaschine für Via-Plugging, etwa von ITC oder Mass? Siebdruck ist nur bei niedriger Aspect Ratio vertretbar.

- Planarisierungslinie: Verfügt der Lieferant über Keramikbürsten oder eine CMP-Linie, um überschüssiges Füllmaterial und Kupfer abzutragen?

- Galvaniklinien: Können die Anlagen mit Pulsplattierung arbeiten, was bei hoher Aspect Ratio die Throwing Power verbessert?

- Röntgenkapazität: Gibt es eine Inhouse-Röntgenprüfung zur Detektion von Hohlräumen?

Qualität und Rückverfolgbarkeit

- IPC-Klasseneinhaltung: Kann der Lieferant VIPPO-Merkmale nach IPC-6012 Class 3 zertifizieren?

- Schliffberichte: Wird zu jeder Lieferung ein Mikroschliffbericht bereitgestellt, der speziell die Schnittstelle zwischen Via-Füllung und Deckschicht zeigt?

- Materialkontrolle: Ist das definierte Füllmaterial, zum Beispiel Taiyo THP-100 oder ein freigegebenes Äquivalent, wirklich verfügbar?

- Change Control: Verpflichtet sich der Lieferant, Material- oder Chemiewechsel bei Füllung und Beschichtung vorab zu melden?

DFM-Unterstützung

- Pre-CAM-Review: Wird ein DFM-Report angeboten, der VIP-Lagen gezielt auf Ätzfallen und Verstöße beim Annular Ring prüft?

- Bohrdaten-Handling: Gibt es einen belastbaren Ablauf, um VIP-Bohrungen aus kombinierten Daten von Standardbohrungen zu trennen oder zu zusammenzuführen?

Auswahlkriterien und Entscheidungsregeln

Diese Regeln helfen dabei, Kosten, Zuverlässigkeit und Packungsdichte sauber gegeneinander abzuwägen.

- Wenn der BGA-Pitch < 0,5 mm ist: Wählen Sie VIPPO. Standard-Dog-Bone-Routing ist dann rechnerisch kaum noch möglich oder zu kurzschlusskritisch.

- Wenn der BGA-Pitch ≥ 0,8 mm ist: Wählen Sie Standard Tented Vias. VIP verursacht dann meist nur unnötige Mehrkosten von etwa 20 %.

- Wenn ausschließlich Wärmeabfuhr zählt: Wählen Sie VIP mit leitfähiger Füllung nur in seltenen Sonderfällen oder setzen Sie dichte Arrays normaler Thermal-Vias ein, falls genug Platz vorhanden ist. Hinweis: Nichtleitende Füllung mit Kupferplattierung ist für die Zuverlässigkeit meist besser als leitfähige Füllung.

- Wenn die Leiterplatte hochfrequent ist: Wählen Sie VIP, um Signalstubs zu minimieren, prüfen Sie aber die Dielektrizitätskonstante des Füllmaterials.

- Wenn Kosten der Haupttreiber sind: Überarbeiten Sie das BGA-Fanout so, dass VIP möglichst vermieden wird, etwa durch weniger Lagen oder eine größere Platine.

- Wenn Zuverlässigkeit der Klasse 3 Priorität hat: Spezifizieren Sie nichtleitende Füllung + Deckschicht. Leitfähige Füllung sollte wegen des CTE-Risikos vermieden werden.

- Wenn die Aspect Ratio > 10:1 ist: Überarbeiten Sie den Stackup. Oberhalb dieses Werts sinkt die VIP-Ausbeute deutlich.

- Wenn die Lieferzeit sehr knapp ist (< 5 Tage): Vermeiden Sie VIP. Aushärten und Planarisierung sind physische Engpässe, die sich nicht ohne Risiko beschleunigen lassen.

- Wenn das Bauteil ein QFN mit Zentralpad ist: Setzen Sie VIP im Zentralpad ein, damit kein Lot in offene Vias abfließt und die thermische Anbindung verschlechtert.

- Wenn Prototypen "Dimpling" zeigen: Ziehen Sie die Spezifikation auf < 15 µm an und verlangen Sie eine Überprüfung des Planarisierungsprozesses für die Serie.

FAQ

F: Wie stark erhöht Via-in-Pad-Fertigung die Leiterplattenkosten? A: Typischerweise um 15 bis 25 % gegenüber einer Standard-Leiterplatte. Darin enthalten sind zusätzliche Schritte wie separate VIP-Bohrungen, Vakuumfüllung, Aushärtung, Planarisierung und ein zweiter Beschichtungszyklus zum Capping.

F: Sollte ich leitfähige oder nichtleitfähige Füllung verwenden? A: Für 95 % der Anwendungen ist nichtleitende Füllung aus Epoxid die bessere Wahl. Sie passt thermisch besser zum Laminat und reduziert Barrel Cracks. Leitfähige Füllung bringt meist nur einen sehr geringen thermischen Zusatznutzen, da die Wärme überwiegend über die Kupfermetallisierung transportiert wird.

F: Welcher Mindestpitch ist mit VIP realistisch? A: VIP unterstützt BGA-Pitches bis hinunter zu 0,35 mm oder 0,4 mm. In diesem Bereich sinkt der Bohrdurchmesser typischerweise auf 0,15 mm (6 mil) oder 0,125 mm (5 mil), was fortschrittliches Laser- oder Mikrobohren erfordert.

F: Warum brauche ich separate Bohrdateien für VIP? A: Das verhindert Fertigungsfehler. Werden VIP-Bohrungen mit Standardbohrungen vermischt, kann der Hersteller versehentlich offene Löcher füllen oder VIPs unbefüllt lassen, was bei der Montage zu Lotverlust führt.

F: Kann ich VIP nur auf einer Leiterplattenseite einsetzen? A: Ja, das Design kann VIPs nur auf einer Seite enthalten. Der Fertigungsprozess läuft aber in der Regel panelweit, weil Füll- und Beschichtungsschritte global für die gesamte Struktur abgearbeitet werden.

F: Was passiert, wenn die Dimple-Tiefe zu groß ist? A: Lötpaste kann in der Vertiefung hängen bleiben, oder die BGA-Kugel kontaktiert die Pad-Schultern nicht sauber. Das führt zu Hohlstellen in der Lötverbindung oder zu offenen Kontakten wie Head-in-Pillow-Defekten.

F: Wie wirkt sich VIP auf die Signalintegrität aus? A: Im Regelfall positiv. Weil das Via direkt im Pad sitzt, entfällt der Stub zwischen Pad und Via. Dadurch sinken Induktivität und Kapazität, was für Hochgeschwindigkeitssignale besonders wichtig ist.

F: Was ist der Unterschied zwischen tented Vias und VIP? A: Tented Vias sind nur mit Lötstoppmaske abgedeckt, also weder gefüllt noch überplattiert. VIPs sind mit festem Epoxid gefüllt und anschließend mit Kupfer überplattiert. Tented Vias sind nicht lötbar, VIPs dagegen schon.

Angebot / DFM-Review für Via-in-Pad-Fertigung anfragen (was Sie mitsenden sollten)

Damit ein Angebot belastbar und das DFM-Review aussagekräftig wird, sollte Ihr RFQ-Paket Folgendes enthalten:

- Gerber-Daten (RS-274X) oder ODB++: ODB++ ist vorzuziehen, weil Via-Typen darin intelligenter unterscheidbar sind.

- Separate Bohrdatei: Eindeutig markiert für gefüllte Vias, zum Beispiel

VIP_Drill.drl. - Fertigungszeichnung / Readme:

- Geben Sie ausdrücklich an: "IPC-4761 Type VII (Filled and Capped)."

- Definieren Sie die Füllart: "Non-conductive epoxy."

- Definieren Sie das Abnahmekriterium: "Dimple depth < 0.025 mm."

- Stackup-Diagramm: Zeigen Sie, welche Lagen die VIPs verbinden, besonders bei Blind- oder Buried-Strukturen.

- Menge: Prototyp, z. B. 10 Stück, oder Serienfertigung, z. B. 1000 Stück.

- Lieferzeitanforderung: Weisen Sie darauf hin, dass VIP gegenüber Standardfertigung etwa 2 bis 4 Tage zusätzlich benötigt.

- IPC-Klasse: Klasse 2 oder Klasse 3.

- Bestückungsdaten (optional, aber empfohlen): Centroid-Datei und BOM, wenn der Hersteller zusätzlich die Kompatibilität des BGA-Footprints prüfen soll.

Glossar

| Begriff | Definition |

|---|---|

| VIPPO | Via-in-Pad Plated Over. Der übliche Fachbegriff für ein mit Kupfer gefülltes und überplattiertes Via. |

| Aspect Ratio | Verhältnis von Leiterplattendicke zu Bohrlochdurchmesser. Entscheidend für die Metallisierbarkeit. |

| Dimple | Vertiefung oder konkave Oberfläche an der Oberseite eines gefüllten Vias. Für eine sichere Montage muss sie minimiert werden. |

| Planarisierung | Mechanischer oder chemischer Prozess zum Nivellieren der Leiterplattenoberfläche nach dem Füllen und vor dem Überplattieren. |

| Wrap Plating | Kupferplattierung, die |

Fazit

via in pad manufacturing gelingt am zuverlässigsten, wenn Spezifikationen und Verifikationsplan früh definiert und anschließend über DFM sowie geeignete Tests abgesichert werden.

Nutzen Sie die oben beschriebenen Regeln, Kontrollpunkte und Fehlermuster, um Iterationsschleifen zu verkürzen und die Ausbeute auch bei steigenden Stückzahlen zu schützen.

Wenn eine Randbedingung unklar ist, validieren Sie sie zuerst mit einem kleinen Pilotlos, bevor Sie die Serienfreigabe fixieren.