Wichtige Erkenntnisse

Bevor wir uns in die technischen Tiefen von Quanten-Interconnects begeben, sind hier die wesentlichen Punkte, die Ingenieurteams verstehen müssen.

- Material ist entscheidend: Standard-Golddraht ist aufgrund des Restwiderstands oft ungeeignet für supraleitende Qubits; Aluminium (1 % Silizium) ist der Standard für kryogene Umgebungen.

- Induktivität ist parasitär: Die Länge und Schleifenhöhe der Drahtbondverbindung erhöhen direkt die Induktivität, was die Qubit-Frequenz verstimmen kann.

- Kritikalität der Oberflächenbeschaffenheit: Magnetische Materialien (wie Standard-Nickel in ENIG) zerstören die Qubit-Kohärenz; nicht-magnetische Oberflächen wie ENEPIG oder Weichgold sind zwingend erforderlich.

- Mechanische Belastung: Die Schnittstelle muss wiederholte thermische Zyklen von Raumtemperatur (300 K) bis in den Milli-Kelvin (mK)-Bereich ohne Ablösung überstehen.

- Frequenzgang: Die Drahtbondverbindung wirkt als Diskontinuität in der Übertragungsleitung; kurze Bonds minimieren die Impedanzfehlanpassung.

- Validierung: Durchgangsprüfungen bei Raumtemperatur sind unzureichend; Gleichstrom-Widerstandsverhältnisse (RRR) und kryogene Zugtests sind oft erforderlich.

Was und der Montageprozess (Drahtbonden) für die Qubit-Schnittstelle wirklich bedeutet (Umfang & Grenzen)

Das Verständnis der Kernanforderungen an das Drahtbonden für die Qubit-Schnittstelle beginnt mit der Erkenntnis, dass die Standard-IPC-Klasse-3-Zuverlässigkeit für Quantenanwendungen nicht ausreicht. In der traditionellen Elektronik verbindet das Drahtbonden einen Siliziumchip mit einem Leadframe oder einer Leiterplatte, um Strom- und Logiksignale zu übertragen. Im Quantenbereich dient das Drahtbonden für die Qubit-Schnittstelle einem doppelten Zweck: Es stellt die elektrische Konnektivität her, während der empfindliche Quantenzustand (Kohärenz) des Qubits aufrechterhalten wird. Diese Schnittstelle arbeitet in einem Regime, in dem einzelne Photonen eine Rolle spielen und thermisches Rauschen praktisch nicht existieren darf.

Der Umfang dieses Prozesses unterscheidet sich in dreifacher Hinsicht von der Standardmontage:

- Thermisches Regime: Die Bondverbindung muss bei Temperaturen nahe dem absoluten Nullpunkt (10 mK bis 4 K) mechanische Integrität bewahren.

- Elektromagnetische Umgebung: Die Drahtschleife selbst wird zu einem strahlenden Element. Wenn sie nicht kontrolliert wird, wirkt sie als Antenne, die Rauschen aufnimmt oder Energie abstrahlt, was zu Dekohärenz führt.

- Supraleitung: Bei supraleitenden Qubits muss die Drahtbondverbindung selbst oft supraleitend werden, um Energieableitung (Erwärmung) am Verbindungspunkt zu verhindern.

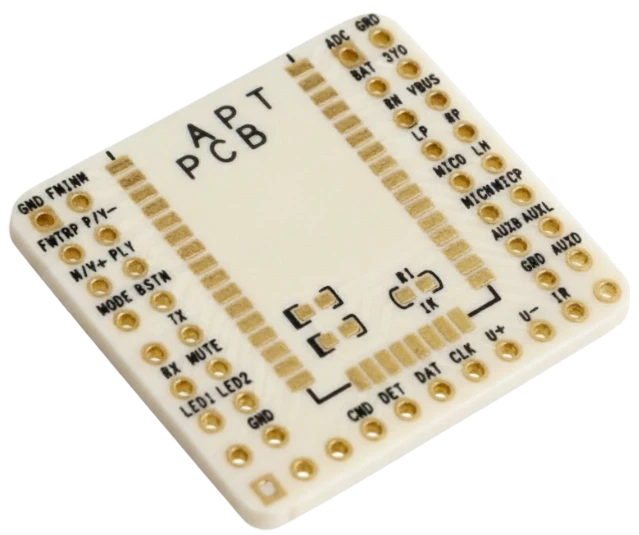

APTPCB (APTPCB PCB Factory) rät Kunden oft, dass das Substratdesign (Leiterplatte) und der Montageprozess (Drahtbonden) in Quantenanwendungen nicht getrennt behandelt werden können. Die Pad-Geometrie auf der Leiterplatte bestimmt die Bondform, die wiederum die Induktivität bestimmt.

Metriken für das und der Montageprozess (Drahtbonden) von Qubit-Schnittstellen, die wichtig sind (wie man Qualität bewertet)

Sobald der Umfang definiert ist, müssen Ingenieure den Erfolg anhand spezifischer Metriken quantifizieren, die über die standardmäßigen Zugfestigkeiten hinausgehen. Die folgende Tabelle skizziert die kritischen Leistungsindikatoren für eine hochwertige Quantenschnittstelle.

| Metrik | Warum es wichtig ist | Typischer Bereich / Faktor | Wie zu messen |

|---|---|---|---|

| Parasitäre Induktivität | Hohe Induktivität verändert die Resonanzfrequenz des Qubits und begrenzt die Bandbreite. | 0,5 nH bis 2,0 nH (geometrieabhängig) | VNA (Vektor-Netzwerkanalysator) oder TDR-Simulation. |

| Scherfestigkeit der Bondverbindung | Gewährleistet mechanische Zuverlässigkeit während thermischer Kontraktion/Expansion. | > 5 Gramm (abhängig vom Drahtdurchmesser) | Dage Bondtester (Scherprüfung). |

| Kritischer Strom (Ic) | Der maximale Strom, den die Verbindung ohne Bruch der Supraleitung führen kann. | > 10 mA (anwendungsspezifisch) | 4-Punkt-Sondenmessung bei kryogenen Temperaturen. |

| Impedanzfehlanpassung | Reflexionen an der Bond-Schnittstelle verursachen Signalverlust und stehende Wellen. | Ziel 50 Ohm (VSWR < 1,2) | TDR (Zeitbereichsreflektometrie). |

| Restwiderstandsverhältnis (RRR) | Zeigt die Reinheit des Metalls und seine Leistung bei niedrigen Temperaturen an. | > 10 für Al-Drähte | Verhältnis des Widerstands bei 300K zu 4K. |

| Konsistenz der Schleifenhöhe | Höhenschwankungen ändern die Induktivität und verursachen eine Streuung der Qubit-Frequenz. | ± 10 µm Toleranz | Optische Profilometrie / 3D AOI. |

Wie man und der Montageprozess (Drahtbonden)Auswahlhilfe nach Szenario (Kompromisse)

Nachdem die Metriken festgelegt wurden, besteht der nächste Schritt darin, die richtige Bondstrategie basierend auf Ihrer spezifischen Quantenarchitektur auszuwählen. Verschiedene Qubit-Modalitäten (supraleitend, Spin, gefangenes Ion) stellen unterschiedliche Anforderungen an den Drahtbondprozess.

Szenario 1: Supraleitende Transmon-Qubits

- Anforderung: Widerstandsloser Pfad und minimales magnetisches Rauschen.

- Empfehlung: Aluminium-Keilbonden.

- Kompromiss: Aluminiumdrähte sind schwieriger auf bestimmten Goldoberflächen zu bonden als Golddrähte. Sie müssen sicherstellen, dass die Leiterplattenoberflächenveredelung kompatibel ist (z. B. dickes Weichgold oder Aluminiumpads). Ultraschall-Keilbonden wird gegenüber thermosonischem Ballbonden bevorzugt, um eine Erwärmung der empfindlichen Josephson-Kontakte zu vermeiden.

Szenario 2: Spin-Qubits in Silizium

- Anforderung: Hochdichte Gate-Leitungen, weniger empfindlich gegenüber magnetischem Rauschen als Transmons, aber begrenzter Platz.

- Empfehlung: Gold-Ballbonden (wenn eine nicht-magnetische Barriere verwendet wird).

- Kompromiss: Gold ist einfacher zu bonden und ermöglicht einen engeren Rasterabstand (Feinraster). Gold ist jedoch kein Supraleiter. Wenn die Leitungen einen erheblichen Strom führen, wird die Wärmeableitung zu einem Problem.

Szenario 3: Hochfrequenz-Steuerleitungen (4-8 GHz)

- Anforderung: Impedanzanpassung ist entscheidend, um Signalreflexionen zu verhindern.

- Empfehlung: Bandbonden.

- Kompromiss: Die Verwendung eines Flachbands anstelle eines Runddrahts reduziert die Induktivität und verbessert die Impedanzanpassung näher an 50 Ohm. Der Kompromiss besteht darin, dass das Bandbonden spezielle Keilwerkzeuge und größere Bondpads auf der Hochfrequenz-Leiterplatte erfordert.

Szenario 4: 3D-Integration / Multichip-Module

- Anforderung: Vertikale oder horizontale Verbindung mehrerer Quantenchips.

- Empfehlung: Keilbonden mit kurzen Schleifen.

- Kompromiss: Extrem kurze Schleifen minimieren die Induktivität, erhöhen aber die mechanische Spannung während thermischer Zyklen. Die CTE-Fehlanpassung (Koeffizient der thermischen Ausdehnung) zwischen dem Chip und dem Interposer muss minimal sein.

Szenario 5: Abstimmung und Frequenzanpassung

- Anforderung: Induktivitätsanpassung nach der Fertigung.

- Empfehlung: Adaptives Schleifenprofiling.

- Kompromiss: Ähnlich der präzisen Antennenabstimmung und -trimmung in der HF-Fertigung kann die Form des Drahtbonds angepasst werden, um die Induktivität zu "abzustimmen". Dies erfordert hochentwickelte Bondausrüstung, die komplexe Schleifenprofile erstellen kann, was die Herstellungskosten erhöht.

Szenario 6: Schnelle Prototypenentwicklung

- Anforderung: Schnelle Bearbeitung zum Testen von Chipdesigns.

- Empfehlung: Manuelles oder halbautomatisches Keilbonden.

- Kompromiss: Manuelles Bonden ist langsamer und weniger konsistent (höhere Induktivitätsvariation), ermöglicht aber sofortige Tests ohne komplexe Programmierung. Geeignet für Machbarkeitsstudien, nicht für die Produktion.

und der Montageprozess (Drahtbonden) für die Implementierung von Qubit-Schnittstellen: Prüfpunkte (vom Design bis zur Fertigung)

Die Wahl der richtigen Methode ist nur die halbe Miete; strenge Implementierungsprotokolle sind erforderlich, um sicherzustellen, dass die Schnittstelle den Übergang vom Design zum Verdünnungskühlschrank übersteht.

Phase 1: PCB-/Substratdesign

- Oberflächenveredelung: ENEPIG (stromloses Nickel, stromloses Palladium, Tauchgold) oder Weichgold spezifizieren. Standard-HASL oder Tauchzinn vermeiden. Sicherstellen, dass die Nickelschicht, falls verwendet, nicht magnetisch ist (hoher Phosphorgehalt) oder vollständig eliminiert wird.

- Pad-Geometrie: Pads so gestalten, dass sie den „Fuß“ der Keilbondung aufnehmen. Für das Bandbonden müssen die Pads rechteckig und am Signalpfad ausgerichtet sein.

- Erdung: Signalpads mit Massevias (Masse-Signal-Masse-Konfiguration) umgeben, um die Impedanz bis zum Bondpunkt aufrechtzuerhalten.

Phase 2: Materialbeschaffung

- Drahtreinheit: 99,999% (5N) Aluminium- oder Aluminium-1%-Siliziumdraht beschaffen. Verunreinigungen streuen Elektronen und unterbrechen die Supraleitung.

- Substratqualität: Keramik-Leiterplatten (Aluminiumoxid oder Aluminiumnitrid) verwenden, um eine bessere thermische Anpassung an Siliziumchips im Vergleich zu FR4 zu gewährleisten.

Phase 3: Vorbereitung vor dem Bonden

- Plasmareinigung: Führen Sie unmittelbar vor dem Bonden einen Argon/Sauerstoff-Plasmareinigungszyklus durch, um organische Verunreinigungen von den Pads zu entfernen. Dies ist entscheidend für die Zuverlässigkeit des Keilbondens.

- Ausheizen: Entfernen Sie Feuchtigkeit vom Substrat. Im PCB eingeschlossene Feuchtigkeit kann in der Vakuumkammer ausgasen oder während des Abkühlens gefrieren/sich ausdehnen, wodurch die Bondverbindung reißt.

Phase 4: Bondprozess

- Parameteroptimierung: Führen Sie ein DOE (Design of Experiments) für Ultraschallleistung, Zeit und Kraft durch. Das Fenster für Quantenchips ist eng – zu viel Leistung beschädigt das Qubit; zu wenig führt zu Ablösungen.

- Schleifensteuerung: Programmieren Sie den Bonder für "Low Loop"- oder "Flat Loop"-Profile, um parasitäre Induktivität zu minimieren.

Phase 5: Validierung nach dem Bonden

- Zerstörungsfreier Zugtest: Wenden Sie eine sehr geringe Kraft (z.B. 1g) an, um sicherzustellen, dass keine "falschen Bonds" existieren.

- Sichtprüfung: Überprüfen Sie auf Fersenrisse und die Genauigkeit der Bondplatzierung.

- Kryogene Qualifizierung: Entnehmen Sie stichprobenartig Einheiten für Thermoschocktests (Eintauchen in flüssigen Stickstoff), gefolgt von Durchgangsprüfungen.

und der Montageprozess (Drahtbonden) für Qubit-Schnittstellen: Häufige Fehler (und der richtige Ansatz)

Selbst erfahrene Ingenieure stoßen auf Fallstricke, wenn sie von klassischen zu Quanten-Interconnects wechseln.

Fehler 1: Verwendung magnetischer Unterschichten

- Der Fehler: Verwendung von Standard-ENIG (Electroless Nickel Immersion Gold), bei dem die Nickelschicht magnetisch ist.

- Die Folge: Das Magnetfeld des Nickels stört den Spinzustand oder Fluss des Qubits und reduziert die Kohärenzzeit.

- Die Lösung: Nicht-magnetisches Nickel-Phosphor spezifizieren oder eine direkte Gold-auf-Kupfer- oder Silberbeschichtung verwenden.

Fehler 2: Ignorieren der CTE-Fehlanpassung

- Der Fehler: Bonden eines Siliziumchips direkt auf eine Standard-FR4-Platine mit kurzen, engen Drähten.

- Die Folge: Beim Abkühlen auf 10 mK schrumpft FR4 viel stärker als Silizium. Die Spannung lässt die Drähte reißen.

- Die Lösung: Einen CTE-angepassten Interposer verwenden oder eine „Serviceschleife“ (Spielraum) im Draht lassen, obwohl dies die Induktivität beeinträchtigt.

Fehler 3: Übermäßiges Bonden (Zu viel Kraft/Leistung)

- Der Fehler: Anwenden hoher Ultraschallenergie, um einen starken Halt zu gewährleisten.

- Die Folge: Dies kann zu Kraterbildung (Mikrorissen) im darunterliegenden Substrat oder zur Beschädigung der empfindlichen Josephson-Kontakte auf dem Chip führen.

- Die Lösung: Die minimale Energie verwenden, die für eine zuverlässige Verbindung erforderlich ist. Zuerst mit Scherversuchen an Dummy-Proben validieren.

Fehler 4: Lange Drahtschleifen

- Der Fehler: Zulassen großer, bogenförmiger Schleifen für eine einfachere Bond-Freigängigkeit.

- Die Folge: Erhöht die Induktivität erheblich ($L \approx 1 \text{nH/mm}$). Dies wirkt als Tiefpassfilter und erzeugt Impedanzdiskontinuitäten.

- Die Lösung: Die Bonds so kurz und flach wie möglich halten. Die Chip-Kavität oder PCB-Ablage auf die gleiche Höhe wie die Chip-Oberfläche platzieren (bündige Montage).

Fehler 5: Vernachlässigung der Oxidbeseitigung auf Aluminium

- Der Fehler: Bonden an Aluminium-Pads, die ohne ordnungsgemäße Reinigung oxidiert sind.

- Die Konsequenz: Kontakte mit hohem Widerstand oder nicht haftende Bonds.

- Die Lösung: Aggressive Plasmareinigung oder mechanisches Schrubben (Teil des Keilbond-Vorgangs) ist erforderlich, um die Oxidschicht zu durchbrechen.

Fehler 6: Annahme, dass Tests bei Raumtemperatur der Kryo-Leistung entsprechen

- Der Fehler: Eine Einheit wird allein aufgrund von Durchgangsprüfungen bei 300K als bestanden erklärt.

- Die Konsequenz: Bonds können beim Abkühlen mechanisch versagen ("offener" Stromkreis) oder einen nichtlinearen Widerstand aufweisen.

- Die Lösung: Führen Sie "Kaltbad"-Tests an Stichproben durch.

und der Montageprozess (Drahtbonden) für Qubit-Schnittstellen FAQ (Kosten, Lieferzeit, Materialien, Tests, Abnahmekriterien)

F: Wie beeinflusst das Drahtbonden für die Qubit-Schnittstelle die Kosten der Leiterplattenbestückung? A: Es erhöht die Kosten aufgrund des Bedarfs an spezialisierten Materialien (hochreiner Al-Draht), spezialisierten Substraten (Keramik oder Rogers) und des geringeren Durchsatzes des Präzisions-Keilbondens im Vergleich zum Hochgeschwindigkeits-Kugelbonden. Zusätzlich sind die NRE (Non-Recurring Engineering) für die Einrichtung von Schleifenprofilen höher.

F: Was ist die typische Lieferzeit für Substrate, die für das Quanten-Drahtbonden geeignet sind? A: Standard-FR4 ist schnell, aber Substrate in Quantenqualität wie Aluminiumoxid oder Hochfrequenzlaminate haben oft Lieferzeiten von 3–5 Wochen. APTPCB bietet beschleunigte Dienstleistungen für NPI-Montage an, um diese Frist zu verkürzen. F: Können wir Kupferdraht anstelle von Aluminium für eine bessere Leitfähigkeit verwenden? A: Im Allgemeinen nein. Kupfer oxidiert schnell und ist härter, was höhere Bondkräfte erfordert, die den Chip beschädigen können. Darüber hinaus wird Aluminium bei 1,2 K supraleitend, was es zu einem perfekten widerstandslosen Leiter für Quantenschaltungen macht, während Kupfer dies nicht tut.

F: Was sind die Akzeptanzkriterien für eine Quanten-Drahtbondverbindung? A: Zu den Kriterien gehören typischerweise:

- Scherfestigkeit > X Gramm (basierend auf dem Drahtdurchmesser).

- Platzierungsgenauigkeit innerhalb von ±10 µm.

- Schleifenhöhenvariation < 5 µm.

- Keine Fersenrisse bei 100-facher Vergrößerung sichtbar.

- Gleichstromwiderstand < 0,5 Ohm (bei Raumtemperatur).

F: Wie testen Sie Drahtbondverbindungen, ohne das Qubit zu zerstören? A: Wir verwenden „Witness-Coupons“ oder Dummy-Chips, die mit denselben Parametern gebondet wurden, für zerstörende Tests (Zug-/Scherprüfung). Die eigentlichen Quantenchips werden einer 100%igen Sichtprüfung (AOI) und, falls das Design es zulässt, Niederstrom-Durchgangsprüfungen unterzogen.

F: Warum wird „Antennenabstimmung und -trimmen“ im Zusammenhang mit Drahtbonden erwähnt? A: Obwohl es sich primär um einen HF-Begriff handelt, trifft das Konzept hier zu. Die Drahtschleife wirkt als Induktor. Durch präzises Anpassen der Schleifenform (Trimmen der Länge/Höhe) können Ingenieure die Impedanz der Verbindung „abstimmen“, um sie an die Übertragungsleitung anzupassen und so Signalverluste zu minimieren.

F: Übernimmt APTPCB das Drahtbonden oder nur die Leiterplattenfertigung? A: APTPCB bietet schlüsselfertige Lösungen. Wir fertigen das Hochleistungssubstrat und können den PCBA-Prozess verwalten, einschließlich spezieller Bondinganforderungen durch unsere fortschrittlichen Montagepartner.

Ressourcen für und der Montageprozess (Drahtbonden) für Qubit-Schnittstellen (verwandte Seiten und Tools)

Um Ihren Designprozess weiter zu unterstützen, nutzen Sie die folgenden auf unserer Plattform verfügbaren Ressourcen.

- Substratauswahl: Entdecken Sie Keramik-Leiterplatten-Fähigkeiten für kryogene Stabilität.

- Signalintegrität: Nutzen Sie unseren Impedanzrechner, um Ihre Leiterbahnen zu entwerfen, bevor sie das Drahtbond-Pad erreichen.

- Oberflächenveredelungen: Lesen Sie über Leiterplatten-Oberflächenveredelungen, um die richtige nicht-magnetische Option zu wählen.

- Montagedienstleistungen: Erfahren Sie mehr über unsere schlüsselfertige Montage für komplexe Projekte mit hoher Variantenvielfalt.

Glossar und der Montageprozess (Drahtbonden) für Qubit-Schnittstellen (Schlüsselbegriffe)

| Begriff | Definition |

|---|---|

| Wedge-Bonden | Eine Bondtechnik, die Ultraschallenergie und Druck verwendet, um Drähte anzubringen; bevorzugt für feine Raster und Aluminiumdrähte. |

| Ball-Bonden | Eine Technik, die eine Kugel an der Drahtspitze bildet; normalerweise schneller, erfordert aber Wärme (thermosonisch) und verwendet typischerweise Gold. |

| Supraleitung | Ein Zustand, in dem ein Material (wie Aluminium bei <1,2 K) keinen elektrischen Widerstand aufweist. |

| Qubit (Quantenbit) | Die Basiseinheit der Quanteninformation; sehr empfindlich gegenüber Rauschen und Wärme. |

| Induktivität (parasitär) | Unerwünschte Induktivität, die durch die Drahtschleife hinzugefügt wird und die Signalfrequenz und -qualität beeinflusst. |

| Kryogen | Bezieht sich auf extrem niedrige Temperaturen (typischerweise unter 100K, bis in den mK-Bereich). |

| WAK (Wärmeausdehnungskoeffizient) | Die Rate, mit der sich ein Material bei Temperaturänderungen ausdehnt/zusammenzieht. Eine Fehlanpassung führt zu Bondversagen. |

| ENEPIG | Chemisch Nickel, chemisch Palladium, Tauchgold; eine universelle Oberflächenveredelung, die gut für das Drahtbonden geeignet ist. |

| Skin-Effekt | Die Tendenz von Hochfrequenzstrom, nahe der Oberfläche des Leiters zu fließen; relevant für Mikrowellen-Steuerleitungen. |

| Josephson-Kontakt | Eine Schlüsselkomponente supraleitender Qubits; extrem empfindlich gegenüber elektrostatischer Entladung und Wärme. |

| Interposer | Eine Zwischenschicht (Silizium oder Keramik), die verwendet wird, um Signale zwischen dem Chip und der Hauptplatine zu leiten. |

| Fersenriss | Ein Bruch an der Stelle, an der der Draht vom Bondpad zur Schleife übergeht; ein häufiger Fehlermodus. |

Fazit: und der Montageprozess (Drahtbonden) für Qubit-Schnittstellen – nächste Schritte

Die Beherrschung des Drahtbondens für Qubit-Schnittstellen bedeutet, die Schnittstelle von mechanischer Robustheit, kryogener Physik und Mikrowellentechnik zu managen. Es erfordert eine Abkehr von standardmäßigen "nur-Kontinuität"-Denkweisen und die Annahme eines rigorosen Ansatzes für Materialreinheit, Schleifengeometrie und Oberflächenbeschaffenheit. Wenn Sie bereit sind, Ihren Quantenprozessor oder Ihre Steuerungselektronik vom Design zur Fertigung zu überführen, stellen Sie sicher, dass Ihr Fertigungspartner diese einzigartigen Einschränkungen versteht.

Wenn Sie ein Angebot von APTPCB anfordern, geben Sie bitte Folgendes an:

- Gerber-Dateien: Mit klaren Angaben zu den Positionen der Bondpads.

- Lagenaufbau-Details: Einschließlich spezifischer dielektrischer Materialien (z.B. Rogers, Keramik).

- Spezifikationen der Oberflächenveredelung: Geben Sie explizit "Nicht-magnetisch" an, falls erforderlich.

- Drahtbond-Diagramm: Mit Angabe der Zieldrahtschleifenhöhen und des Drahtmaterials (Al vs. Au).

- Betriebstemperatur: (z.B. 4K, 10mK), damit wir Sie bezüglich CTE-Risiken beraten können.

Zuverlässige Quantenhardware beginnt mit einer zuverlässigen Schnittstelle. Kontaktieren Sie uns noch heute, um Ihr Design auf Herstellbarkeit zu überprüfen.