Inhalt

- Highlights

- Was ist ein 5G Small Cell PCB? (Umfang & Grenzen)

- Wichtige Kennzahlen (Wie man sie bewertet)

- Wie man wählt (Material- & Designauswahl)

- Implementierungs-Prüfpunkte (vom Design bis zur Fertigung)

- Häufige Fehler (und wie man sie vermeidet)

- Checkliste zur Lieferantenqualifizierung: Wie Sie Ihre Fabrik überprüfen

- Glossar

- 6 wesentliche Regeln für 5G Small Cell PCBs (Spickzettel)

- FAQ

- Fordern Sie ein Angebot / DFM-Review für 5G Small Cell PCBs an

- Fazit

Die Bereitstellung von 5G-Netzwerken hat das Infrastrukturparadigma von massiven, weit verteilten Türmen (Macro Cells) hin zu dichten, kompakten Einheiten, den sogenannten Small Cells (Kleinzellen), verschoben. Für PCB-Ingenieure und Beschaffungsmanager stellt diese Verschiebung ein einzigartiges Paradoxon dar: Die Hardware muss kleiner und billiger sein, um in großen Mengen eingesetzt werden zu können, muss aber gleichzeitig deutlich höhere Frequenzen (mmWave) und thermische Lasten als je zuvor bewältigen. Eine 5G Small Cell PCB ist nicht einfach nur eine verkleinerte Basisstations-Platine; sie ist eine hochpräzise Verbindungsplattform, die Signalintegrität, Wärmemanagement und Umgebungsbeständigkeit in Einklang bringt.

Bei APTPCB sehen wir, wie Small-Cell-Designs die Grenzen der hybriden Fertigung ausreizen – durch die Kombination von FR4 mit Hochfrequenz-Laminaten, um eine kostengünstige Leistung zu erzielen. Dieser Leitfaden dient als Ihr definitives technisches Handbuch, das über grundlegende Definitionen hinausgeht und sich mit spezifischen Materialauswahlen, Stackup-Strategien und Fertigungsprüfpunkten befasst, die für die Einführung eines erfolgreichen 5G-Small-Cell-Produkts erforderlich sind.

Highlights

- Die Hierarchie: Den Unterschied zwischen den PCB-Anforderungen für Femto-, Pico- und Micro-Zellen verstehen.

- Materialstrategie: Wie man hybride Stackups (FR4 + Rogers/Taconic) verwendet, um Kosten zu senken, ohne das Signal zu zerstören.

- Wärmemanagement: Lösungen für Hochleistungs-PAs (Leistungsverstärker) in kompakten, lüfterlosen Gehäusen.

- Kritische Fertigungsaspekte: Verwaltung von Lagenregistrierung und Durchkontaktierung (Plating) in HDI-Strukturen.

- Qualitätskontrolle: Warum PIM-Tests (Passive Intermodulation) der neue Standard für die Abnahme sind.

- Kostentreiber: Identifizieren, wo Sie überspezifizieren und wo Sie es sich nicht leisten können, Abstriche zu machen.

Was ist ein 5G Small Cell PCB? (Umfang & Grenzen)

Ein 5G Small Cell PCB ist die Kernplatine, die in drahtlosen Zugangspunkten (Access Points) mit geringer Leistung und kurzer Reichweite zu finden ist und zur Verdichtung der Netzabdeckung verwendet wird. Im Gegensatz zu Macro Cells, die kilometerweite Gebiete abdecken, decken Small Cells Bereiche in Metern ab (10 m bis 2 km). Diese PCBs verarbeiten Hochgeschwindigkeitsdaten und RF-Signale und integrieren das Antennenarray (Active Antenna Unit oder AAU) oft direkt auf der Platine oder über einen Mezzanine-Steckverbinder.

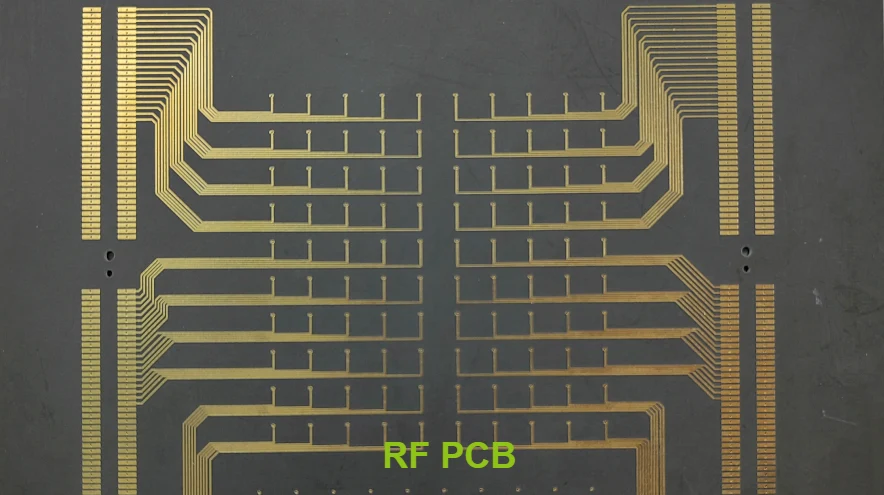

Die technische Herausforderung liegt in der Frequenz. 5G arbeitet in zwei Bereichen: Sub-6GHz (ähnlich wie 4G, aber mit größerer Bandbreite) und mmWave (24 GHz–100 GHz). Die PCB-Anforderungen für mmWave sind hinsichtlich Oberflächenrauheit, dielektrischen Verlusten und Lagenregistrierung exponentiell strenger.

Das Small-Cell-Spektrum

- Femtocell: Einsatz im Wohnbereich. Geringe Lagenzahl (4-6 Lagen), Standard-HDI, oft kostengetrieben.

- Picocell: Unternehmen/Innenbereich. Moderate Komplexität (8-12 Lagen), erfordert Hochgeschwindigkeitsmaterialien.

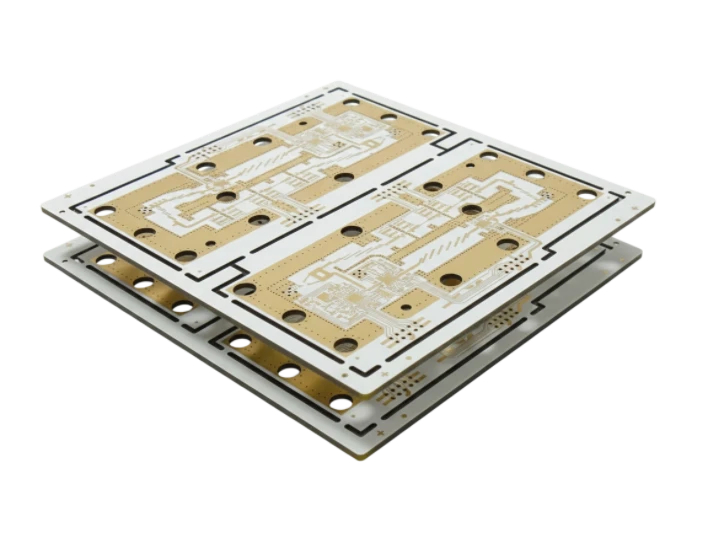

- Microcell: Außenbereich/Städtisch. Hohe Komplexität (12+ Lagen), robust, hohe thermische Anforderungen, verwendet oft Materialien für High Frequency PCB in Kombination mit dickem Kupfer.

Technische Entscheidungsmatrix

Jede Designentscheidung bei Small Cell PCBs beinhaltet einen Kompromiss zwischen Signalintegrität (SI) und Herstellbarkeit (Ertrag).

Technisches Merkmal → Auswirkung auf Käufer

| Technisches Merkmal / Entscheidung | Direkte Auswirkung (Ertrag/Zuverlässigkeit) |

|---|---|

| Hybrider Stackup (FR4 + PTFE) | Reduziert die Materialkosten um 30-40 %, erhöht jedoch die Laminierungskomplexität aufgrund unterschiedlicher CTE (Ausdehnungsraten). Risiko der Delamination, wenn es nicht richtig gehandhabt wird. |

| Eingebettete Kupfer-Münze (Embedded Copper Coin) | Bietet überlegene Wärmeableitung für Leistungsverstärker (PAs). Erhöht die Fertigungskosten und Vorlaufzeiten; erfordert präzises Routing. |

| Oberflächenfinish: ENEPIG | Hervorragend geeignet für Wire-Bonding und Löten; kein Signalverlust durch Skin-Effekt. Teurer als ENIG, aber entscheidend für hochzuverlässiges 5G. |

| Backdrilling (Stubs) | Entscheidend für die Signalintegrität >10Gbps. Reduziert die Signalreflexion, erfordert jedoch eine strenge Kontrolle der Tiefentoleranz (+/- 0,05 mm). |

Wichtige Kennzahlen (Wie man sie bewertet)

Bei der Bewertung eines Designs oder einer fertigen Leiterplatte für 5G-Anwendungen sind standardmäßige IPC-Klasse-2-Prüfungen unzureichend. Sie müssen die Kennzahlen für die RF-Leistung validieren.

| Kennzahl | Zielwert (Typisch) | Warum es für 5G wichtig ist |

|---|---|---|

| Dk (Dielektrizitätskonstante) | 3.0 – 3.5 (Stabil) | Bestimmt die Signalausbreitungsgeschwindigkeit. Variationen verursachen Phasenverschiebungen in MIMO-Antennen. |

| Df (Verlustfaktor) | < 0.002 @ 10GHz | "Verlustwinkel" (Loss Tangent). Ein hoher Df bedeutet, dass das Signal in Wärme umgewandelt wird, bevor es die Antenne erreicht. |

| PIM (Passive Intermodulation) | < -160 dBc | Kritisch zur Vermeidung von Signalinterferenzen. Verursacht durch raues Kupfer oder schlechte Lötstellen. |

| CTE (z-Achse) | < 50 ppm/°C | 5G-Chips werden heiß. Eine hohe Ausdehnung bricht durchkontaktierte Löcher (PTH). |

| Kupferrauheit | < 0.5 µm (VLP/HVLP) | Bei mmWave wandert der Strom auf der "Haut" (Skin) des Kupfers. Raues Kupfer wirkt wie ein Widerstand. |

| Wärmeleitfähigkeit | > 0.8 W/mK (Dielektrikum) | Small Cells sind oft lüfterlos; die Leiterplatte selbst muss die Wärme von den Komponenten ableiten. |

Wie man wählt (Material- & Designauswahl)

Der häufigste Fehler beim Design von 5G Small Cells ist die Verwendung teurer Hochfrequenzmaterialien für die gesamte Leiterplatte. Dies ist selten notwendig.

1. Die Hybride Stackup-Strategie

Für eine 12-lagige Small-Cell-Leiterplatte sollten die Lagen 1-2 und 11-12 (RF-Lagen) Hochleistungsmaterialien wie Rogers RO4350B, Taconic TLY oder Panasonic Megtron 6/7 verwenden. Die inneren Lagen (digitale Logik, Stromverteilung) können Standard-FR4 mit hohem Tg verwenden.

- Vorteil: Erhebliche Kostenreduzierung.

- Herausforderung: Der Hersteller muss Experte in der Verwaltung des Laminierungszyklus sein, da FR4 und PTFE bei unterschiedlichen Raten und Drücken aushärten.

2. Auswahl der Kupferfolie

Standardmäßig galvanisch abgeschiedenes (ED) Kupfer ist für 28GHz+ Signale zu rau. Sie müssen VLP (Very Low Profile) oder HVLP (Hyper Very Low Profile) Kupferfolie spezifizieren. Dies minimiert den Verlust durch den "Skin-Effekt".

3. Wärmemanagement-Design

Small Cells sind dicht gepackt. Um die Hitze zu bewältigen:

- Thermische Vias: Platzieren Sie dichte Arrays von Vias unter dem PA (Leistungsverstärker).

- Metallkern: Erwägen Sie bei extremer Hitze eine Metal Core PCB oder die Einbettung einer Kupfer-Münze direkt unter dem heißen Bauteil.

- Lötstopplack: Verwenden Sie einen dünnen, verlustarmen Lötstopplack oder entfernen Sie den Lack vollständig über RF-Übertragungsleitungen, um Signaldämpfung zu verhindern.

Implementierungs-Prüfpunkte (vom Design bis zur Fertigung)

Die Herstellung einer 5G Small Cell PCB erfordert einen synchronisierten Fahrplan. Hier sind die vier kritischen Phasen, in denen typischerweise Fehler auftreten.

Implementierungs-Fahrplan

Vom Konzept zur Produktion

Simulieren Sie vor CAM die Impedanzkontrolle. Verifizieren Sie, dass die hybride Materialkombination (z. B. Rogers + FR4) ausbalanciert ist, um ein Verziehen zu verhindern. Definieren Sie frühzeitig Blind-/Buried-Via-Strukturen.

Dies ist die Phase mit dem höchsten Risiko. Plasma-Reinigung ist zwingend erforderlich, um Harzverschmierungen von PTFE-Schichten vor dem Galvanisieren zu entfernen. Laserbohren wird für Microvias verwendet, um die Genauigkeit der Registrierung sicherzustellen.

Die Toleranz der Linienbreite muss auf +/- 10 % oder besser für die Impedanz kontrolliert werden. Tragen Sie Immersion Silver (Chemisch Silber) oder ENEPIG auf. Vermeiden Sie HASL, da die unebene Oberfläche die RF-Leistung ruiniert.

Führen Sie über den Standard-E-Test hinaus TDR (Time Domain Reflectometry) für die Impedanz durch. Führen Sie bei High-End-Einheiten PIM-Tests durch, um sicherzustellen, dass keine Signalverzerrung vorliegt.

Häufige Fehler (und wie man sie vermeidet)

1. Den "Glass Weave Effect" (Glasgewebe-Effekt) ignorieren

Wenn bei Hochgeschwindigkeits-5G-Signalen eine Leiterbahn parallel zum Glasfasergewebe des Laminats verläuft, kann es zu periodischen Impedanzänderungen (Fiber Weave Skew) kommen.

- Lösung: Verwenden Sie "Spread Glass"-Gewebe (1067, 1078) oder verlegen Sie die Leiterbahnen in einem Winkel von 10 Grad relativ zum Gewebe.

2. Schlechtes CTE-Management bei Hybridplatinen

Das Mischen von Materialien mit stark unterschiedlichen Wärmeausdehnungskoeffizienten (CTE) führt zu Delamination während des Reflow-Lötens.

- Lösung: Wählen Sie FR4-Materialien, die speziell so formuliert sind, dass sie zur Z-Achsen-Ausdehnung des Hochfrequenzlaminats passen. Konsultieren Sie die DFM-Richtlinien von APTPCB für kompatible Materialpaare.

3. Überätzen von RF-Leiterbahnen

RF-Leiterbahnen sind nach dem Ätzen oft trapezförmig und nicht perfekt rechteckig. Dies ändert die Impedanz.

- Lösung: Berücksichtigen Sie den "Ätzfaktor" (Etch Factor) in Ihrer Simulationssoftware. Stellen Sie sicher, dass Ihr Hersteller Vakuumätzen für feinere Linien verwendet.

Checkliste zur Lieferantenqualifizierung: Wie Sie Ihre Fabrik überprüfen

Nicht jeder Leiterplattenhersteller kann die Anforderungen von 5G erfüllen. Verwenden Sie diese Checkliste, um potenzielle Partner zu überprüfen.

- Erfahrung mit hybrider Laminierung: Können sie Querschliff-Fotos von früheren hybriden Aufbauten (FR4 + PTFE) vorlegen?

- PIM-Tests: Verfügen sie über interne Kapazitäten zum Testen auf passive Intermodulation?

- LDI-Fähigkeit: Verwenden sie Laser Direct Imaging? (Alte Filmbelichtungsmethoden sind für 5G-Leiterbahnabstände nicht genau genug).

- Plasma-Ätzen: Ist Plasma-Desmear (Plasma-Reinigung) Standard in ihrem Prozessablauf für PTFE-Materialien?

- Impedanztoleranz: Können sie +/- 5 % Impedanztoleranz garantieren (Standard ist +/- 10 %)?

- Materialbestand: Haben sie Rogers/Megtron auf Lager, oder müssen Sie mit 8 Wochen Vorlaufzeit für Materialien rechnen?

Glossar

PIM (Passive Intermodulation): Eine Art von Signalverzerrung, die auftritt, wenn zwei oder mehr Signale in einem nichtlinearen Bauteil (wie einem rostigen Stecker oder einer rauen PCB-Leiterbahn) gemischt werden, was zu Interferenzen führt.

Hybrid Stackup (Hybrider Lagenaufbau): Ein PCB-Design, das teure Hochfrequenzmaterialien nur auf kritischen Signallagen und billigeres FR4 für den Rest der Platine verwendet, um Kosten zu sparen.

Skin-Effekt: Die Tendenz von hochfrequentem Wechselstrom (AC), nahe der Oberfläche des Leiters zu fließen. Dies macht die Kupferoberflächenrauheit zu einem kritischen Faktor bei 5G-Leiterplatten.

MIMO (Multiple Input Multiple Output): Eine Antennentechnologie, die in 5G verwendet wird, bei der mehrere Antennen sowohl an der Quelle als auch am Ziel verwendet werden. Die Leiterplatte muss komplexe Antennenarrays unterstützen.

Backdrilling: Der Prozess des Ausbohrens des ungenutzten Teils eines durchkontaktierten Lochs (Stub), um Signalreflexionen in Hochgeschwindigkeitsdesigns zu verhindern.

6 wesentliche Regeln für 5G Small Cell PCBs (Spickzettel)

| Goldene Regel | Warum es wichtig ist | Implementierungsschlüssel |

|---|---|---|

| 1. Hybride Stackups verwenden | Reduziert die Kosten um ~40 % im Vergleich zu reinem PTFE. | Passen Sie den CTE von FR4 an das HF-Material an. |

| 2. VLP-Kupfer spezifizieren | Reduziert die Einfügedämpfung bei mmWave. | Fordern Sie ein Rauheitsprofil < 0,5 µm an. |

| 3. HASL-Finish vermeiden | Unebene Pads ruinieren den RF-Kontakt/-Impedanz. | Verwenden Sie Immersion Silver oder ENEPIG. |

| 4. Backdrill für High-Speed-Vias | Beseitigt Signalreflexionen (Stubs). | Halten Sie die Stub-Länge < 10 mils (0,25 mm). |

| 5. Thermische Via-Arrays | Small Cells haben keine Lüfter; die Leiterplatte ist der Kühlkörper. | Füllen und verschließen Sie Vias unter PA-Komponenten. |

| 6. Frühzeitige DFM-Einbindung | Verhindert unmögliche Laminierungszyklen. | Senden Sie den Stackup vor dem Routing an die Fertigung. |

FAQ

F: Was ist der größte Kostentreiber bei 5G Small Cell PCBs?

A: Das Laminatmaterial. Hochfrequenzmaterialien (wie die Rogers RO3000/RO4000-Serie) können 5- bis 10-mal so teuer sein wie Standard-FR4. Aus diesem Grund sind hybride Stackups für die Massenproduktion unerlässlich.

F: Kann ich Standard-FR4 für 5G-Anwendungen verwenden?

A: Für Sub-6GHz-Anwendungen könnte Hochleistungs-FR4 (wie Isola I-Speed) für kurze Leiterbahnen ausreichen. Für mmWave (24GHz+) weist Standard-FR4 jedoch zu viel dielektrischen Verlust (Df) und Feuchtigkeitsaufnahme auf, was es für Signallagen unbrauchbar macht.

F: Warum wird ENEPIG als Oberflächenfinish empfohlen?

A: ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold) bietet die beste Balance. Es bietet eine flache Oberfläche für Fine-Pitch-Bauteile, hervorragende Wire-Bonding-Fähigkeit und leidet im Gegensatz zu ENIG nicht unter "Black Pad"-Problemen. Es ist äußerst zuverlässig für Außenumgebungen.

F: Wie verwalte ich die Hitze in einer versiegelten Small Cell-Einheit?

A: Da selten Lüfter verwendet werden, muss die Leiterplatte die Wärme an das Gehäuse ableiten. Verwenden Sie dickes Kupfer (2oz+), eingebettete Kupfer-Münzen oder Metal Core PCBs für den Leistungsverstärkerteil. Wärmeleitmaterialien (TIM) verbinden die Hotspots der Leiterplatte mit dem Gehäuse.

F: Wie lang ist die Vorlaufzeit für Prototypen von 5G Small Cell PCBs?

A: Die Standardvorlaufzeit beträgt 10-15 Tage. Wenn jedoch spezielle Materialien (ungewöhnliche Rogers/Taconic-Varianten) nicht auf Lager sind, können sich die Vorlaufzeiten auf 4-6 Wochen verlängern. Prüfen Sie die Materialverfügbarkeit immer in der Designphase mit APTPCB.

F: Benötige ich Blind- und Buried-Vias?

A: Höchstwahrscheinlich ja. Um die für Small Cells erforderliche Dichte zu erreichen (insbesondere mit MIMO-Antennenarrays), ist die HDI PCB-Technologie mit Blind- und Buried-Vias notwendig, um Signale zu routen, ohne die Leiterplattengröße zu erhöhen.

Fordern Sie ein Angebot / DFM-Review für 5G Small Cell PCBs an

Sind Sie bereit, Ihr 5G-Design von der Simulation in die Realität umzusetzen? Bei APTPCB sind wir auf Hochfrequenz-, Hybrid- und HDI-Fertigung spezialisiert.

Um ein genaues Angebot und eine DFM-Analyse zu erhalten, stellen Sie bitte Folgendes zur Verfügung:

- Gerber-Dateien: RS-274X oder ODB++ Format.

- Stackup-Diagramm: Klare Angabe der Materialtypen (z. B. Lage 1: Rogers 4350B, Lage 2: FR4).

- Impedanzanforderungen: Spezifische Leiterbahnbreiten und Ziel-Ohm.

- Bohrtabelle: Definition der Blind-/Buried-Via-Paare.

- Menge: Schätzungen für Prototypen im Vergleich zur Massenproduktion.

Fazit

5G Small Cell PCBs repräsentieren die Schnittmenge aus fortschrittlicher Materialwissenschaft und Präzisionsfertigung. Sie erfordern eine Abkehr vom traditionellen "FR4-Denken". Indem Sie die Nuancen von hybriden Stackups, strenger PIM-Kontrolle und Wärmemanagement verstehen, können Sie eine zuverlässige Netzwerkinfrastruktur aufbauen, die den Anforderungen der 5G-Ära standhält.

Egal, ob Sie eine Femtozelle für ein Heimbüro oder eine robuste Mikrozelle für eine städtische Straßenlaterne bauen, der Erfolg Ihres Produkts hängt von der Integrität der Leiterplatte ab. Stellen Sie sicher, dass Sie mit einem Hersteller zusammenarbeiten, der die Physik von Hochfrequenzsignalen versteht.

Entdecken Sie mehr über unsere Fähigkeiten: