Inhalt

- Kernaussagen

- Was ist eine AES/EBU-PCB?

- Wichtige Kennwerte

- Auswahl von Material und Design

- Umsetzung von Design bis Fertigung

- Typische Fehler und ihre Vermeidung

- Lieferanten-Checkliste

- Glossar

- 6 Grundregeln fuer AES/EBU-PCB

- FAQ

- Angebot / DFM-Review anfordern

- Fazit

In der professionellen Audiotechnik und im Broadcast-Bereich ist Signalintegritaet kein Bonus, sondern Grundvoraussetzung. Ein einzelnes Knacken, ein Klick oder ein durch Jitter erzeugtes Artefakt kann eine Master-Aufnahme oder einen Live-Feed ruinieren. Viel Aufmerksamkeit geht zwar an Kabel und XLR-Stecker, doch das eigentliche Fundament der digitalen Audio-Uebertragung ist die AES/EBU PCB.

Das Design und die Fertigung einer Leiterplatte fuer den AES3-Standard, der meist als AES/EBU bezeichnet wird, erfordern ein anderes Denken als klassische analoge Audio-Layouts. Es geht nicht nur darum, Punkt A mit Punkt B zu verbinden, sondern eine praezise Uebertragungsleitungsumgebung zu erhalten, damit keine Reflexionen und keine Datenverluste entstehen. Bei APTPCB sehen wir viele Projekte scheitern, nicht wegen schlechter Schaltplaene, sondern wegen schwacher Stackup-Planung und fehlender Impedanzkontrolle in der Fertigung.

Dieser Leitfaden ist als technische Referenz gedacht. Wir gehen ueber die Grunddefinition hinaus und betrachten die Fertigungsrealitaet, die Materialauswahl und die DFM-Vorgaben, die fuer fehlerfreie AES/EBU-Hardware notwendig sind.

Kernaussagen

- 110 Ω sind zwingend: Die charakteristische Impedanz ist die wichtigste Kennzahl fuer AES/EBU.

- Materialauswahl: Teures Rogers ist meist nicht noetig, konsistentes FR4 aber schon.

- Topologie und Layout: Gute Praxis bei Differentialpaaren und Terminierung reduziert Jitter.

- Fertigungspruefpunkte: Mit TDR laesst sich die Leiterplatte vor der Bestueckung pruefen.

- Fehleranalyse: Viele AES3-Probleme lassen sich schon auf Gerber-Ebene vermeiden.

Was ist eine AES/EBU-PCB?

Eine AES/EBU PCB ist eine Leiterplatte, die digitale Audiosignale gemaess dem AES3-Standard fuehrt, der von der Audio Engineering Society und der European Broadcasting Union definiert wurde. Anders als bei Analog-Audio, wo die Signalspannung den Tonverlauf repraesentiert, uebertraegt AES3 digitale Daten, also zwei PCM-Audiokanaele, ueber ein symmetrisches Leitungspaar.

Das definierende Merkmal einer AES/EBU-PCB ist die Forderung nach einer charakteristischen Impedanz von 110 Ohm.

Auch wenn der Frequenzinhalt von AES3 im Vergleich zu modernen High-Speed-Schnittstellen niedrig ist, typischerweise etwa 3 MHz bis 6 MHz und bei 192 kHz noch hoeher, ist das Signal sehr empfindlich gegenueber Impedanzfehlanpassungen. Wenn die Leiterbahnen nicht zur 110-Ω-Impedanz von Kabeln und Empfaengertransformatoren passen, wird Signalenergie zur Quelle reflektiert. Das erzeugt stehende Wellen und Jitter, also Timing-Fehler, die die Audioqualitaet verschlechtern und Stereoabbildung oder Verzerrungen beeintraechtigen.

Eine AES/EBU-PCB ist deshalb praktisch immer eine Controlled Impedance PCB. Trace Width, Spacing und Dielektrikumsabstand muessen genau berechnet werden.

Technisches Merkmal → Auswirkung fuer den Einkaeufer

| Technische Entscheidung | Direkte Auswirkung |

|---|---|

| 110Ω Impedanzkontrolle (±10 %) | Verhindert Reflexionen und haelt das digitale Eye Pattern offen, damit die Audio-Dekodierung fehlerfrei bleibt. |

| Eng gefuehrte Differentialpaare | Verbessern die Gleichtaktunterdrueckung und damit die Stoerfestigkeit in elektrisch belasteten Studio-Umgebungen. |

| Durchgehende Referenzflaechen | Reduzieren EMI und vermeiden Ground Bounce, der Jitter im Datenstrom erzeugen kann. |

| Backdrilling bei dicken Backplanes | Entfernt Via-Stubs, die wie Antennen oder Filter wirken, und sichert so die Signalintegritaet in komplexen Broadcast-Systemen. |

Wichtige Kennwerte

Bei der Bewertung einer AES/EBU-PCB oder eines gefertigten Prototyps muessen bestimmte Kennwerte geprueft werden. Anders als bei einfachen Boards reicht reine Konnektivitaet nicht aus. AES3-Platinen muessen physikalische Leitungsanforderungen erfuellen.

| Kennwert | Zielwert | Warum er wichtig ist |

|---|---|---|

| Differentielle Impedanz | 110Ω ± 10 % | Das ist der Standard. Abweichungen fuehren zu Reflexionen, Return Loss und damit zu Fehlern oder Jitter. |

| Toleranz der Leiterbahnbreite | ±10-15 % | Aetzschwankungen veraendern die Impedanz. Engere Toleranzen verlangen bessere Fertigungsfaehigkeit. |

| Dielektrizitaetskonstante | Konstant, z. B. 4,2 | Schwankungen in Kernmaterial oder Prepreg verschieben die Impedanz weg von 110Ω. |

| Intra-Pair-Skew | < 5-10 mil | Laengendifferenz zwischen Plus- und Minus-Leiterbahn. Zu hoher Skew erzeugt Gleichtaktstoerungen. |

| Return Loss | > 15 dB | Misst die Rueckreflexion des Signals. Hoeher ist besser. |

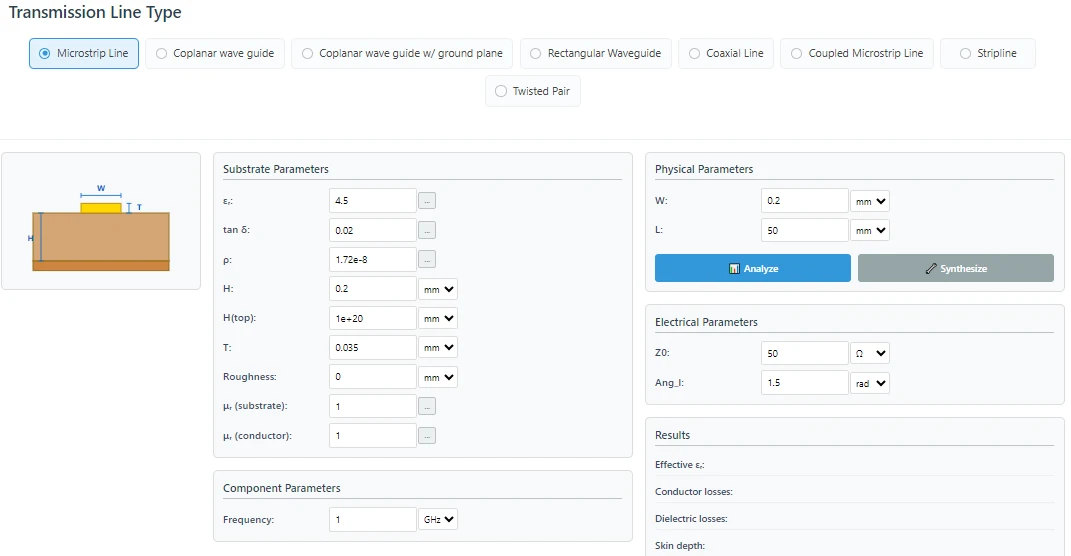

Wer unseren Impedanzrechner nutzt, sollte die exakten Stackup-Daten des Fertigers eingeben, weil theoretische Werte oft von real gepressten Prepreg-Dicken abweichen.

Auswahl von Material und Design

Der erste Schritt zu einer erfolgreichen AES/EBU-Implementierung ist die richtige Wahl von Material und Designparametern.

1. Materialwahl: FR4 oder High-Speed-Material

Ein verbreiteter Irrtum ist, dass digitales Audio exotische Materialien wie Rogers oder Teflon benoetigt.

- Realitaet: Die Grundfrequenz von AES3 liegt grob bei 3 bis 6 MHz. Standard-FR4 ist bei diesen Frequenzen fuer die Signalintegritaet voellig ausreichend. Ein High-Tg-Typ ist fuer die Montagezuverlaessigkeit sinnvoll.

- Die Einschraenkung: Wichtig ist die Konstanz des FR4. Das Laminat sollte eine stabile Dielektrizitaetskonstante und moeglichst gleichmaessiges Gewebe aufweisen. Bei sehr langen Leitungswegen oder hochdichten Broadcast-Routern kann Spread-Glass-FR4 helfen, Skew durch den Fasergewebeeffekt zu reduzieren.

- Empfehlung: Verwenden Sie normales FR4 PCB, fordern Sie aber Impedanzkontrolle in den Fertigungsnotizen. Dadurch muss der Hersteller das Stackup verifizieren.

2. Stackup-Design

Der Abstand zwischen Signallage und Referenzflaeche bestimmt die benoetigte Leiterbahnbreite fuer 110Ω.

- Duenne Dielektrika: erfordern schmalere Leiterbahnen.

- Dicke Dielektrika: erlauben breitere Leiterbahnen.

- Tipp: 110Ω ist relativ hoch. Bei Standard-1,6-mm-Boards braucht man oft etwas groesseren Abstand im Differentialpaar oder mehr Distanz zur Ground Plane. Ihr PCB Stackup sollte fertigungsgerechte Leiterbahnbreiten ermoeglichen, meist ueber 4 mil.

3. Stecker-Layout

AES/EBU wird meist ueber XLR oder BNC angeschlossen. Diese Footprints fuehren eine deutliche Impedanzdiskontinuitaet ein.

- Layout-Tipp: Halten Sie die Strecke von den Steckerpins zum Transformer oder Receiver-IC so kurz wie moeglich.

- Grounding: Chassis Ground, also die XLR-Huelle, und Signal Ground muessen sauber gefuehrt werden, sonst entstehen Ground Loops, ein klassisches Audioproblem.

Umsetzung von Design bis Fertigung

Damit Ihre AES/EBU-PCB in der Praxis funktioniert, sollten Sie diese Prozessschritte einhalten. Genau diese Pruefpunkte verwenden wir bei APTPCB waehrend unserer DFM-Reviews.

Implementierungs-Roadmap

Vom Konzept bis zur Produktion

Pruefen Sie, ob der 110Ω-Abschlusswiderstand so nah wie moeglich am Receiver-IC sitzt. Isolationstransformatoren helfen, Ground Loops zu unterbrechen.

Sprechen Sie mit dem Fertiger vor dem Routing. Bestimmen Sie die exakte Geometrie fuer 110Ω Differentialimpedanz auf dem konkreten Material.

Routen Sie AES-Signale als Differentialpaare ueber einer durchgehenden Ground Plane. Keine Split Planes kreuzen, sonst geht die Impedanzkontrolle verloren.

Fordern Sie Impedance Coupons auf den Panel-Rails an. Der Hersteller muss per TDR pruefen, dass die reale Impedanz innerhalb von ±10 % um 110Ω liegt.

Typische Fehler und ihre Vermeidung

Selbst erfahrene Entwickler machen Fehler, wenn sie von analogem auf digitales Audio-PCB-Design umsteigen.

1. Rueckstrompfad ignorieren

Der haeufigste Fehler ist das Routing des AES-Differentialpaars ueber einem Split in der Ground Plane.

- Folge: Der Rueckstrom muss einen grossen Umweg nehmen. Dadurch entstehen Induktionsschleifen, die die Impedanz ruinieren und die Leiterbahn zur EMI-Antenne machen.

- Loesung: Schnelles Digital-Audio immer ueber einer geschlossenen Referenzflaeche fuehren.

2. Leiterbahnbreiten "nach Augenmass" festlegen

Eine Standard-50Ω-Single-Ended-Breite fuer ein 110Ω-Differentialpaar funktioniert nicht.

- Folge: Starke Signalreflexion.

- Loesung: Nutzen Sie einen Feldloeser oder unseren Impedanzrechner, um die korrekte Differentialgeometrie zu berechnen.

3. Schlechte Platzierung der Steckverbinder

Wenn der AES-Receiver weit vom XLR-Stecker entfernt sitzt, entstehen unnötig lange Uebertragungswege.

- Folge: Hoehere Stoeranfaelligkeit und groessere Gefahr von Impedanzfehlern.

- Loesung: I/O-Komponenten nah an der Boardkante platzieren.

Lieferanten-Checkliste

Nicht jeder PCB-Hersteller versteht die Besonderheiten von Digital-Audio. Nutzen Sie diese Liste bei der Auswahl eines Fertigungspartners fuer AES/EBU-Projekte.

- Fuehren Sie bei jeder Charge TDR-Tests durch? (Wichtig fuer die Verifikation von 110Ω.)

- Wie hoch ist Ihre Standard-Aetztoleranz? (Fuer Impedanzkontrolle sollte sie ±10 % oder besser betragen.)

- Koennen Sie vor Produktionsstart einen kundenspezifischen Stackup-Report liefern? (Sie muessen Lagen- und Materialdicken verifizieren.)

- Unterstuetzen Sie Spread-Glass-FR4? (Nuetzlich fuer hochwertiges Profi-Audio-Equipment.)

- Wie gehen Sie mit Impedance Coupons um? (Sie sollten auf den Panel-Rails liegen.)

- Bieten Sie Cross-Section-Analysen an? (Damit lassen sich Plating-Dicke und Dielektrikumshoehe verifizieren.)

Bei APTPCB sind diese Punkte fuer High Frequency PCB und Digital-Audio-Kunden Standard.

Glossar

AES3 (AES/EBU): Standard fuer den Austausch digitaler Audiosignale zwischen professionellen Audiogeraeten. Er uebertraegt zwei Kanaele PCM-Audio.

Characteristic Impedance: Der Widerstand, den eine Uebertragungsleitung dem Stromfluss entgegensetzt. Bei AES3 muss die differentielle Impedanz 110Ω betragen.

Differential Pair: Zwei komplementaere Signale auf zwei separaten Leiterbahnen. Der Empfaenger wertet die Differenz aus und unterdrueckt Gleichtaktstoerungen.

Jitter: Zeitliche Abweichung digitaler Pulse. Im Audiobereich fuehrt das zu Verzerrung und Detailverlust.

TDR: Messverfahren zur Bestimmung der charakteristischen Impedanz einer Leiterbahn durch Pulssendung und Reflexionsmessung.

6 Grundregeln fuer AES/EBU-PCB

| Goldene Regel | Warum sie wichtig ist | Praktische Umsetzung |

|---|---|---|

| Exakt 110Ω treffen | Passt zu Kabeln und Transformern nach Standard. | Leiterbahnbreite und Abstand fuer 110Ω Differential exakt berechnen. |

| Durchgehende Masseflaeche | Erhaelt Rueckstrompfad und Impedanz. | Nie ueber Split Planes routen. |

| Stubs minimieren | Stubs erzeugen Reflexionen. | Daisy-Chain-Routing, keine T-Abzweige. |

| Enge Kopplung | Verbessert die Stoerunterdrueckung. | P- und N-Leitung nah zusammen fuehren. |

| Laengen abgleichen | Verhindert Mode Conversion. | Laengen innerhalb von 5-10 mil matchen. |

| Mit TDR verifizieren | Sichert die Fertigungsgenauigkeit ab. | In den Fab Notes "Impedance Control" angeben. |

FAQ

Q: Kann ich Standard-FR4 fuer AES/EBU-PCBs verwenden?

A: Ja. Standard-FR4 reicht fuer den AES3-Frequenzbereich grundsaetzlich aus. Entscheidend ist, dass der Hersteller enge Toleranzen bei Leiterbahnbreite und Dielektrikumsdicke halten kann, damit 110Ω eingehalten werden.

Q: Was ist der Unterschied zwischen AES/EBU- und S/PDIF-PCB-Design?

A: Das Datenprotokoll ist aehnlich, aber das elektrische Interface nicht. AES/EBU ist symmetrisch mit 110Ω und hoeheren Pegeln. S/PDIF ist unsymmetrisch mit 75Ω und niedrigeren Pegeln. Die Routing-Strategien sind daher nicht austauschbar.

Q: Wie berechne ich die Leiterbahnbreite fuer 110Ω?

A: Nicht schaetzen. Nutzen Sie einen Impedanzrechner oder einen Feldloeser. Sie brauchen Dielektrizitaetskonstante, Abstand zur Referenzflaeche, Kupferdicke und Leiterbahnabstand.

Q: Beeinflusst das Steckverbinder-Footprint die Impedanz?

A: Ja. XLR- oder Transformatorpads sind breiter als die Leiterbahnen und erzeugen eine kapazitive Diskontinuitaet. Man kann mit Referenzflaechen-Aussparungen arbeiten, das ist aber eher eine fortgeschrittene Methode.

Q: Warum versagt mein AES-Signal bei langen Kabelstrecken?

A: Wenn die PCB-Impedanz nicht 110Ω betraegt, entstehen am Stecker Reflexionen. Bei kurzen Strecken bleibt das oft unsichtbar. Bei langen Strecken verschlechtern Kabeldaempfung und Return Loss das Eye Pattern so stark, dass Unlock-Fehler auftreten.

Q: Muss ich Vias bei AES/EBU backdrillen?

A: Meist nicht. Die Frequenzen sind niedrig genug, dass normale Via-Stubs kaum Resonanzen verursachen. Bei sehr dicken Backplanes grosser Broadcast-Systeme kann Backdrilling aber sinnvoll sein.

Angebot / DFM-Review anfordern

Wenn Sie Ihr Audio-Design vom Prototyp in die Produktion bringen wollen, unterstuetzt Sie APTPCB mit Controlled-Impedance-Boards fuer den professionellen Audiobereich.

Fuer ein exaktes Angebot und ein kostenloses DFM-Review senden Sie bitte:

- Gerber Files: vorzugsweise im RS-274X-Format.

- Stackup-Anforderung: gewuenschte Lagenzahl und Gesamtdicke, etwa 4 Lagen bei 1,6 mm.

- Impedanzanforderung: klar angeben, z. B. "110Ω Differential auf Lage X".

- Materialpraeferenz: Standard-FR4 oder bestimmte Marke, falls erforderlich.

- Menge: Prototyp oder Serienvolumen.

Fazit

Das Design einer AES/EBU PCB ist eine Frage technischer Praezision. Es schlaegt die Bruecke zwischen klassischem Audio-Layout und digitalem Signalintegritaets-Design. Wenn Sie die 110Ω-Anforderung sauber einhalten, durchgehende Rueckstrompfade bewahren und mit einem Hersteller arbeiten, der TDR-Validierung beherrscht, bleibt das Audiosignal am Ausgang so sauber wie am Eingang.

Lassen Sie nicht zu, dass Ihre Leiterplatte das schwaechste Glied in der Signalkette wird. Ob Boutique-AD/DA-Wandler oder grosse Broadcast-Konsole: APTPCB bietet die passenden Fertigungskapazitaeten, um die geforderte Performance zu liefern.